GPIO口高速電路與PCB設計的關鍵技術解析

引言

在現代嵌入式系統和通信設備中,GPIO(通用輸入輸出)接口承擔著信號傳輸的核心任務。隨著系統時鐘頻率的提升(從傳統1MHz到高速GHz級別),GPIO設計已從簡單的電平轉換演變為需要精密控制的信號完整性工程。本文將從電路設計與PCB實現兩個維度,剖析不同速率等級GPIO的設計方法論。

本文引用地址:http://www.104case.com/article/202504/469453.htm

一、GPIO速率分級與設計挑戰

1. 低速GPIO(<1MHz)

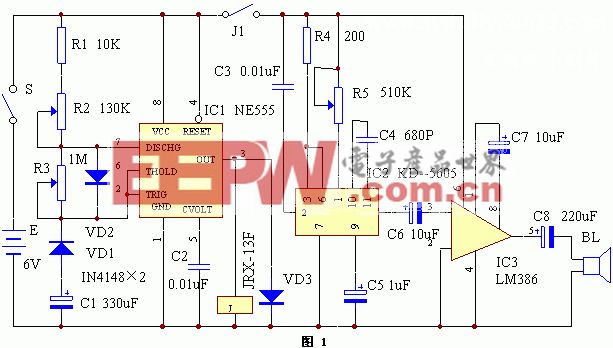

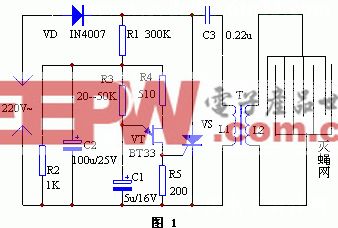

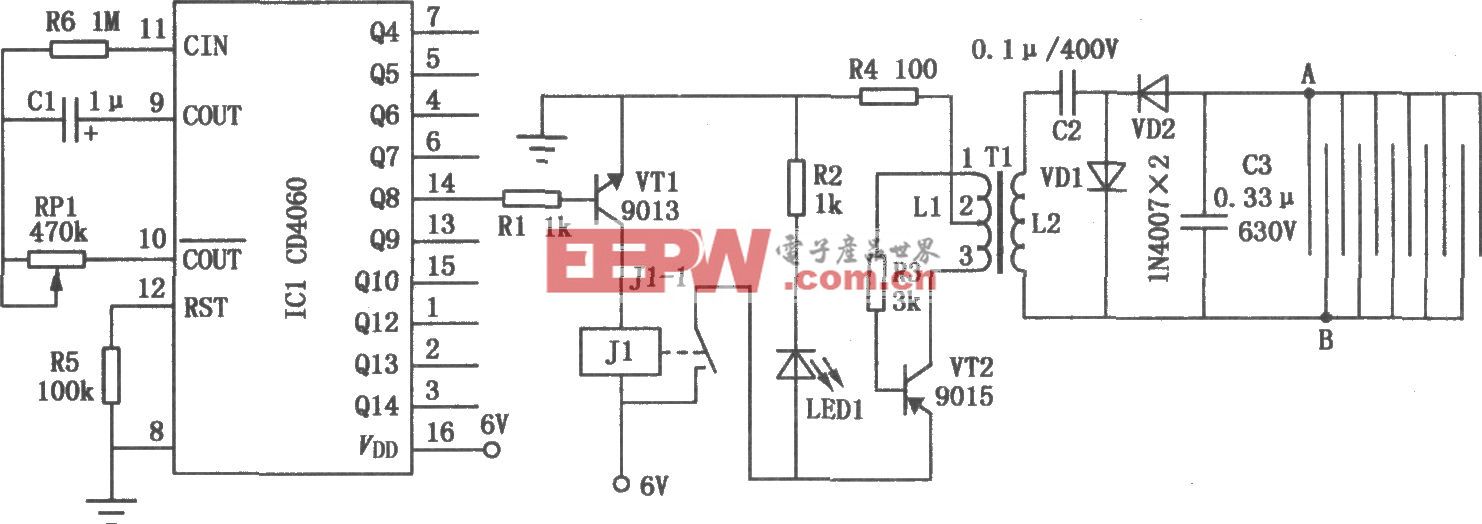

典型應用:按鍵檢測、LED控制、繼電器驅動

電路設計要點:選用常規RC濾波電路(R=1-10kΩ,C=0.1-1μF)、配置TVS二極管防止靜電放電(ESD保護電壓15kV)、驅動能力匹配:灌電流/拉電流控制在20mA以內。

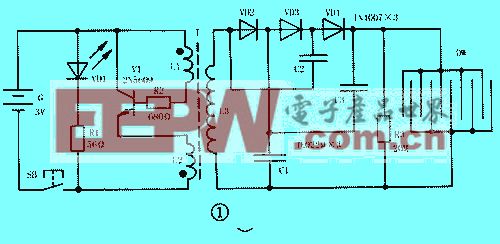

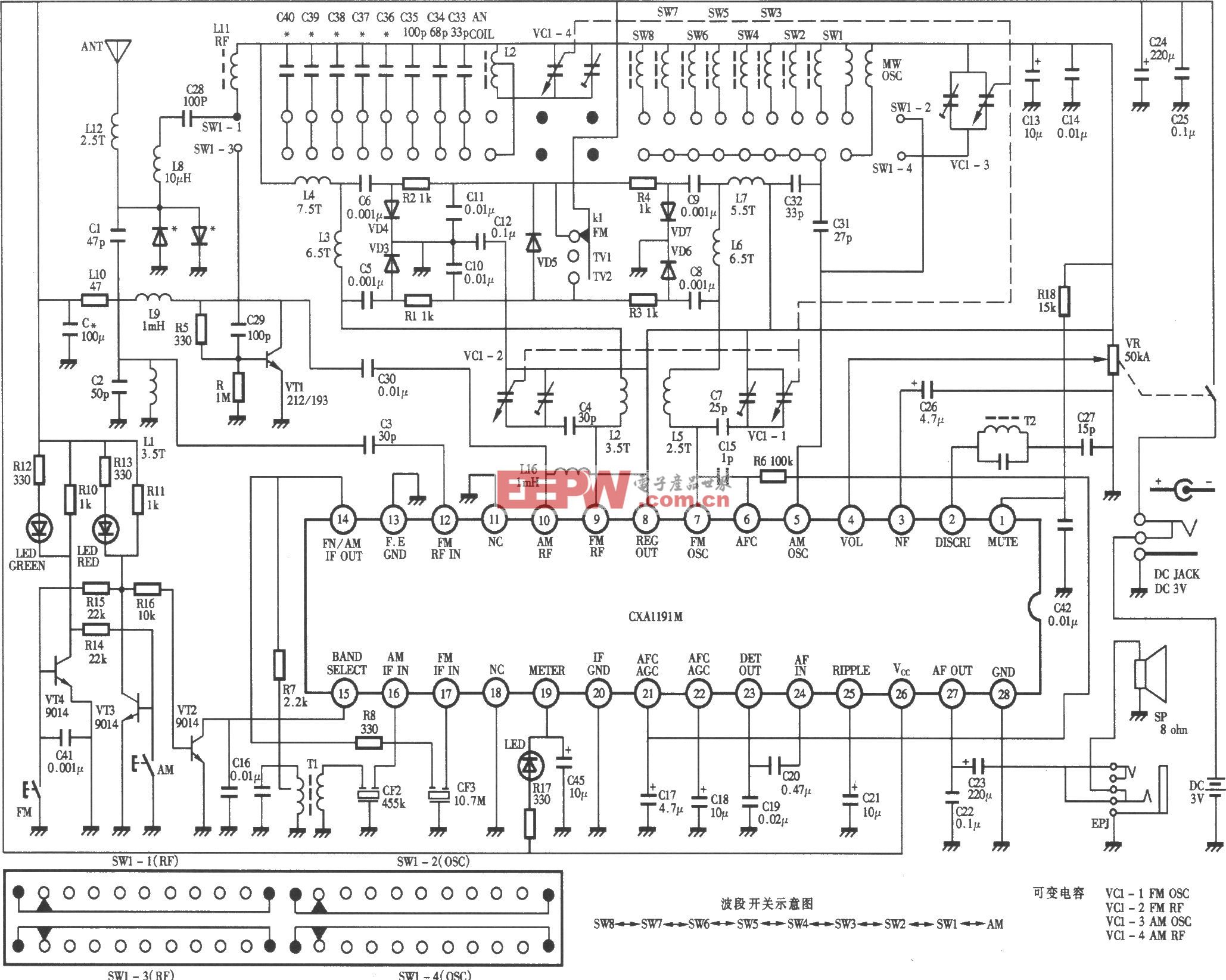

2. 中速GPIO(1MHz-50MHz)

典型應用:SPI通信、I2C總線、UART接口

信號完整性對策:源端串聯電阻匹配(22-100Ω)、采用π型濾波網絡(L=100nH,C=10pF)、建立時間/保持時間計算:需滿足t_su > 3ns,t_h > 1.5ns。

3. 高速GPIO(>50MHz)

典型應用:DDR內存接口、LVDS差分傳輸、MIPI信號

關鍵設計參數:阻抗控制精度±10%(單端50Ω,差分100Ω)、上升時間tr < 0.35/f_max(例如100MHz時tr<3.5ns)、時滯匹配要求:組內偏差<50ps,組間偏差<200ps。

二、高速PCB設計黃金法則

1. 疊層架構規劃

四層板推薦結構:

嘉立創疊層設計支持:其在線EDA平臺提供智能疊層計算器,可自動推薦符合IPC標準的疊層方案,支持混合介電常數材料組合(如FR4+高頻材料混壓),阻抗計算誤差控制在±5%以內。

2. 布線關鍵技術

3W原則:線間距≥3倍線寬(防止串擾)、長度匹配:蛇形走線補償(幅度5mm,間距2倍線寬)、過孔優化:通孔直徑0.3mm,焊盤直徑0.6mm、背鉆深度控制殘樁<10mil(0.254mm)。

嘉立創EDA設計規范優勢:設計規則檢查(DRC)模板預設高速布線約束條件,包括:自動檢測3W原則違反點、 差分對長度偏差報警閾值±5mil、過孔殘樁長度超標提示。支持一鍵生成Gerber+IPC網表,確保設計與生產數據一致性。

3. 接地策略

分割式地平面設計:數字地與模擬地單點連接(0Ω電阻或磁珠)、關鍵信號下方保留完整參考平面、地過孔間距λ/20(例如1GHz信號間距7.5mm)。

三、典型設計缺陷案例分析

案例1:阻抗突變導致信號反射:現象:某HDMI接口出現畫面閃爍,根因分析:連接器處線寬突變引起阻抗從90Ω跳變至70Ω。解決方案:采用漸變線過渡(錐度角<45°)。

案例2:跨分割地平面引發EMI:現象:無線模塊通信距離縮短,根因分析:高速GPIO線跨越電源分割間隙,解決方案:增加橋接電容(0.1μF+1nF并聯)。

結語

高速GPIO設計是電子系統性能的基石。工程師需要建立"系統級思維",從芯片選型、電路設計到PCB布局進行全鏈路優化。隨著5G和AIoT技術的發展,未來高速接口設計將面臨更嚴苛的挑戰,掌握本文所述方法論可為應對這些挑戰提供堅實基礎。

評論