PCB設(shè)計(jì)抗干擾有哪些方法?

現(xiàn)在高速高密電路中,串?dāng)_問(wèn)題越來(lái)越嚴(yán)重。對(duì)于電路的抗干擾性能設(shè)計(jì),也是很多工程師很頭痛的問(wèn)題,這也是一個(gè)非常復(fù)雜的技術(shù)問(wèn)題。對(duì)于PCB設(shè)計(jì)而言,主要做好以下幾點(diǎn),即可以在很大程度上減少信號(hào)受到的干擾。

本文引用地址:http://www.104case.com/article/202412/465402.htm1. 增大布線空間距離

設(shè)計(jì)意義:

增大信號(hào)之間的間距可以減少電磁場(chǎng)耦合,降低串?dāng)_(Crosstalk)效應(yīng)。

在高密度設(shè)計(jì)中,雖然空間有限,但關(guān)鍵信號(hào)(如時(shí)鐘線、高速總線)應(yīng)盡量?jī)?yōu)先分配較大的間距。

補(bǔ)充建議:

對(duì)于高速差分對(duì),如LVDS、USB、HDMI等,差分對(duì)之間的距離應(yīng)遠(yuǎn)大于差分對(duì)內(nèi)部的線間距(常用3W規(guī)則)。

使用布線工具中的串?dāng)_分析功能,標(biāo)記關(guān)鍵布線區(qū)域。

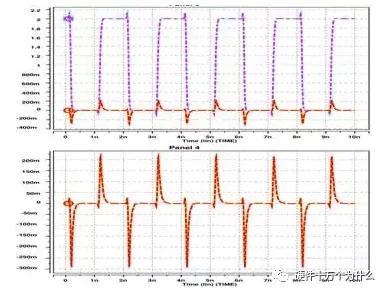

串?dāng)_是兩條信號(hào)線之間的耦合、信號(hào)線之間的互感和互容引起線上的噪聲。容性耦合引發(fā)耦合電流,而感性耦合引發(fā)耦合電壓。PCB板層的參數(shù)、信號(hào)線間距、驅(qū)動(dòng)端和接收端的電氣特性及線端接方式對(duì)串?dāng)_都有一定的影響。

串?dāng)_是信號(hào)完整性中最基本的現(xiàn)象之一,在板上走線密度很高時(shí)串?dāng)_的影響尤其嚴(yán)重。我們知道,線性無(wú)緣系統(tǒng)滿足疊加定理,如果受害線上有信號(hào)的傳輸,串?dāng)_引起的噪聲會(huì)疊加在受害線上的信號(hào),從而使其信號(hào)產(chǎn)生畸變。

串?dāng)_是由電磁耦合引起的,耦合分為容性耦合和感性耦合兩種。

根據(jù)電磁波傳播的自由空間傳播模型,信號(hào)的強(qiáng)度隨著距離的增加呈平方反比衰減。

串?dāng)_是指當(dāng)信號(hào)在傳輸線上傳播時(shí),因電磁耦合對(duì)相鄰的傳輸線產(chǎn)生的不期望

的電壓噪聲。

容性耦合是由于干擾源(Aggressor)上的電壓變化在被干擾對(duì)象(Victim)上

引起感應(yīng)電流從而導(dǎo)致的電磁干擾;

而感性耦合則是由于干擾源上的電流變化產(chǎn)生的磁場(chǎng)在被干擾對(duì)象上引起感應(yīng)電壓從而導(dǎo)致的電磁干擾。因此,信號(hào)通過(guò)一導(dǎo)體時(shí)會(huì)在相鄰的導(dǎo)體上引起兩類不同的噪聲信號(hào):容性耦合信號(hào)和感性耦合信號(hào)。

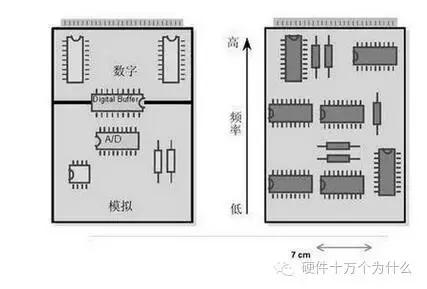

2. 數(shù)模信號(hào)分區(qū)域

設(shè)計(jì)意義:

數(shù)字信號(hào)因開(kāi)關(guān)頻率高,噪聲頻譜寬,對(duì)模擬信號(hào)容易造成干擾。

分區(qū)域設(shè)計(jì)能減少耦合干擾,改善信號(hào)完整性和電磁兼容性(EMC)。

補(bǔ)充建議:

數(shù)字區(qū)域和模擬區(qū)域在電路上應(yīng)物理隔離,并且盡量減少跨區(qū)域布線。

如果必須跨區(qū)域,則要確保跨區(qū)域的布線使用單點(diǎn)接地,避免形成地回路。

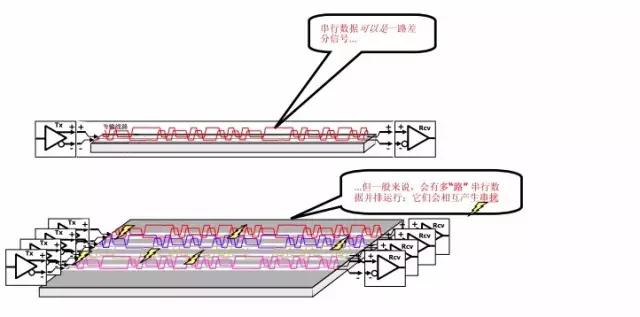

數(shù)字信號(hào)電平有較強(qiáng)的抗干擾能力,而模擬信號(hào)的抗干擾能力很差。舉個(gè)例子,3V 電平的數(shù)字信號(hào),即使接收到 0.3V 的串?dāng)_信號(hào),也可以容忍,不會(huì)對(duì)邏輯狀態(tài)產(chǎn)生影響。但在模擬信號(hào)領(lǐng)域,有些信號(hào)極微弱,例如 GSM 手機(jī)的接收靈敏度能夠做到-110dBm 的指標(biāo),僅相當(dāng)于 0.7uV 的正弦波有效值。在 LNA 前端即使接收到 uV 數(shù)量級(jí)的帶內(nèi)干擾噪聲,也足以使基站接收靈敏度大幅度劣化。這種輕微干擾可能來(lái)自數(shù)字控制信號(hào)線或電源地線上的細(xì)小的噪聲。

從系統(tǒng)的觀點(diǎn)來(lái)看,數(shù)字信號(hào)一般只在板上或框內(nèi)傳送。比如內(nèi)存總線信號(hào)、電源控制信號(hào)等,只要保證從發(fā)送端到接收端接收到的干擾不足以影響邏輯狀態(tài)的判別即可。而模擬信號(hào)需要經(jīng)過(guò)調(diào)制、變頻、放大、發(fā)射、空間傳播、接收、解調(diào)等一系列過(guò)程才能被回復(fù)。在此過(guò)程之中噪聲不斷地跌價(jià)到信號(hào)上,從系統(tǒng)的角度來(lái)講必須保證最終的信噪比滿足要求才能正確解調(diào)。最大的干擾來(lái)自空間傳播的衰減和噪聲,為了達(dá)到更好的通訊性能,必須盡可能減小板內(nèi)互連引入的串?dāng)_。

因此可以認(rèn)為,模擬信號(hào)對(duì)串?dāng)_的要求比數(shù)字信號(hào)高幾十倍,甚至有可能達(dá)到幾萬(wàn)倍。

3. 信號(hào)網(wǎng)絡(luò)不要穿過(guò)高速IO接口

設(shè)計(jì)意義:

高速接口的插拔動(dòng)作可能產(chǎn)生瞬態(tài)干擾(如ESD、電磁噪聲),容易耦合到附近的信號(hào)。

這類干擾隨機(jī)性高,難以通過(guò)濾波解決,避免布線是最直接的解決方案。

補(bǔ)充建議:

對(duì)于高速IO接口(如USB、RJ45等),可以在接口附近布置必要的保護(hù)電路,如靜電抑制二極管。

布線時(shí)保持接口周圍的保護(hù)環(huán)路完整,例如通過(guò)銅箔或包地線進(jìn)行隔離。

4. 信號(hào)網(wǎng)絡(luò)不要穿過(guò)PTH的電感、電容、晶振

設(shè)計(jì)意義:

PTH元件(插件元件)會(huì)引入非理想寄生參數(shù)(如分布電感和電容),導(dǎo)致信號(hào)質(zhì)量惡化,增加反射和噪聲耦合。

晶振等高頻元件周圍電磁場(chǎng)強(qiáng),容易干擾信號(hào)的穩(wěn)定性。

補(bǔ)充建議:

晶振附近的地面必須完整,確保無(wú)“信號(hào)穿越”現(xiàn)象,并對(duì)關(guān)鍵信號(hào)線采取避讓設(shè)計(jì)。

電容和電感盡量靠近負(fù)載放置,減少通過(guò)這些器件的回路長(zhǎng)度。

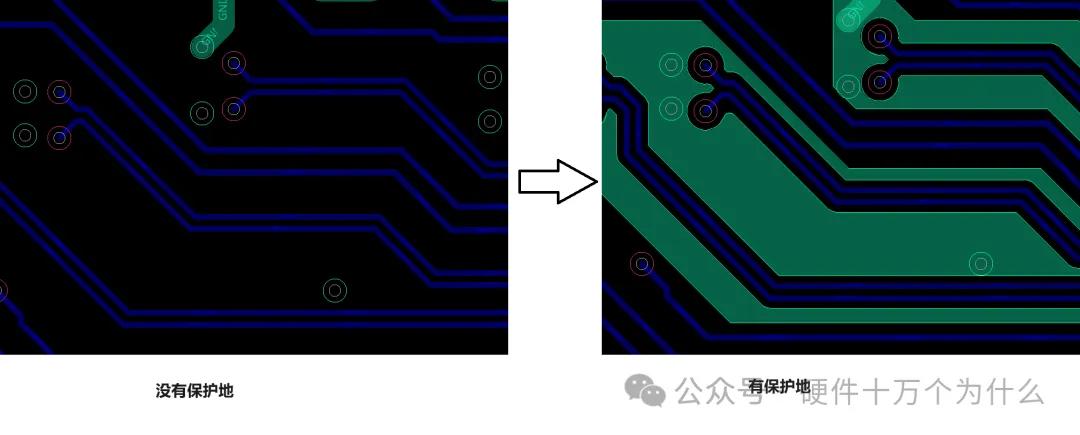

5. 包地設(shè)計(jì)

設(shè)計(jì)意義:

包地(Guard Trace)能有效減少高速信號(hào)的電磁輻射,同時(shí)抑制外界電磁干擾的耦合。

不過(guò)包地設(shè)計(jì)不當(dāng)可能導(dǎo)致信號(hào)阻抗變化,帶來(lái)反射問(wèn)題。

補(bǔ)充建議:

包地的參考地面需和系統(tǒng)的實(shí)際接地良好連接,不能孤立懸空。

包地設(shè)計(jì)可以結(jié)合差分對(duì)布線,使用等距包地,并加密地孔,保證信號(hào)穩(wěn)定。

6. 電源設(shè)計(jì)

設(shè)計(jì)意義:

電源的穩(wěn)定性直接影響整個(gè)電路系統(tǒng)的抗干擾能力。電源噪聲(Ripple/Noise)容易耦合到敏感信號(hào)上,導(dǎo)致性能退化甚至故障。

補(bǔ)充建議:

去耦電容的擺放應(yīng)靠近芯片的電源引腳,同時(shí)在多個(gè)頻段設(shè)置不同的電容值(如0.1μF、10nF、1nF)。

設(shè)計(jì)電源平面時(shí),避免與信號(hào)線交叉布線。

高功率器件的電源布線應(yīng)避免長(zhǎng)距離串聯(lián),優(yōu)先采用“星形供電”或多點(diǎn)分布方式。

7. 地平面設(shè)計(jì)

設(shè)計(jì)意義:

地平面為信號(hào)提供低阻抗的回流路徑,其完整性直接影響電路的抗干擾性能和信號(hào)質(zhì)量。

不完整的地平面會(huì)造成“地彈”效應(yīng)(Ground Bounce)和信號(hào)反射,尤其在高速電路中影響顯著。

補(bǔ)充建議:

盡量減少切割地平面,尤其是高速信號(hào)回流路徑附近。

數(shù)字地和模擬地的分割應(yīng)清晰明確,并通過(guò)單點(diǎn)連接實(shí)現(xiàn)電勢(shì)統(tǒng)一。

對(duì)于多層板設(shè)計(jì),優(yōu)先將地平面布置在靠近高速信號(hào)層的位置,以減小返回路徑的環(huán)路面積。

以上7點(diǎn)是減少干擾、提升抗干擾性能的重要指導(dǎo)原則。在實(shí)際設(shè)計(jì)中,工程師需綜合考慮信號(hào)頻率、布線密度、電源噪聲等多種因素,輔以仿真工具(如SI/PI仿真)進(jìn)行優(yōu)化,最終在板級(jí)實(shí)現(xiàn)優(yōu)良的抗干擾性能。

評(píng)論