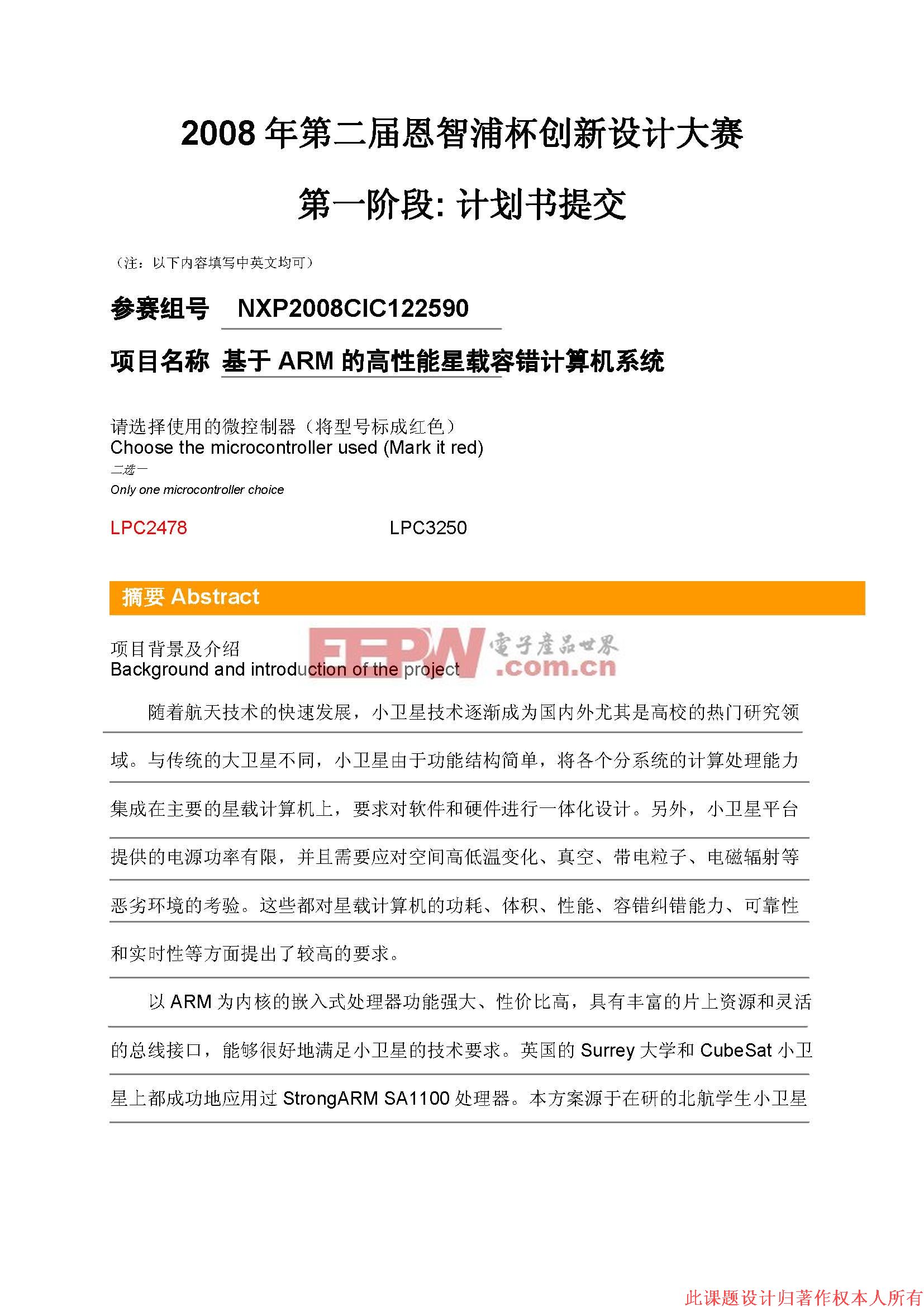

一種超低功耗、容錯的靜態隨機存儲器設計

這一分析表明基于DICE結構的SRAM存儲單元具有抗SEU特性。

2 數據讀寫電路設計

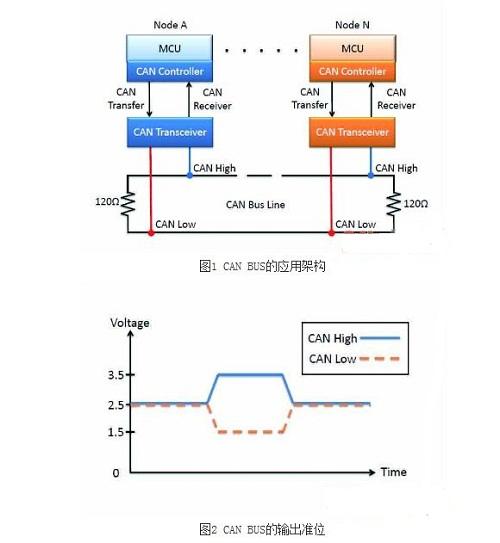

該SRAM存儲器的具體工作過程描述如下:首先從10位地址輸入端(A0~A9)口把CPU發出的地址信號傳送進來,控制信號也一并傳送進來;然后譯碼器根據所給的讀/寫地址進行譯碼,譯碼后讀/寫控制信號把相應的字線打開,由讀/寫控制信號分別控制讀/寫過程。寫操作過程,數據輸入端口把準備好的數據寫進存儲位元;讀操作過程,BL與上產生電位差,經過靈敏放大器(Sense Amplitier,SA)放大后輸出,從而實現從存儲單元中讀出存儲值,通過數據輸出端口,把存儲在位元中的數據讀出。

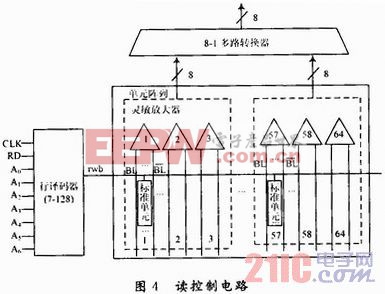

2.1 讀控制時序電路

讀操作分為兩個階段:等化階段和靈敏階段。在等化階段中,靈敏放大器將驅動兩條互補位線(BL和)上的電壓在同一水平上,這是為了實現更高的數據讀出速度。如果兩個位線上的電壓差與所需的位線電壓差相反,那么存儲單元將需要花更多的時間來驅動位線,以獲得足夠的電壓差。等化階段結束的同時,讀字線也將打開,開始讀取數據。完整的控制電路如圖4所示。

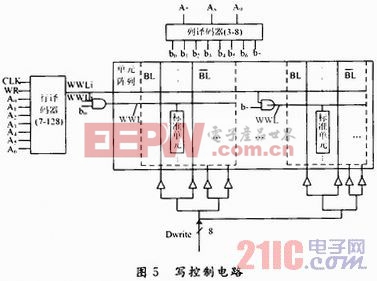

2.2 寫控制時序電路

相對于讀控制時序電路,寫控制電路簡單得多,因為它只需要接收輸入的數據到相應的BL和上。完整的寫控制電路如圖5所示。

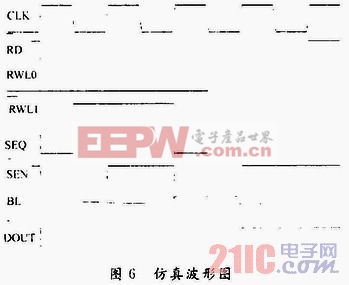

3 仿真結果

本文提出的SRAM存儲單元為基于DICE結構的16T單元,采用TSMC 90 nm CMOS工藝,利用Cadence進行仿真,數據讀操作的波形如圖6所示,其中,CLK為時鐘信號,RD為數據讀信號(低電平有效),RWL為讀字線,BL和分別是位線和反位線,DOUT為存儲單元的讀出數據。首先將數據“0”和“1”分別寫入兩個不同地址的存儲單元里,當RD有效,SEN信號為高電平時,BL和上的數據通過靈敏放大器放大,最后再將數據DOUT讀出。

評論