實(shí)驗(yàn)22 4位串行累加器

實(shí)驗(yàn)?zāi)康?/h2>實(shí)驗(yàn)任務(wù)

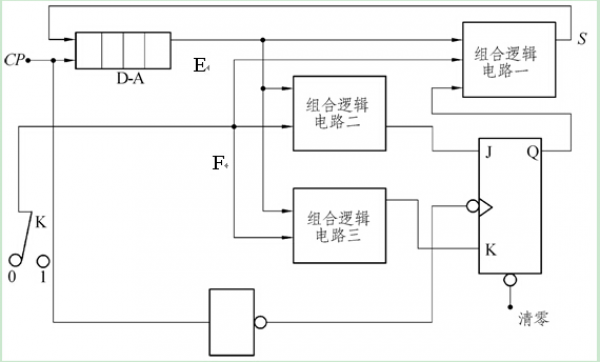

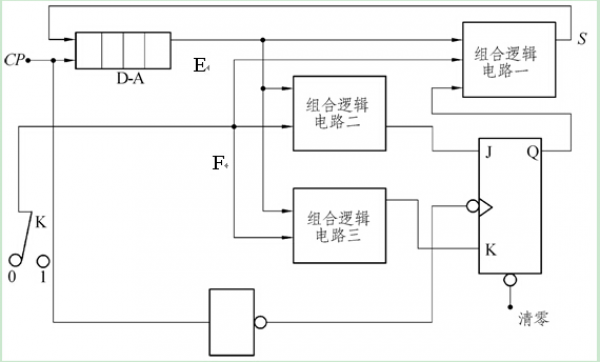

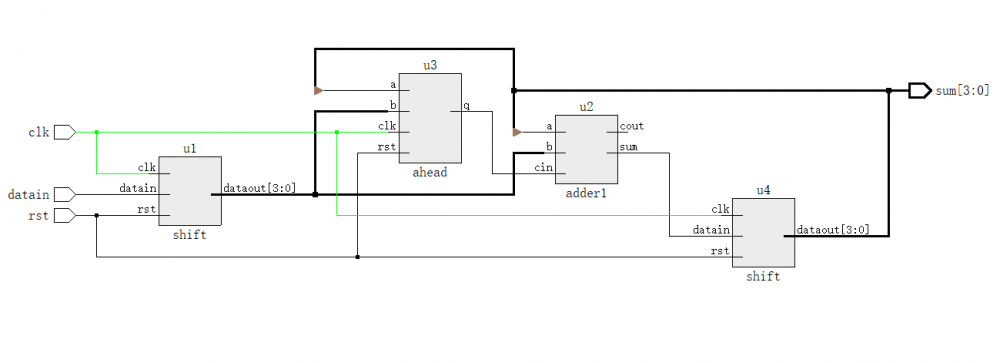

設(shè)計(jì)一個(gè)4位串行累加器,電路原理框圖如圖所示,在開關(guān)K處設(shè)置串行輸入數(shù)據(jù),在CP端輸入8個(gè)脈沖,將完成一次,兩個(gè)四位串行數(shù)據(jù)的相加,結(jié)果存D-A中。

本文引用地址:http://www.104case.com/article/202310/451566.htm

實(shí)驗(yàn)原理

根據(jù)上述電路框圖,可以分割系統(tǒng)任務(wù)。

累加器是一個(gè)具有特殊功能的二進(jìn)制寄存器,可以存放計(jì)算產(chǎn)生的中間結(jié)果,省去了計(jì)算單元的讀取操作,能加快計(jì)算單元的速度。串行累加器是由移位寄存器和全加器組成的一個(gè)求和電路。

由題目給出的要求可以分析組合邏輯電路一是一個(gè)全加器電路;組合邏輯電路二和組合邏輯電路三加上JK觸發(fā)器組成了加法超前進(jìn)位電路,D-A是儲(chǔ)存結(jié)果的寄存器。

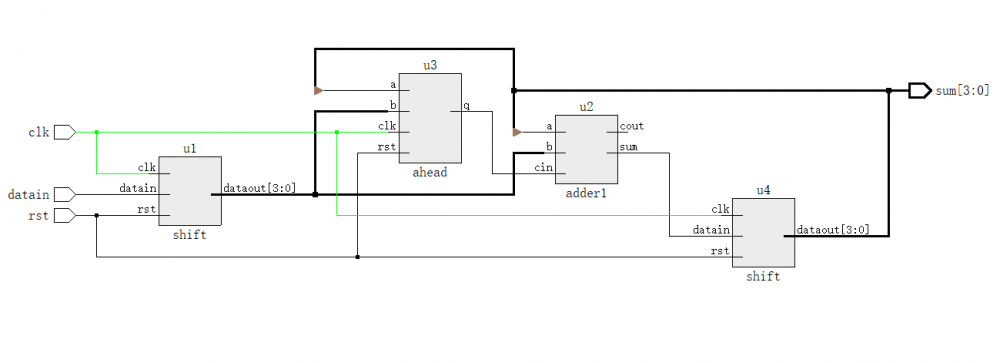

頂層模塊由4個(gè)模塊組成:

Shift U1模塊;輸入的串行寄存器,把輸入的串行數(shù)據(jù)轉(zhuǎn)換成并行數(shù)據(jù)寄存

Adder U2模塊:一位的二進(jìn)制全加器模塊,輸入的進(jìn)位信號(hào)由超前進(jìn)位邏輯產(chǎn)生

Ahead U3模塊:超前進(jìn)位邏輯,根據(jù)題目要求用JK觸發(fā)器產(chǎn)生超前進(jìn)位

Shift U4模塊:一位全加器輸出再移位輸出保存在4位寄存器中

Verilog HDL建模描述

設(shè)計(jì)文件accum4.v

module accum4

(

input wire datain, //數(shù)據(jù)輸入

input wire clk,rst, //脈沖和復(fù)位輸入信號(hào)

output wire [3:0] sum //累加結(jié)果

);

wire [3:0] adder; //寄存器1,存儲(chǔ)輸入加數(shù)內(nèi)容

wire [3:0] sumer; //寄存器2,存儲(chǔ)被加數(shù)內(nèi)容

wire cin; //全加器超前進(jìn)位信號(hào)

wire sumout; //全加器輸出

assign sum = sumer; //累加結(jié)果輸出

shift u1 //移位寄存器,把數(shù)據(jù)存入加數(shù)寄存器

(

.clk(clk),

.rst(rst),

.datain(datain),

.dataout(adder)

);

adder1 u2 //全加器,兩個(gè)寄存器的最低位相加,進(jìn)位由超前進(jìn)位邏輯輸出

(

.a(sumer[0]),

.b(adder[0]),

.cin(cin),.sum(sumout),

.cout());ahead u3 //超前進(jìn)位邏輯,產(chǎn)生進(jìn)位信號(hào)

(

.a(sumer[0]),.b(adder[0]),.clk(clk),.rst(rst),

.q(cin)

);

shift u4 //移位寄存器,將全加器結(jié)果存入被加數(shù)寄存器

(

.clk(clk),

.rst(rst),

.datain(sumout),

.dataout(sumer)

);

endmodule

頂層文件里面例化了shift.v、adder1.v、ahead.v等模塊,其中全加器和移位寄存器的源碼文件在前面章節(jié)有介紹

我們看看超前進(jìn)位邏輯的源碼ahead.v

// Description : 超前進(jìn)位邏輯產(chǎn)生

// JK觸發(fā)器:Qi+1=J!Qi+!KQi

// 全加器進(jìn)位:Ci+1=AiBi+(Ai+Bi)Ci=AiBi!Ci+!(Ai+Bi)Ci

// 推導(dǎo)得出:J=AiBi,K=!(Ai+Bi)

//********************************************************

module ahead

(

input wire a,b,clk,rst,

output wire q

);

wire j,k;jk_ff u1 //例化JK觸發(fā)器

(

.clk(clk),.j(j),.k(k),.rst(rst),.set(),

.q(q),.qb()

);

assign j = a&b; //根據(jù)推導(dǎo)得到J,K與加法器輸入信號(hào)邏輯關(guān)系

assign k = ~(a|b);

endmodule

仿真文件accum4_tb.v

`timescale 1ns/100ps //仿真時(shí)間單位/時(shí)間精度

module accum4_tb();

reg clk,rst,datain;

reg [7:0] data;

wire [3:0]sum; //初始化過程塊

initial

begin

clk = 0;

rst = 0;

data <= 8'b00100001; //串行輸入數(shù)據(jù)初值

#25

rst = 1;

end

always #10 clk = ~clk;

always @(posedge clk) //產(chǎn)生串行輸入數(shù)據(jù)

datain

if(!rst)

begin

datain <= 0;

end

else

begin

data <={0,data[7:1]};

datain <= data[0];

end

//module調(diào)用例化格式

accum4 u1

(

.clk (clk),

.rst (rst),

.datain (datain),

.sum (sum)

);

endmodule實(shí)驗(yàn)步驟

仿真結(jié)果和實(shí)驗(yàn)現(xiàn)象

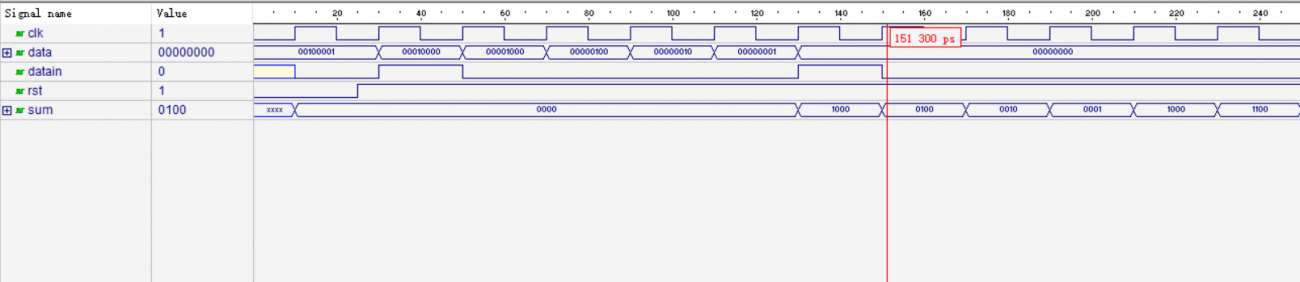

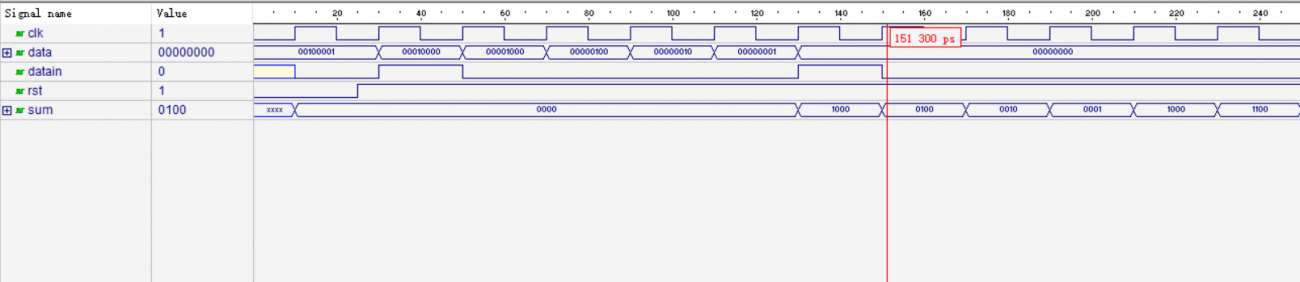

仿真結(jié)果如下圖所示:

仿真文件的串行輸入數(shù)據(jù)也是靠串行轉(zhuǎn)并行移位寄存器輸入,所以累加器計(jì)算的時(shí)鐘要順延8個(gè)clock得到結(jié)果。可以修改仿真文件中的串行輸入數(shù)據(jù)初值驗(yàn)證累加器結(jié)果。

設(shè)計(jì)一個(gè)4位串行累加器,電路原理框圖如圖所示,在開關(guān)K處設(shè)置串行輸入數(shù)據(jù),在CP端輸入8個(gè)脈沖,將完成一次,兩個(gè)四位串行數(shù)據(jù)的相加,結(jié)果存D-A中。

根據(jù)上述電路框圖,可以分割系統(tǒng)任務(wù)。

累加器是一個(gè)具有特殊功能的二進(jìn)制寄存器,可以存放計(jì)算產(chǎn)生的中間結(jié)果,省去了計(jì)算單元的讀取操作,能加快計(jì)算單元的速度。串行累加器是由移位寄存器和全加器組成的一個(gè)求和電路。

由題目給出的要求可以分析組合邏輯電路一是一個(gè)全加器電路;組合邏輯電路二和組合邏輯電路三加上JK觸發(fā)器組成了加法超前進(jìn)位電路,D-A是儲(chǔ)存結(jié)果的寄存器。

頂層模塊由4個(gè)模塊組成:

Shift U1模塊;輸入的串行寄存器,把輸入的串行數(shù)據(jù)轉(zhuǎn)換成并行數(shù)據(jù)寄存

Adder U2模塊:一位的二進(jìn)制全加器模塊,輸入的進(jìn)位信號(hào)由超前進(jìn)位邏輯產(chǎn)生

Ahead U3模塊:超前進(jìn)位邏輯,根據(jù)題目要求用JK觸發(fā)器產(chǎn)生超前進(jìn)位

Shift U4模塊:一位全加器輸出再移位輸出保存在4位寄存器中

設(shè)計(jì)文件accum4.v

module accum4 ( input wire datain, //數(shù)據(jù)輸入 input wire clk,rst, //脈沖和復(fù)位輸入信號(hào) output wire [3:0] sum //累加結(jié)果 ); wire [3:0] adder; //寄存器1,存儲(chǔ)輸入加數(shù)內(nèi)容 wire [3:0] sumer; //寄存器2,存儲(chǔ)被加數(shù)內(nèi)容 wire cin; //全加器超前進(jìn)位信號(hào) wire sumout; //全加器輸出 assign sum = sumer; //累加結(jié)果輸出 shift u1 //移位寄存器,把數(shù)據(jù)存入加數(shù)寄存器 ( .clk(clk), .rst(rst), .datain(datain), .dataout(adder) ); adder1 u2 //全加器,兩個(gè)寄存器的最低位相加,進(jìn)位由超前進(jìn)位邏輯輸出 ( .a(sumer[0]), .b(adder[0]), .cin(cin),.sum(sumout), .cout());ahead u3 //超前進(jìn)位邏輯,產(chǎn)生進(jìn)位信號(hào) ( .a(sumer[0]),.b(adder[0]),.clk(clk),.rst(rst), .q(cin) ); shift u4 //移位寄存器,將全加器結(jié)果存入被加數(shù)寄存器 ( .clk(clk), .rst(rst), .datain(sumout), .dataout(sumer) ); endmodule

頂層文件里面例化了shift.v、adder1.v、ahead.v等模塊,其中全加器和移位寄存器的源碼文件在前面章節(jié)有介紹

我們看看超前進(jìn)位邏輯的源碼ahead.v

// Description : 超前進(jìn)位邏輯產(chǎn)生 // JK觸發(fā)器:Qi+1=J!Qi+!KQi // 全加器進(jìn)位:Ci+1=AiBi+(Ai+Bi)Ci=AiBi!Ci+!(Ai+Bi)Ci // 推導(dǎo)得出:J=AiBi,K=!(Ai+Bi) //******************************************************** module ahead ( input wire a,b,clk,rst, output wire q ); wire j,k;jk_ff u1 //例化JK觸發(fā)器 ( .clk(clk),.j(j),.k(k),.rst(rst),.set(), .q(q),.qb() ); assign j = a&b; //根據(jù)推導(dǎo)得到J,K與加法器輸入信號(hào)邏輯關(guān)系 assign k = ~(a|b); endmodule

仿真文件accum4_tb.v

`timescale 1ns/100ps //仿真時(shí)間單位/時(shí)間精度

module accum4_tb();

reg clk,rst,datain;

reg [7:0] data;

wire [3:0]sum; //初始化過程塊

initial

begin

clk = 0;

rst = 0;

data <= 8'b00100001; //串行輸入數(shù)據(jù)初值

#25

rst = 1;

end

always #10 clk = ~clk;

always @(posedge clk) //產(chǎn)生串行輸入數(shù)據(jù)

datain

if(!rst)

begin

datain <= 0;

end

else

begin

data <={0,data[7:1]};

datain <= data[0];

end

//module調(diào)用例化格式

accum4 u1

(

.clk (clk),

.rst (rst),

.datain (datain),

.sum (sum)

);

endmodule仿真結(jié)果如下圖所示:

仿真文件的串行輸入數(shù)據(jù)也是靠串行轉(zhuǎn)并行移位寄存器輸入,所以累加器計(jì)算的時(shí)鐘要順延8個(gè)clock得到結(jié)果。可以修改仿真文件中的串行輸入數(shù)據(jù)初值驗(yàn)證累加器結(jié)果。

評論