時鐘抖動的影響

抖動和相位噪聲是晶振的非常重要指標,本文主要從抖動和相位噪聲定義及原理出發,闡述其在不同場景下對數字系統、高速串行接口、數據轉換器和射頻系統的影響。

本文引用地址:http://www.104case.com/article/202303/444743.htm1. 抖動和相位噪聲

1.1. 抖動

1.1.1. 抖動定義和分類

ITU-T G.701對抖動的定義為:“抖動是指數字信號在短期內相對于理想位置發生的偏移重大影響的短時變化”。

對于真實物理世界中的時鐘源,比如晶振、DLL、PLL,它們的時鐘輸出周期都不可能是一個單點的固定值,而是隨時間而變化的。即使是同一個時鐘,此刻時鐘周期的邊沿與它下一個時鐘周期的邊沿都是會發生變化的。

圖1 抖動的圖示

抖動分確定性抖動(Deterministic jitter,DJ)和隨機性抖動(Random jitter,RJ)兩種。DJ通常幅度有限,以單位時間表示,可粗略地分為周期性抖動(PJ)、有界不相關抖動BUJ和數據相關的抖動DDJ;RJ為高斯分布,以RMS均方根值表示。

圖2 抖動分類

1.1.2. 隨機抖動

隨機抖動是在任何周期中都是無法預測的,只能預測其統計特性。最常用于隨機抖動測量的是正態分布的標準差,也叫RMS抖動。

隨機抖動來自真正的隨機行為,器件的內部熱噪聲、閃爍噪聲、晶體的隨機振動、宇宙射線等都可能引起隨機抖動,這些來源很難消除。

1.1.3. 確定性抖動

確定性抖動是遵循已知模式的抖動,非高斯分布,通常是有邊際的,它是可重復可預測的。確定性抖動的峰值可以直接測量,并且測量的結果是絕對的。

(1)周期性抖動PJ

周期性抖動測量主要是針對時鐘信號,它測量實時時鐘的每一個周期,然后對實際時鐘周期進行數據統計,最后根據概率統計給出該時鐘周期大小的分布規律,此測量將顯示信號的整體質量。可能的抖動源有:電源的EMI干擾與擴頻時鐘SSC的調制信號。

(2)有界不相關抖動BUJ

主要由電源或相鄰信道的串擾等引起的,可以是周期的(Periodic),也可以是非周期的(non-periodic)。其來源通常有3種:電源噪聲、串擾和外部噪聲。

(3)數據相關抖動DDJ

DDJ分為ISI和DCD兩種。

符號間干擾ISI是由于信道帶寬受限,相鄰的碼元沖擊效應疊加產生。

DCD 值是相對于50%的理想占空比偏差,一般分兩種情況:

①信號的上升沿和下降沿的斜率不同;

②信號DC平均值發生變化而導致波形的判決門限高或者低于判決閾值;

表1 確定性抖動和隨機抖動的比較

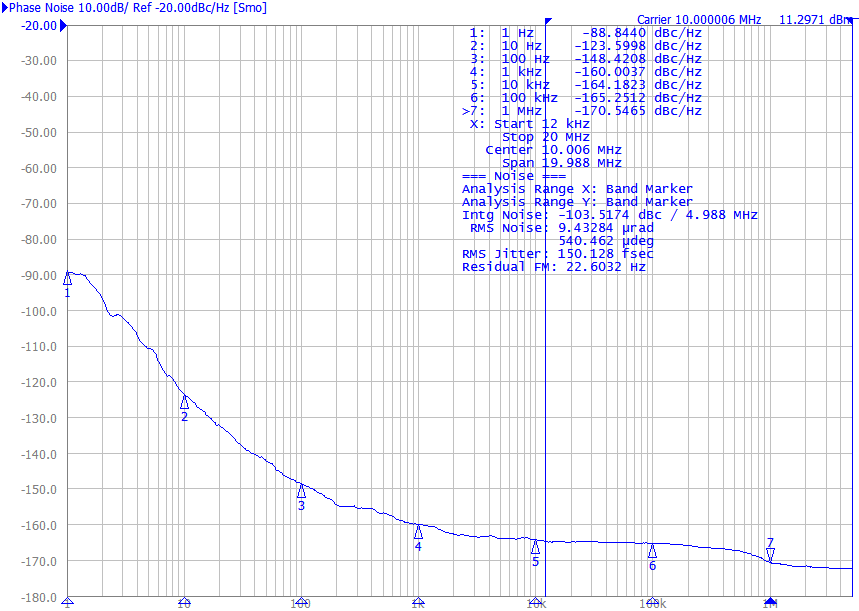

1.2. 相位噪聲和抖動轉換

相位噪聲是時鐘頻域上的表現,抖動是時鐘時域上的體現,相位噪聲可以通過數學變換轉換成抖動。

1.2.1. 相位噪聲定義

理想正弦波信號V(t)=Asin(2*pi*fc*t),其頻譜就是一條以fc為中心的直線。現實世界中的正弦波信號有不穩定性,從而產生了邊帶,其頻譜是一條類似裙子的逐漸衰落曲線。

圖3 理想的正弦波信號頻譜

圖4 現實世界中的正弦波信號頻譜

相位噪聲(Phase Noise)是抖動在頻域上的表現,通常定義為在某一頻率偏移f0處1Hz寬帶內的單邊噪聲信號積分功率和信號功率比值,單位是dBc/Hz,通常表示為dBc/Hz@ f0,數學表示如下:

圖5 相位噪聲定義圖示

晶振相位噪聲的來源主要有三方面:

①晶體品質因數Q值,主要影響1Hz~1KHz近端相位噪聲;

②晶體外圍電路,包括電源、振蕩電路、驅動線路等,主要影響1KHz~10MHz的相位噪聲;

③信號輸出的白噪聲,主要影響10M~20M遠端相位噪聲。

1.2.2. 相位噪聲轉換成抖動

抖動是信號的時域表現,相位噪聲呈現出的是信號的頻域特性。這兩者本質上是一樣的,只是表述方式不同而已,下圖6給出從相位噪聲轉換成抖動的示意。

圖6 相位噪聲積分圖示

L(f)以功率譜密度函數的形式給出了邊帶噪聲的分布,單位為dBc。單邊帶的總噪聲功率N可以由L(f)函數在整個感興趣頻段內(通常選用的積分范圍為12KHz到20MHz)積分得到。

噪聲功率N轉換成RMS抖動:

2. 抖動和相位噪聲的影響

在通信網絡、無線傳輸、CPRI和SONET等高速系統中,時鐘或振蕩器波形的時序誤差會限制一個數字I/O接口的最大速率。不僅如此,它還會導致通信鏈路的誤碼率增大,甚至限制A/D轉換器的動態范圍。下面描述時鐘抖動和相位噪聲對數字系統、高速串行接口、數據轉換器和射頻系統的影響。

2.1. 數字系統

在數字系統中時鐘邊沿決定了每個基本單元的開始和結束時間。當抖動改變了時鐘邊沿從而導致時鐘周期變化時,每個基本單元的有效工作時間也會發生變化,可能會導致信號的建立時間和保持時間不能滿足要求,從而影響電路的正常工作。

確定時鐘容差最好的方法是建立時序預算。如下圖7所示,最早達到時鐘的上升沿標志著窗口開始,最晚到達時鐘的上升沿標志著窗口的結束,兩者的時間差為窗口。為了創建時序窗口,還需要考慮加上偏斜、延時和抖動等指標(見圖8)。

隨著系統時鐘速度的提高,要求時序電路的容差更小,減小時鐘抖動有利于提高系時鐘的容差,給系統的偏斜與延時提供更多的余量。

圖7 時序窗口

圖8 時序窗口的組成

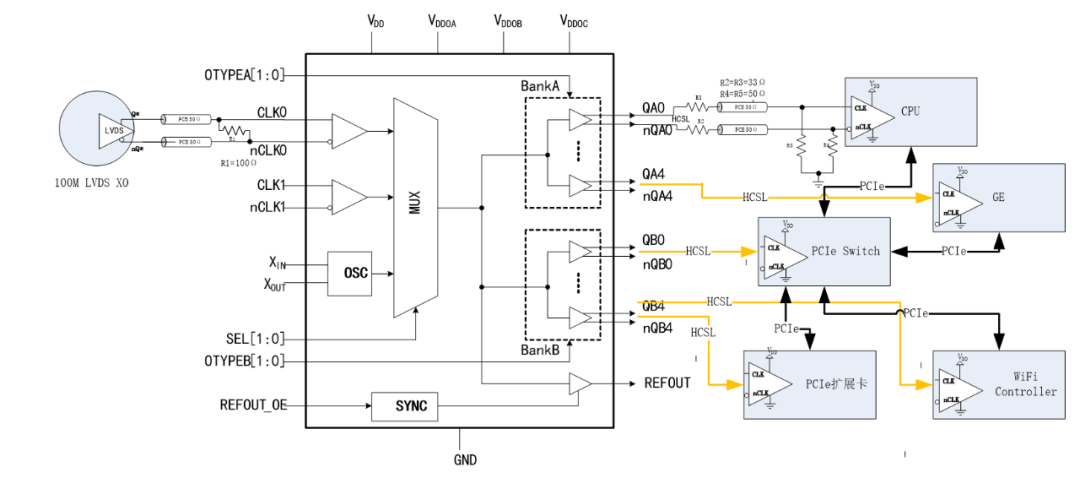

2.2. 高速接口

當使用Serdes發送或者接收串行bit流時,時鐘是用于對傳輸的數據進行編碼,并將時鐘信息嵌入到傳輸的數據中。接收器會從傳輸的比特流中分離出單獨的時鐘,用于對數據進行采樣和捕捉。在該系統中累計抖動決定了bit到達與采樣之間的時間差,因此它是最重要的。如果整個系統中抖動太大,會出現如圖9中所示的眼圖,從而會導致接受端采樣到錯誤的bit。表2給出了常見的高速接口抖動要求。

圖9 時鐘抖動對高速接口的影響

表2 常見的高速接口抖動要求

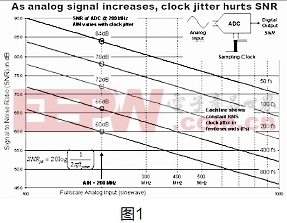

2.3. 數據轉換器

在模數轉換器(ADC)和數模轉換器(DAC)中,對信號的采樣可以轉換為信號與時鐘時域乘積。時鐘決定了信號采樣時間,如果時鐘抖動導致采樣時間偏離了理想采樣時間,會導致采樣到的信號值相比于理想的信號值發生變化,從而惡化信噪比和動態范圍,降低轉換器的有效分辨率。

采樣抖動是由外部時鐘抖動和ADC內部孔徑抖動決定:

![]()

采樣抖動造成的ADC SNR下降計算如下:

![]()

由量化噪聲、熱噪聲和采樣抖動三者一起決定ADC的SNR:

圖10 時鐘抖動對ADC采樣影響

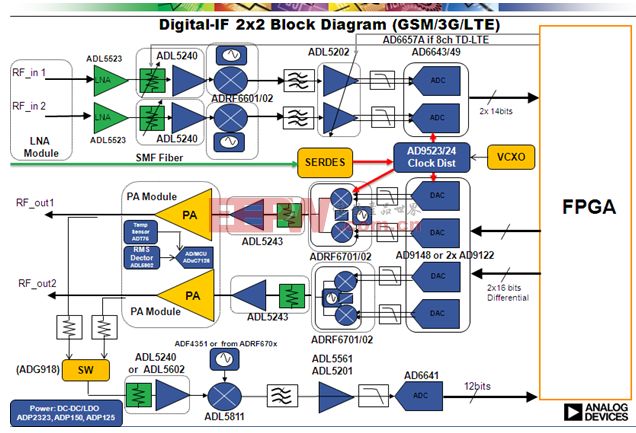

2.4. 射頻系統

在射頻系統中,時鐘主要為產生本振的鎖相環提供參考。鎖相環合成出來的本振信號通常為混頻器或者正交調制、解調器提供穩定的高頻振蕩頻率,用于產生發射信號或者下變頻的接收信號。當混頻器工作時,源信號會在時域上乘以本振時鐘來進行上變頻或下變頻,得到目標信號的頻譜為源信號頻譜與本振時鐘頻譜的乘積。

因此,本振時鐘中的任何相位噪聲都會在輸出端產生不想要的信號并混在目標信號中,可能會出現倒易混頻,從而降低系統中有用信號的信噪比,降低接收機的靈敏度,惡化發射機的ACLR和EVM,這就要求晶振和時鐘選型必須滿足嚴格的相位噪聲指標。

圖11 單音干擾時的倒易混頻

大普通信的Crystal和SPXO在-40℃~+85℃范圍內具有±20ppm的穩定度,42fs@156.25MHz的低相位抖動,具有單端和差分兩種輸出接口;TCXO具有-150dBc/Hz@1KHz的相位噪聲,OCXO極低相位噪聲-170dBc/Hz@1KHz,并達到-120dBC/Hz@1Hz的優越近端相噪。這些產品非常適合精密儀器、高速接口、數字系統、射頻系統等對相位噪聲有高需求的場景。

另外大普通信的SO系列全硅振蕩器,抗振動性能好,典型抖動為350fs,符合PCIe Gen1/2/3/4/5,支持頻率可配置,非常適合服務器、高速存儲、交換機等產品。

3. 相關術語

4. 參考文獻

[1] Telcordia GR-253-CORE Issue 4

[2] Renesas Application Note839《RMS phases jitter》

評論