時鐘抖動對光纖接入數字中頻系統的影響分析

摘要:本文根據光纖接入數字中頻系統的時鐘使用情況,分析了時鐘抖動對ADC和鎖相環性能影響的原理,講述了鎖相環的基本原理和相噪優化方式,最后給出采用雙環鎖相環來完成去抖和時鐘分發的解決方案。

本文引用地址:http://www.104case.com/article/130445.htm■數字中頻系統的時鐘信號

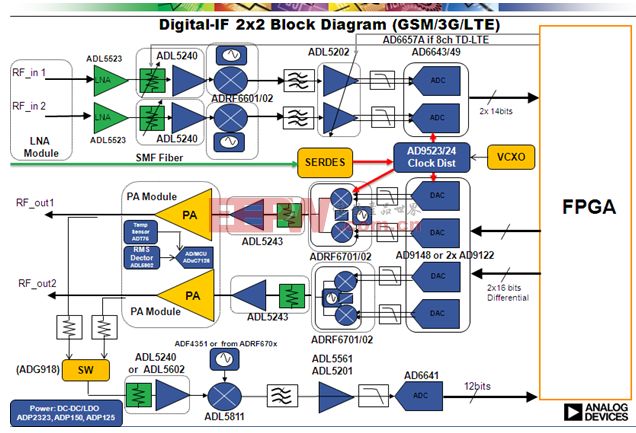

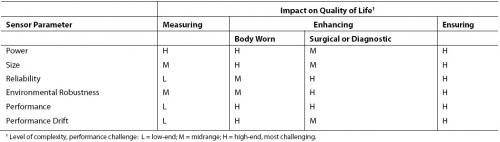

圖1

對于常見的數字中頻系統,例如RRU、數字光纖直放站,遠端設備中的時鐘信號都是從近端通過光纖傳輸過來的,由于光纖傳輸的色散影響,原有時鐘參考信號在通過光口芯片恢復出來后,其抖動指標會惡化。而在遠端設備中(如圖1),這個時鐘信號將會作為整個系統的參考時鐘,包括ADC,DAC,調制器和鎖相環等等。如果這個參考時鐘信號的抖動性能不佳,將會造成系統中上述器件的性能惡化。所以在光纖接入的數字中頻系統中,時鐘抖動設計非常重要。

■時鐘相噪對ADC性能的影響分析

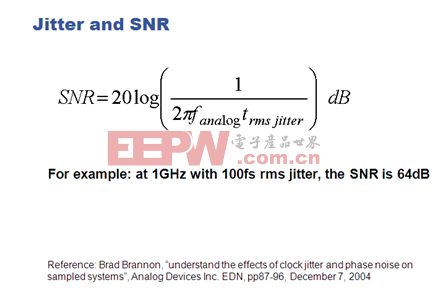

對于數字中頻系統中的ADC,SNR指標是我們非常關注的指標之一。這個指標會影響系統的動態范圍。我們知道一般一款設計好的高速ADC,它的SNR基本是確定。比如AD6649手冊給出在95MHz帶寬和245.76MSPS采樣率的條件下,SNR為73.4dBFs。而這個指標的前提是ADC的參考時鐘抖動指標非常好,如果系統提供給ADC的時鐘抖動不好,則會惡化實際SNR水平。如圖2,實際SNR取決于系統工作頻率和時鐘抖動。

圖2

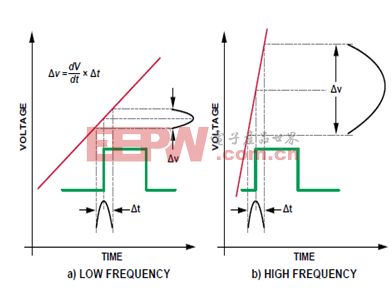

為什么會出現上面的現象?如圖3所示,綠色表示ADC的采樣時鐘波形,紅色則表示一個輸入模擬信號的瞬態截圖。黑色表示采樣的誤差范圍。我們可以看出。采樣時鐘的抖動在輸入信號投影誤差的大小會隨著采樣時鐘自身抖動增加而增加;同時,如果輸入信號的速率(或者說頻率)增加,它的瞬態斜率也會增加,那么投影誤差也會相應的增加。這張圖就解釋了圖2公式的原因。所以對于數字中頻系統的ADC需要提供優異的時鐘信號并且當輸入信號頻率(也叫中頻)越高時,越需要考慮這個問題。

圖3

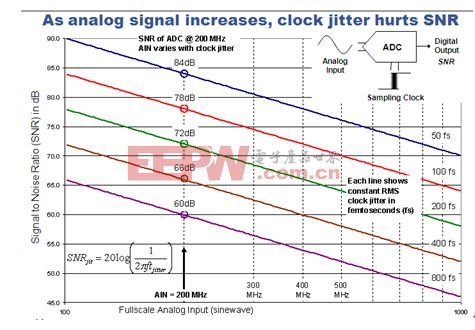

到底需要多小的抖動才能夠滿足系統的ADC的需求呢?如圖4所示。不同輸入頻率,在不同抖動水平下,可以達到不同的最大SNR水平。舉例,當輸入頻率為200MHz,系統時鐘抖動為200fs水平時候,可以達到SNR水平就是72dB(如圖4虛線和綠色線交叉點)。

圖4

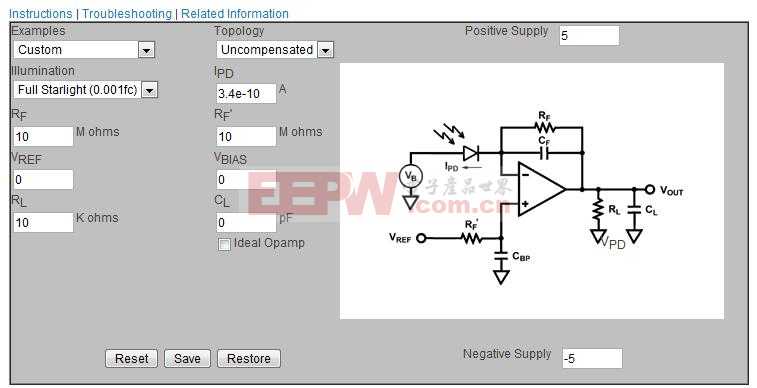

為了方便工程師衡量系統受抖動影響SNR的水平。ADI公司還可以提供一個在線的ADC性能仿真軟件ADIsimADC™。通過這個軟件可以選擇ADC型號后輸入時鐘的抖動水平,就可以得出SNR的實際水平和雜散SFDR水平。如圖5所示。

圖5

■時鐘對鎖相環的影響分析

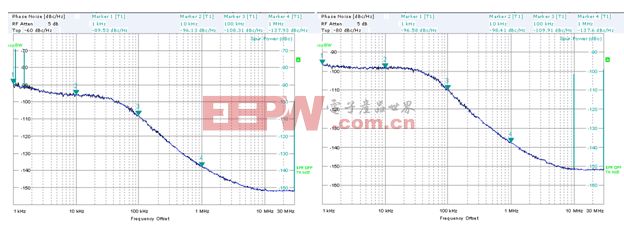

在數字中頻系統中,參考時鐘還會提供給鎖相環作為輸入參考頻率。而鎖相環的相噪好壞會影響到接收鏈路的EVM指標。這是因為輸入參考頻率的近端相噪進入鎖相環后,并不會被鎖相環的低通濾波器抑制,從來會影響到鎖相環輸出的近端相噪水平。而近端相噪有是系統接收機EVM指標的主要影響因素。圖6就是比較兩個不同參考相噪對于同一個鎖相環芯片ADF4351的近端相噪影響。可以看出1KHz頻率處,相噪分別為-96dBc/Hz和-89dBc/Hz。這就是由于鎖相環的參考時鐘近端相噪不同造成的差異。

圖6

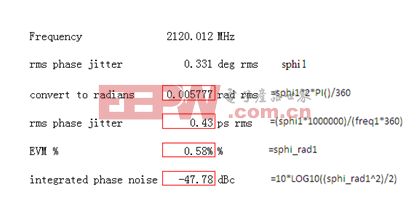

根據鎖相環輸出的相噪(抖動)水平和輸出頻率,可以通過下圖7的過程計算其對系統EVM的影響水平。因此我們可以得出結論:參考時鐘相噪影響鎖相環近端相噪,鎖相環近端相噪影響系統接收機的EVM指標。

圖7

■鎖相環原理和相噪產生原因分析

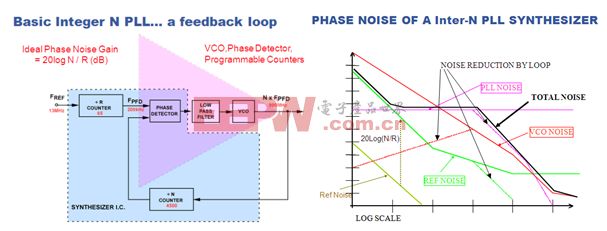

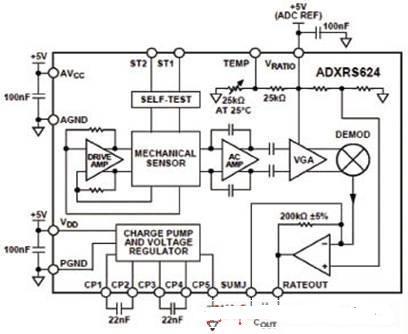

根據前面對系統的分析,我們知道時鐘抖動對于系統中的ADC和PLL(鎖相環)都有非常明顯的影響,那么如何才能在數字中頻系統中獲取更好的時鐘相噪呢?首先,要理解一下在數字中頻系統中核心器件,例如AD9523中PLL(鎖相環)的基本工作原理。見圖8左側所示,鎖相環其實是一個數模混合器件,它包括了數字的鑒相器和分頻器,以及模擬的電流泵、低通濾波器和VCO (壓控振蕩器)。從本質來說,PLL 是一個負反饋系統,它通過頻率信號的負反饋和鑒相比較,使得VCO工作在一個穩定的控制電壓下,從而達到輸出頻率穩定的作用。

圖8

圖8右側所示,黑色線表示PLL輸出的相噪相對頻率的水平,也就是我們在頻譜儀上觀測的結果。紅色線表示VCO的相噪水平,它被PLL的高通濾波響應所抑制掉了低頻的部分,而綠色線是黃色線(外部參考輸入相噪)的倍頻增益產物,它的高頻噪聲被PLL的低通響應所抑制,但是低頻(也稱之近端)相噪被保留。恰恰是這個特性導致了,如果PLL的輸入參考的相噪不好或者低通濾波器的截止頻率不夠低,就會導致參考時鐘相噪被搬移到PLL的輸出端。

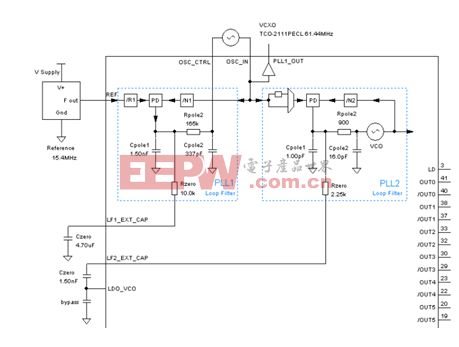

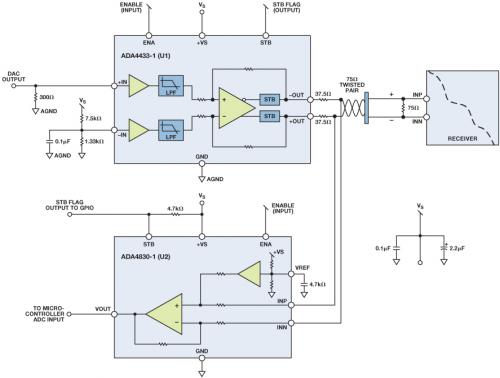

■AD9523實例用低環路濾波器去抖

根據上面的分析,系統為了提高時鐘近端相噪水平,就需要提高參考時鐘的相噪水平或者降低PLL低通濾波器的頻率。而在光纖接入數字中頻系統中,參考時鐘是從光口恢復的,它本身就存在近端相噪(抖動)惡化的問題。如何解決這個矛盾呢?只能從降低低通濾波器頻率入手。如圖9所示,AD9523在設計中使用了兩個鎖相環,第一個PLL接外部的參考時鐘(光口恢復的),它采取非常低的低通濾波器設置(10Hz~100Hz)。它可以將參考時鐘近端相噪很好的濾除,而PLL外接的VCXO可以提供很好的近端相噪,這樣保證不會因為低通濾波器頻率低而將VXCO的近端噪聲抬高(注意,這里對于VXCO來說低通濾波器變為高通濾波響應)。這樣第一個PLL就可以將參考時鐘近端相噪很好的抑制。而第二個鎖相環采用高頻率VCO(3600MHz到4000MHz)和70MHz的鑒相頻率。這樣可以降低噪聲頻率增益的同時,獲取更多的頻率組合(系統中有時需要不同頻率的工作時鐘,VCO需要工作在它們的最小公倍數的整數倍)。

圖9

■參考文獻:

[1] Brad Brannon, Allen Barlow. AN-501 孔徑不確定度與ADC系統性能

[2] Brad Brannon, Bill Schoield, Yang Ming.AN-0974: TD-SCMA多載波系統可行性研究

[3] CN-0134寬帶低EVM直接變頻發射機

[4]鎖相環常見問題解答ADI官方網站

■作者簡介:

孫凱(ray.sun@analog.com)就職于ADI武漢分公司,主要負責通信和汽車電子類客戶的現場技術支持工作,擅長RF和高速產品的技術研究和問題分析。他于2002年畢業于武漢理工大學通信工程專業,后在烽火科技虹信公司負責直放站系列產品的開發和項目管理,2009年加入ADI武漢分公司,2010年畢業于華中科技大學MBA專業。

分頻器相關文章:分頻器原理

評論