Astera Labs推出云規模互操作實驗室,實現大規模無縫部署CXL解決方案

先進的專用連接解決方案公司Astera Labs(Astera Labs)近日宣布,擴展其云規模互操作實驗室(Cloud-Scale Interop Lab),支持Leo內存連接平臺(Leo Memory Connectivity Platform)與不斷成長的生態系統之間實現強大的互操作性測試,該生態系統包括領先CXL為基礎的CPU、內存模塊和操作系統。

Astera Labs首席產品官Casey Morrison表示:“Compute Express Link?(CXL?)經證明是數據中心系統里關鍵的內存互連技術,但是,多種應用場景和快速成長的生態系統是大規模無縫部署CXL解決方案的重大挑戰。基于Aries PCIe? Smart Retimers云規模互操作實驗室的成功以及從客戶平臺上運行的真實CXL硅芯片解決方案中學到的知識,我們很高興與行業主要廠商合作實現提供端到端CXL測試和工具,最大程度減少互操作風險,縮短系統開發時間和成本,加快上市時間。”

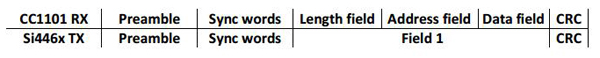

云端互操作性實驗室擁有全面的內存壓力測試、CXL協議檢查和電氣穩健性測量工具,對CPU、Leo智能內存控制器和各種內存模塊在實際應用場景下的性能和互操作性進行驗證。測試涵蓋從物理層到應用層的四個關鍵領域,包括PCIe電氣、內存、CXL合規性以及重復數千次的系統級測試。

云規模互操作實驗室主要合作伙伴

Astera Labs正在與行業領導者合作進行互操作性測試,為不斷成長的CXL市場提供CPU和內存模塊。

CXL聯盟主席Jim Pappas表示:“CXL聯盟(CXL Consortium)舉辦活動旨在測試成員公司的產品是否符合我們的規范。憑借其云規模互操作實驗室,Astera Labs將嚴格的互操作性測試從物理級別擴展到系統級別,包括各種主機、內存和操作系統。作為CXL聯盟的貢獻成員,Astera Labs的供應商中立方式將有助于加速將CXL內存解決方案推向市場。”

AMD服務器系統架構師高級研究員Mahesh Wagh表示:“標準合規性和即插即用功能是發展CXL生態系統的重要一步。第4代霄龍(AMD EPYC?)處理器與CXL1.1標準兼容,有助于創建可組合的架構,提供客戶所需的基礎架構靈活性、安全性和性能要求。我們贊賞Astera Labs對互操作性測試的承諾,并期待繼續合作,提供真正的異構計算。”

英特爾公司高級研究員Debendra Das Sharma博士表示:“英特爾致力于加速CXL生態系統,我們期待繼續與Astera Labs合作,參與其云規模互操作實驗室,讓我們的客戶能夠更輕松部署可靠且可互操作的CXL解決方案。”

美光高級副總裁兼計算和網絡業務部總經理Raj Hazra表示:“美光正在為使用CXL的數據中心提供內存創新,我們正與Astera Labs合作,在其云規模互操作實驗室測試我們的DDR內存解決方案。我們將共同緩解內存帶寬瓶頸,提供可互操作的解決方案,為數據中心和云基礎設施客戶帶來更大的靈活性。”

SK海力士副總裁兼DRAM應用工程組負責人Hyungsoo Kim表示:“我們擁有廣泛的高性能和高密度DDR5 DRAM產品系列,可實現CXL附加內存擴展和池化(pooling)的全部潛力,為云服務器服務。通過總部和美國工程中心的貢獻,SK海力士很高興與Astera Labs合作,在其云規模互操作實驗室中驗證我們的內存,讓我們的客戶能夠確信我們的解決方案將與Astera Labs的CXL控制器和客戶選擇的CPU無縫互操作。”

評論