降低時(shí)間成本提升良率 泰瑞達(dá)為半導(dǎo)體測(cè)試提速

芯片測(cè)試貫穿于半導(dǎo)體研發(fā)到量產(chǎn)的全部過(guò)程,是半導(dǎo)體制造無(wú)法繞開的一環(huán)。雖然近些年半導(dǎo)體工藝的演進(jìn)速度放緩,但因?yàn)橹圃旃に嚨木?xì)和芯片內(nèi)部結(jié)構(gòu)的復(fù)雜,使得測(cè)試和驗(yàn)證的復(fù)雜程度大幅提升。

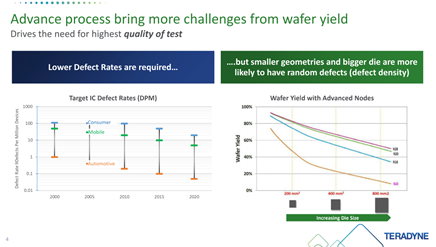

新工藝,新挑戰(zhàn)

隨著制作工藝越來(lái)越先進(jìn),芯片上的晶體管集成度也越來(lái)越高。為數(shù)量暴增的晶體管進(jìn)行測(cè)試勢(shì)必會(huì)造成芯片測(cè)試時(shí)間的增加。另外,模擬和射頻芯片測(cè)試過(guò)程中模擬測(cè)試占比重較大,且在測(cè)試之前需在內(nèi)部進(jìn)行trim調(diào)整,這樣會(huì)帶來(lái)額外的測(cè)試時(shí)間,測(cè)試時(shí)間的增加,就意味著更高的測(cè)試成本。Wafer yield也是先進(jìn)工藝帶來(lái)的一個(gè)挑戰(zhàn), wafer的初次yield不斷下降。越來(lái)越復(fù)雜的芯片也讓每顆芯片的Die size不斷增加,進(jìn)而增加芯片的失效概率。

泰瑞達(dá)的應(yīng)對(duì)之道

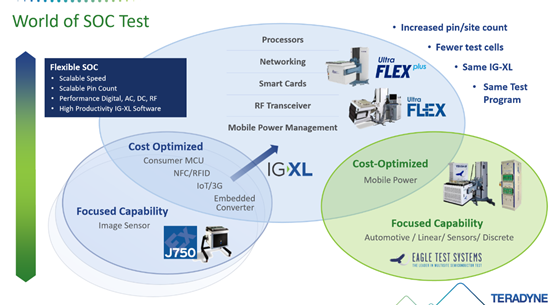

作為ATE領(lǐng)域的領(lǐng)軍企業(yè)之一,泰瑞達(dá)(TERADYNE)擁有雄厚的技術(shù)積累和完整的半導(dǎo)體測(cè)試解決方案。過(guò)去多年中,泰瑞達(dá)已經(jīng)推出了多款測(cè)試設(shè)備,包括測(cè)試低成本解決方案J750和用來(lái)應(yīng)對(duì)更高級(jí)別測(cè)試需求的UltraFLEX系列。

泰瑞達(dá)銷售副總經(jīng)理黃飛鴻介紹表示:“日新月異的終端市場(chǎng)在拉動(dòng)芯片需求大幅增長(zhǎng)的同時(shí),也對(duì)測(cè)試平臺(tái)有了更嚴(yán)格的要求。” 為了應(yīng)對(duì) “量產(chǎn)數(shù)據(jù)激增”、 “量產(chǎn)測(cè)試時(shí)間大幅延長(zhǎng)“等諸多新型挑戰(zhàn)。泰瑞達(dá)旗下產(chǎn)品UltraFLEXplus高性能SoC測(cè)試平臺(tái)應(yīng)運(yùn)而生,并利用 UltraFLEX 過(guò)去 15 年累積開發(fā)的測(cè)試 IP,使產(chǎn)能和工程效率的得到了跨越式的改善。

泰瑞達(dá)的測(cè)試解決方案及適用范圍示意

多維度升級(jí),滿足新興測(cè)試需求

UltraFLEXplus平臺(tái)對(duì)芯片測(cè)試接口板設(shè)計(jì)進(jìn)行了完全革命性的改進(jìn),采用Broadside技術(shù)可使接口板的應(yīng)用區(qū)域擴(kuò)大,同時(shí)降低接口板PCB層數(shù)。通過(guò)簡(jiǎn)化原本復(fù)雜的 DIB布局,實(shí)現(xiàn)更快的上市時(shí)間、和更高的PCB良率。

UltraFLEXplus系列還增加了工位數(shù),并通過(guò)提高并行測(cè)試效率來(lái)減少多工位測(cè)試時(shí)間開銷,從而滿足測(cè)試需求。減少測(cè)試單元的數(shù)量可以最大程度降低總制造成本。除此之外UltraFLEXplus 引入了創(chuàng)新性的PACE運(yùn)行架構(gòu),實(shí)現(xiàn)板卡控制下放,提升處理效率,以最小的工程量創(chuàng)造出最高的測(cè)試單元產(chǎn)能。可助力工程師更快、更好地完成更繁重的測(cè)試任務(wù)。

黃飛鴻表示:“值得一提的是,J750、UltraFLEX以及UltraFLEXplus三款產(chǎn)品均使用統(tǒng)一的測(cè)試軟件平臺(tái)IG-XL,這就意味著工程師開發(fā)的程序可以輕易在上述設(shè)備間實(shí)現(xiàn)無(wú)縫遷移,這無(wú)疑將簡(jiǎn)化開發(fā)難度、縮短開發(fā)時(shí)間,測(cè)試工程師能夠以更少的工作量將更高質(zhì)量的新測(cè)試程序發(fā)布到量產(chǎn)環(huán)境中。”

IG-XL 軟件、獨(dú)有的 PACE 架構(gòu)和 Broadside 應(yīng)用接口的完美結(jié)合,使得新一代測(cè)試平臺(tái)UltraFLEXplus無(wú)論是測(cè)試效率,測(cè)量精準(zhǔn)度,各方面指標(biāo)都有極大的提升。

目前,UltraFLEX測(cè)試平臺(tái)全球裝機(jī)量已經(jīng)達(dá)到5000套,而IG-XL軟件平臺(tái)裝機(jī)也超過(guò)了12000套。泰瑞達(dá)具備豐富的市場(chǎng)驗(yàn)證經(jīng)驗(yàn),在UltraFLEXplus新平臺(tái)發(fā)布一年半以來(lái),全球裝機(jī)量已接近600套,并以其優(yōu)異的表現(xiàn)得到了市場(chǎng)的青睞與客戶的認(rèn)可。

評(píng)論