PC 新時(shí)代!DDR5 內(nèi)存規(guī)范正式發(fā)布:最高速度達(dá) 6.4Gbps,單芯片密度達(dá) 64Gbit

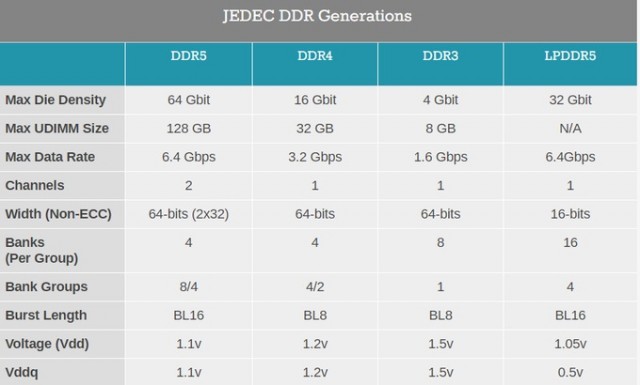

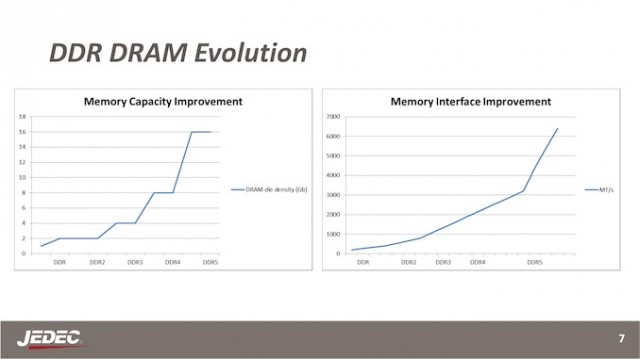

作為計(jì)算機(jī)內(nèi)存發(fā)展的重要里程碑,JEDEC固態(tài)技術(shù)協(xié)會(huì)發(fā)布了下一個(gè)主流內(nèi)存標(biāo)準(zhǔn)DDR5 SDRAM的最終規(guī)范。DDR5是DDR標(biāo)準(zhǔn)的最新迭代,DDR5再次擴(kuò)展了DDR內(nèi)存的功能,將峰值內(nèi)存速度提高了一倍,同時(shí)也大大增加了內(nèi)存容量。基于新標(biāo)準(zhǔn)的硬件預(yù)計(jì)將于2021年推出,先從服務(wù)器層面開(kāi)始采用,之后再逐步推廣到消費(fèi)者PC和其他設(shè)備。

本文引用地址:http://www.104case.com/article/202007/415830.htm

外媒anandtech報(bào)道,和之前的每一次DDR迭代一樣,DDR5的主要關(guān)注點(diǎn)再次放在提高內(nèi)存密度以及速度上。JEDEC希望將這兩方面都提高一倍,最高內(nèi)存速度將達(dá)到6.4Gbps,而單條LRDIMM的容量最終將能夠達(dá)到2TB,最大UDIMM容量為128 GB。同時(shí),還有一些較小的變化,以支持這些目標(biāo)或簡(jiǎn)化生態(tài)系統(tǒng)的某些方面,如on-DIMM電壓調(diào)節(jié)器以及on-die ECC。

更大:更密集的內(nèi)存和芯片堆疊

首先是容量和密度,因?yàn)檫@是與DDR4相比最直接的標(biāo)準(zhǔn)變化。IT之家了解到,DDR5將允許單個(gè)內(nèi)存芯片的密度達(dá)到64Gbit,比DDR4的16Gbit密度最大值高出4倍。再加上Die堆疊,最多允許8個(gè)Die堆疊為一個(gè)芯片,那么40個(gè)元件的LRDIMM可以達(dá)到2TB的有效內(nèi)存容量。或者對(duì)于更簡(jiǎn)陋的無(wú)緩沖DIMM來(lái)說(shuō),這將意味著最終會(huì)看到DIMM容量達(dá)到128GB的典型雙列配置。

當(dāng)然,當(dāng)芯片制造趕上規(guī)格所能允許的范圍時(shí),DDR5規(guī)格的峰值容量將用在標(biāo)準(zhǔn)生命周期的后期,首先,內(nèi)存制造商將使用當(dāng)今可達(dá)到的密度8Gbit和16Gbit芯片來(lái)構(gòu)建DIMM。因此,雖然DDR5的速度提升相當(dāng)直接,但隨著制造密度的提高,容量的提升將更加緩慢。

更快:一個(gè)DIMM,兩個(gè)通道

DDR5再次提高了內(nèi)存帶寬。每個(gè)人都希望獲得更高的性能(尤其是在DIMM容量不斷增長(zhǎng)的情況下),這也是這次DDR5提升的重點(diǎn)。

對(duì)于DDR5來(lái)說(shuō),JEDEC希望比通常的DDR內(nèi)存規(guī)范更積極地開(kāi)始工作。通常情況下,新的標(biāo)準(zhǔn)是從上一個(gè)標(biāo)準(zhǔn)的起點(diǎn)開(kāi)始的,例如DDR3到DDR4的過(guò)渡,DDR3正式停止在1.6Gbps,DDR4從那里開(kāi)始。然而對(duì)于DDR5來(lái)說(shuō),JEDEC的目標(biāo)要高得多,預(yù)計(jì)將以4.8Gbps的速度推出,比DDR4 官方3.2Gbps最高速度快了50%左右。而在之后的幾年里,當(dāng)前版本的規(guī)范允許數(shù)據(jù)速率達(dá)到6.4Gbps,比DDR4的官方峰值快了一倍。

這些速度目標(biāo)的基礎(chǔ)是DIMM和內(nèi)存總線(xiàn)的變化,以便在每個(gè)時(shí)鐘周期內(nèi)提供和傳輸更多數(shù)據(jù)。對(duì)于DRAM速度來(lái)說(shuō),最大的挑戰(zhàn)來(lái)自于DRAM核心時(shí)鐘速率缺乏進(jìn)步。專(zhuān)用邏輯仍然在變快,內(nèi)存總線(xiàn)仍然在變快,但支撐現(xiàn)代內(nèi)存的基于電容和晶體管的DRAM時(shí)鐘速度還不能超過(guò)幾百兆赫。因此,為了從DRAM Die中獲得更多的收益--維持內(nèi)存本身越來(lái)越快的假象,并滿(mǎn)足實(shí)際速度更快的內(nèi)存總線(xiàn)--已經(jīng)需要越來(lái)越多的并行性。而DDR5則再次提升了這一要求。

這里最大的變化是,與LPDDR4和GDDR6等其他標(biāo)準(zhǔn)情況類(lèi)似,單個(gè)DIMM被分解為2個(gè)通道。DDR5將不是每個(gè)DIMM提供一個(gè)64位數(shù)據(jù)通道,而是每個(gè)DIMM提供兩個(gè)獨(dú)立的32位數(shù)據(jù)通道(如果考慮ECC因素,則為40位)。同時(shí),每個(gè)通道的突發(fā)長(zhǎng)度從8個(gè)字節(jié)(BL8)翻倍到16個(gè)字節(jié)(BL16),這意味著每個(gè)通道每次操作將提供64個(gè)字節(jié)。那么,與DDR4 DIMM相比,DDR5 DIMM以?xún)杀兜念~定內(nèi)存速度(核心速度相同)運(yùn)行,將在DDR4 DIMM提供的操作時(shí)間內(nèi)提供兩個(gè)64字節(jié)的操作,使有效帶寬增加一倍。

總的來(lái)說(shuō),64字節(jié)仍然是內(nèi)存操作的神奇數(shù)字,因?yàn)檫@是一個(gè)標(biāo)準(zhǔn)緩存線(xiàn)的大小。如果在DDR4內(nèi)存上采用更大的突發(fā)長(zhǎng)度,則會(huì)導(dǎo)致128字節(jié)的操作,這對(duì)于單條高速緩存線(xiàn)來(lái)說(shuō)太大,如果內(nèi)存控制器不想要兩條線(xiàn)的連續(xù)數(shù)據(jù),充其量也會(huì)導(dǎo)致效率/利用率的損失。相比之下,由于DDR5的兩個(gè)通道是獨(dú)立的,一個(gè)內(nèi)存控制器可以從不同的位置請(qǐng)求64個(gè)字節(jié),這使得它更符合處理器的實(shí)際工作方式,并避免利用率的損失。

對(duì)標(biāo)準(zhǔn)PC臺(tái)式機(jī)的凈影響是,取代了DDR4系統(tǒng)模式,即2個(gè)DIMM填滿(mǎn)2個(gè)通道進(jìn)行2x64bit設(shè)置,而DDR5系統(tǒng)的功能將是4x32bit設(shè)置。

這種結(jié)構(gòu)上的變化在其他地方有一些連鎖效應(yīng),特別是要最大限度地提高這些小通道的使用率。DDR5引入了更細(xì)粒度的Bank存儲(chǔ)體刷新功能,這將允許一些k存儲(chǔ)體在其他使用時(shí)進(jìn)行刷新。這就能更快地完成必要的刷新(電容補(bǔ)給)、控制延遲、并使未使用的存儲(chǔ)庫(kù)更快可用。存儲(chǔ)體組的最大數(shù)量也從4個(gè)增加到8個(gè),這將有助于減輕順序內(nèi)存訪(fǎng)問(wèn)的性能折扣。

快速總線(xiàn)服務(wù):決策反饋均衡化

相比之下想辦法增加DRAM DIMM內(nèi)的并行化量,提高總線(xiàn)速度既簡(jiǎn)單又困難:概念簡(jiǎn)單,執(zhí)行起來(lái)比較難。最后要想讓DDR的內(nèi)存速度提高一倍,DDR5的內(nèi)存總線(xiàn)需要以?xún)杀队贒DR4的速度運(yùn)行。

為了實(shí)現(xiàn)這一目標(biāo),DDR5有幾項(xiàng)改變,但令人驚訝的是,并沒(méi)有對(duì)內(nèi)存總線(xiàn)進(jìn)行任何大規(guī)模、根本性的改變,如QDR或差分信令。相反,JEDEC及其成員已經(jīng)能夠通過(guò)略微修改的DDR4總線(xiàn)來(lái)實(shí)現(xiàn)他們的目標(biāo),盡管它必須在更嚴(yán)格的公差下運(yùn)行。

這里的關(guān)鍵驅(qū)動(dòng)力是引入決策反饋均衡(DFE)。在很高的層次上,DFE是一種通過(guò)使用內(nèi)存總線(xiàn)接收器的反饋來(lái)提供更好的均衡,從而降低符號(hào)間干擾的手段。而更好的均衡,又可以讓DDR5的內(nèi)存總線(xiàn)以更高的傳輸速率運(yùn)行所需的更干凈的信令,而不至于發(fā)生故障。同時(shí),標(biāo)準(zhǔn)中的一些較小的變化也進(jìn)一步幫助了這一點(diǎn),例如增加了新的和改進(jìn)的訓(xùn)練模式,以幫助DIMM和控制器補(bǔ)償內(nèi)存總線(xiàn)上的微小時(shí)序差異。

更簡(jiǎn)單的主板,更復(fù)雜的DIMM:On-DIMM電壓調(diào)節(jié)

在核心改變密度和內(nèi)存速度的同時(shí),DDR5也再次改善了DDR內(nèi)存的工作電壓。在規(guī)格上DDR5的工作電壓Vdd將從DDR4的1.2v降至1.1v。這應(yīng)該會(huì)提高內(nèi)存相對(duì)于DDR4的能效,盡管到目前為止,功耗的提升并沒(méi)有像DDR4和更早的標(biāo)準(zhǔn)那樣被大力推廣。

JEDEC還利用DDR5內(nèi)存標(biāo)準(zhǔn)的推出,對(duì)DIMM的電壓調(diào)節(jié)方式進(jìn)行了相當(dāng)重要的改變。簡(jiǎn)而言之,電壓調(diào)節(jié)將從主板轉(zhuǎn)移到單個(gè)DIMM上,讓DIMM負(fù)責(zé)自己的電壓調(diào)節(jié)需求。這意味著DIMM現(xiàn)在將包括一個(gè)集成的電壓調(diào)節(jié)器,這適用于從UDIMMs到LRDIMMs的所有產(chǎn)品。

JEDEC將此稱(chēng)為“隨用隨付”的電壓調(diào)節(jié),旨在通過(guò)它來(lái)改善/簡(jiǎn)化DDR5的幾個(gè)不同方面。最重要的變化是,通過(guò)將電壓調(diào)節(jié)轉(zhuǎn)移到DIMMs本身,電壓調(diào)節(jié)不再是主板的責(zé)任。主板則不再需要為最壞的情況--比如驅(qū)動(dòng)16個(gè)龐大的LRDIMM--簡(jiǎn)化主板設(shè)計(jì),并在一定程度上控制成本。當(dāng)然,反過(guò)來(lái)說(shuō),它將這些成本轉(zhuǎn)移到了DIMM本身,但這樣一來(lái),系統(tǒng)構(gòu)建者至少只需要購(gòu)買(mǎi)和DIMM一樣多的電壓調(diào)節(jié)硬件,因此也就有了PAYGO理念。

根據(jù)JEDEC的說(shuō)法,On-DIMM穩(wěn)壓器還將使一般的電壓容差更好,提高DRAM的良品率。

由于這些電壓調(diào)節(jié)器的實(shí)現(xiàn)細(xì)節(jié)將由內(nèi)存廠商決定,所以JEDEC并沒(méi)有對(duì)其進(jìn)行過(guò)多的說(shuō)明。客戶(hù)端UDIMM和服務(wù)器(L)RDIMM將有單獨(dú)的穩(wěn)壓器/PMIC,以反映它們的功耗需求。

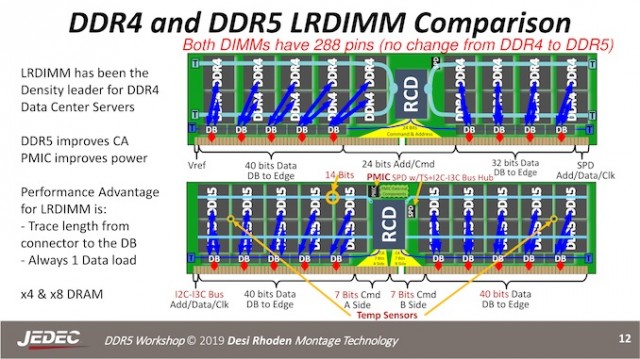

DDR5 DIMMs:依然是288個(gè)針腳,但改變了針腳布局

最后,正如早期廠商的原型產(chǎn)品已經(jīng)廣泛展示的那樣,DDR5將保持與DDR4相同的288個(gè)引腳數(shù)。這反映了DDR2到DDR3的過(guò)渡,其中的引腳數(shù)也保持在240個(gè)引腳。

然而,不要指望在DDR4插槽上使用DDR5 DIMM。雖然引腳數(shù)量沒(méi)有改變,但引腳布局卻發(fā)生了變化,以適應(yīng)DDR5的新特性--尤其是其雙通道設(shè)計(jì)。

這里最大的變化是命令和地址總線(xiàn)被縮小和分區(qū),引腳被重新分配到第二個(gè)內(nèi)存通道的數(shù)據(jù)總線(xiàn)上。DDR5將不再是單一的24位CA總線(xiàn),而是有兩個(gè)7位CA總線(xiàn),每個(gè)通道一個(gè)。當(dāng)然,7位遠(yuǎn)遠(yuǎn)不到舊總線(xiàn)的一半,所以對(duì)于內(nèi)存控制器來(lái)說(shuō),換來(lái)的事情變得更加復(fù)雜。

現(xiàn)在開(kāi)始采樣,未來(lái)12-18個(gè)月內(nèi)采用

和其他JEDEC規(guī)范發(fā)布一樣,今天是開(kāi)發(fā)委員會(huì)將標(biāo)準(zhǔn)放給成員使用。各大內(nèi)存廠商從一開(kāi)始就參與了DDR5的開(kāi)發(fā)過(guò)程,他們已經(jīng)開(kāi)發(fā)出了DIMM的原型,現(xiàn)在正在考慮將第一個(gè)商用硬件推向市場(chǎng)。

預(yù)計(jì)DDR5整體采用曲線(xiàn)將與早期的DDR標(biāo)準(zhǔn)相似。也就是說(shuō),JEDEC預(yù)計(jì)DDR5將在12到18個(gè)月內(nèi)隨著硬件的最終確定而開(kāi)始出現(xiàn)在設(shè)備中,并逐步增加。他們預(yù)計(jì)服務(wù)器將再次成為早期采用的驅(qū)動(dòng)力,尤其是主要的超大規(guī)模廠商。英特爾和AMD都沒(méi)有正式宣布將使用新內(nèi)存的平臺(tái),但目前這只是時(shí)間問(wèn)題。

同時(shí),預(yù)計(jì)DDR5的生命周期將和DDR4一樣長(zhǎng),甚至更長(zhǎng)一些。DDR3和DDR4都享有大約7年的生命周期,DDR5也應(yīng)該享有同樣程度的穩(wěn)定性。目前JEDEC認(rèn)為,DDR5最終會(huì)比DDR4擁有更長(zhǎng)的保質(zhì)期,這得益于技術(shù)產(chǎn)業(yè)的不斷成熟。

評(píng)論