Mentor Catapult HLS 助力Chips&Media 將深度學習硬件加速器 IP 交付時間縮短一半

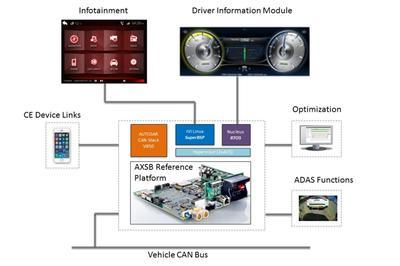

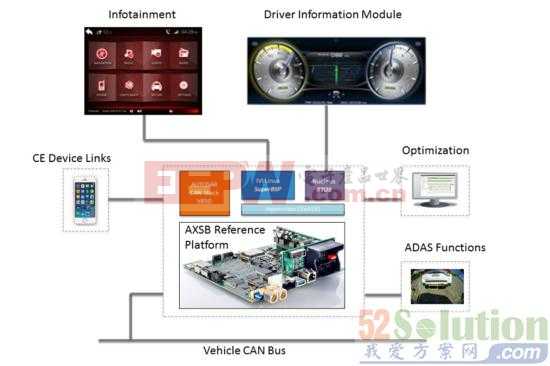

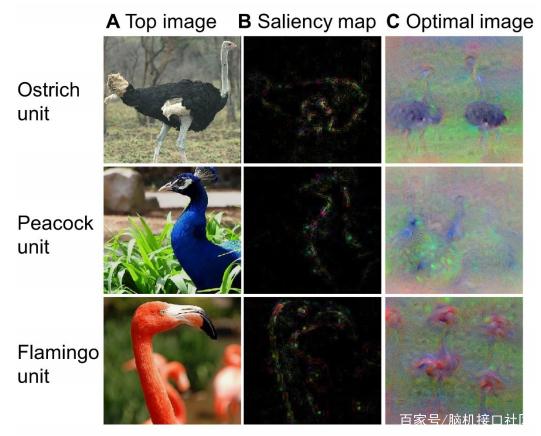

Mentor?, a Siemens business 今日宣布 Chips&Media? 已成功部署 Mentor Catapult? HLS 平臺,將使用深度神經網絡 (DNN) 算法設計和驗證其 c.WAVE 計算機視覺 IP 的實時對象檢測。Chips&Media 是一家面向片上系統 (SoC) 設計高性能、高質量視頻 IP 的領先供應商,其產品廣泛應用于汽車、監控和消費電子領域。

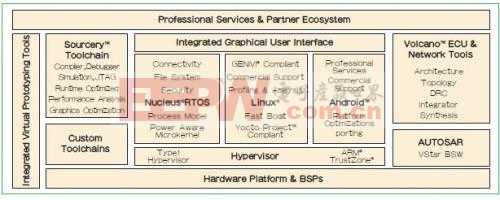

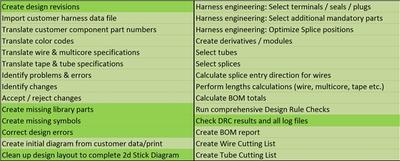

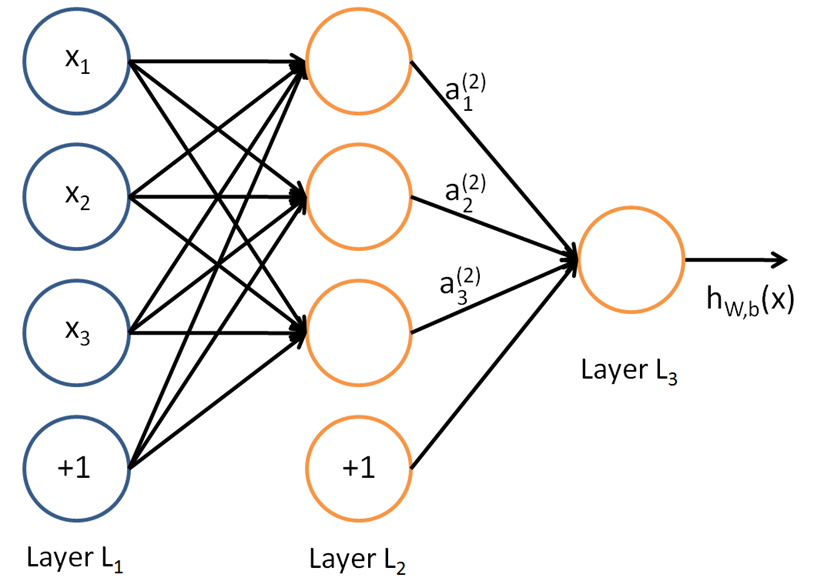

本文引用地址:http://www.104case.com/article/201902/397689.htmChips&Media 需要通過減少功能驗證時間、時序收斂、自定義和最終優化來大幅提高生產力,把更多時間用于機器算法和架構的研發上,從而為客戶快速提供差異化的機器學習 IP。為實現這些目標,他們棄用了傳統的手工編碼寄存器傳輸級 (RTL) 流程,轉而采用 Catapult HLS 平臺,以使用 C 語言編寫算法和驗證平臺。與同一項目中使用 RTL 流程的團隊相比,HLS 設計和驗證團隊將項目時間縮短了一半。

“要應對以推理為目標的設備帶來的加速挑戰,我們認為關鍵在于使用深度神經網絡建立一個專注于功耗、性能和面積 (PPA) 并高度優化的硬件架構,”Chips&Media 首席技術官 Mickey Jeon 表示。“HLS 使我們能夠極其高效地完成這項工作。我們的項目取得了突出的成績,我們計劃在接下來的項目中部署應用 Catapult 的 HLS 流程。”

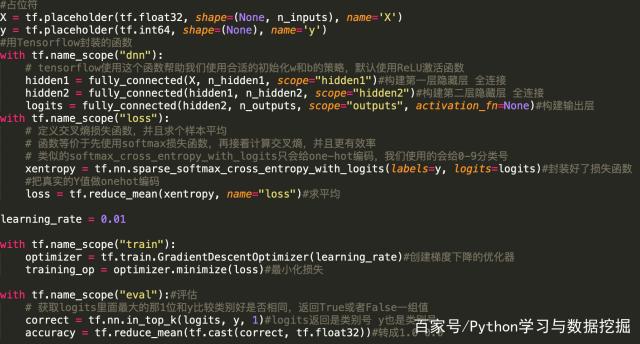

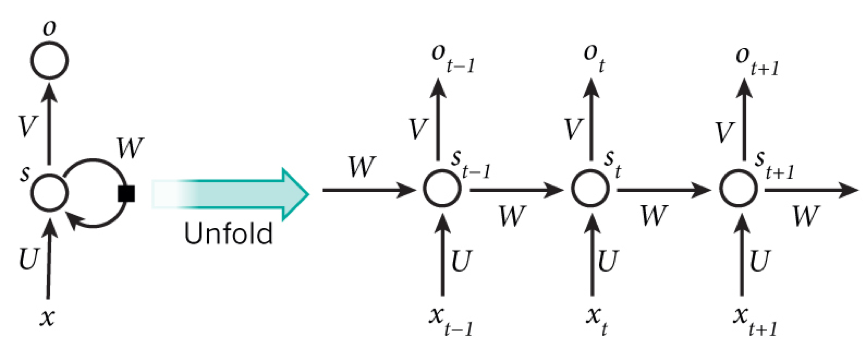

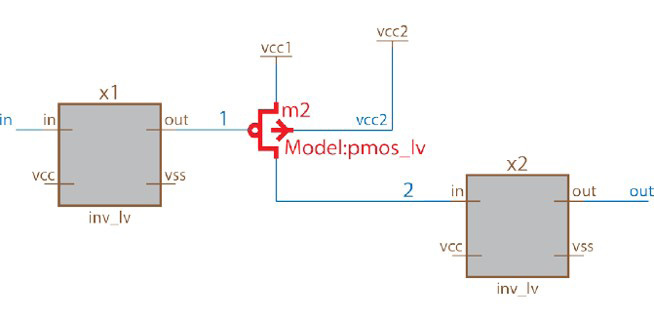

基于 DNN 的計算機視覺處理的特征,就是乘法/加法/累加的重復計算,同時通過神經網絡層進行大量數據遷移。DNN 是在 Caffe 或 TensorFlow? 等框架上開發的,然后在 C 模型中捕獲其算法。Chips&Media 將此算法 C 模型改進為可綜合的 C 代碼,并使用 Catapult HLS 平臺快速探索各種架構并綜合到 RTL 中,以找到此類設計的最佳解決方案。

“根據我們的觀察,在市場快速變化的多個應用領域,采用 Catapult HLS 是提高生產力來獲得成功的唯一途徑,”Mentor 數字設計和實施解決方案總經理 Badru Agarwala 表示。“我們一直與 Chips&Media 密切合作,以確保他們平穩過渡到 HLS。該平臺可以讓他們專注于算法/架構設計,而不是底層實現和調試等細節,從而更快地把想法變成產品,然后推向市場。”

有關更多詳細信息,請參閱詳細的案例研究:《Chips&Media:深度學習對象檢測 IP 的設計和驗證》。

評論