TD2SCDMA終端綜合測試儀物理層的軟硬件設計

由于FPGA 內部RAM 容量的限制,只能緩存一小段時間內12 倍速的數據,設計時充分考慮到這點限制。FPGA 只緩存200μs 12 倍速數據和5 ms (一個TD-SCDMA 系統子幀) 4 倍速數據。每200 μs 產生定時中斷給DSP,并設置相應信號量。DSP 檢測到是否接收FPGA 數據的情況,然后判斷4 倍速數據是否收齊以采取相應動作,這樣就解決了F PGA 內部高速RAM 容量有限的問題。

一般以FPGA + DSP 為硬件平臺的解決方案中,圖3 中產生TD-SCDMA 信號和TD-SCDMA 信號解調2 個模塊不全部在DSP 中實現。考慮到本物理層需要復雜的流程處理,本方案采用全DSP 實現。

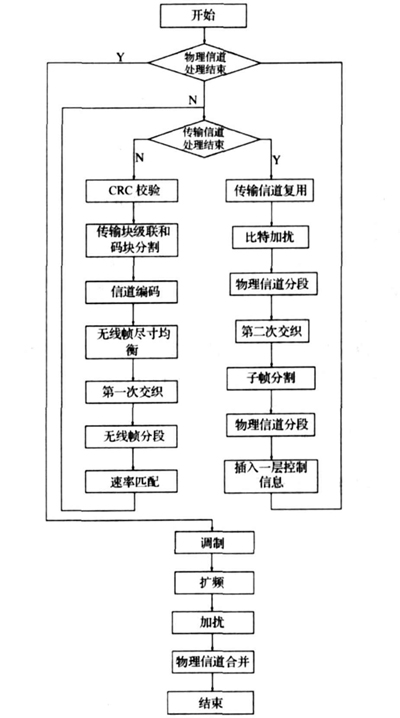

由于圖中生成TD-SCDMA 信號與解調TD2SC2DMA 信號流程互為相反過程,所以下面只闡述生成TD-SCDMA 信號部分。為了闡述方便, 考慮沒有智能天線的情況。如果實現智能天線,只需要稍加擴展。生成TD-SCDMA 信號的流程圖如圖4 所示。

圖4 生成TD-SCDMA 信號的流程圖

每次調用成幀過程,首先采用全DSP 實現方案所特有的調度算法判斷是否所有物理信道都處理完畢,如果不是,則選擇一個物理信道進行下一步處理。

采用另一特有調度算法判斷該物理信道承載的傳輸信道是否處理完畢。每個傳輸信道處理完畢之后,把各個傳輸信道處理結果復用起來,成為編碼復用傳輸信道,再統一處理。依次處理每個物理信道,最后把所有的結果一起進行調制等處理。

與已有方案不同,很多用FPGA 實現的算法,如調制、擴頻、加擾都放在DSP 執行。通過分析協議,采用查表法可以用DS P 高效實現調制、擴頻和加擾,不會對DSP 產生過大負荷。

5 實驗結果

本物理層支持高速率數字信號采集。采集的信號,經過相應射頻測量算法計算,即可完成各種終端射頻指標測量。圖5 表示呼叫狀態下EVM測量結果。

圖5 呼叫狀態下EVM 測量

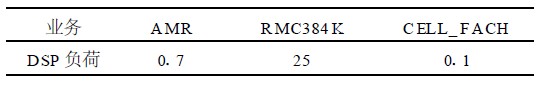

該物理層支持豐富的終端業務能力測量。表1列出了物理層支持的有代表性的業務,以及相應實測DSP 的負荷。

表1 物理層支持的業務

6 結 論

基于綜合測試儀物理層的雙重任務特點,本文詳細闡述了TD-SCDMMA綜合測試儀物理層的硬件構成, FPGA 和DSP程序設計。大部分任務采用全DSP 實現,具有開發周期短的優點。

物理層在863 項目大力支持的綜合測試儀項目中是實現難點,該方案發揮了重要作用,順利通過了專家組驗收。該綜合測試儀已經被無線電管理委員會、MTNET和眾多廠商廣泛采用,推動了TD產業發展。

目前,在該方案基礎之上,經過改進,系統仿真器進一步具備了支持HSDPA 終端測試的能力。今后將繼續研究設計以支持終端協議一致性測試和多模終端測試。

評論