改搭可編程FPGA SoC ADAS系統(tǒng)性故障銳減

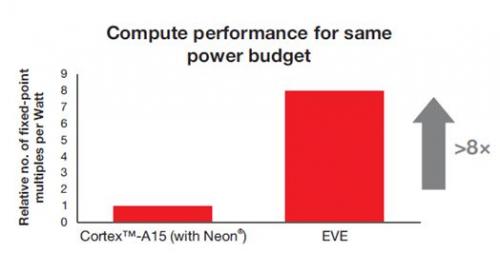

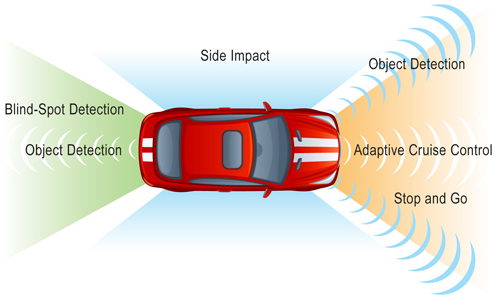

基于雷達(dá)(RADAR)和攝影機(jī)設(shè)計(jì)的應(yīng)用正大舉進(jìn)駐汽車駕駛安全領(lǐng)域。最初,自適應(yīng)巡航控制和道路偏離警報(bào)等先進(jìn)駕駛輔助系統(tǒng)(ADAS)只是一些非常便利的功能,而現(xiàn)在,它們在車輛控制上扮演更積極主動的角色,支持實(shí)現(xiàn)車道維持輔助(LKA)等功能。以前的高性能中央處理器(CPU)被認(rèn)為是最適合這些應(yīng)用的組件,但車廠須要綜合考慮運(yùn)算性能和低功率消耗,這促使工程師轉(zhuǎn)向采用現(xiàn)場可編程門陣列(FPGA)組件。

本文引用地址:http://www.104case.com/article/201808/387641.htmADAS須要滿足特殊的功能安全要求。在2011年,ISO發(fā)布針對載重3.5噸以下客車的ISO26262標(biāo)準(zhǔn),以降低系統(tǒng)出現(xiàn)故障后造成危險(xiǎn)的風(fēng)險(xiǎn)。這個標(biāo)準(zhǔn)要求采用嚴(yán)密的設(shè)計(jì)過程,在應(yīng)用執(zhí)行過程中探測隨機(jī)硬件故障,以減少系統(tǒng)性故障。

提升ADAS功能安全 FPGA SoC受青睞

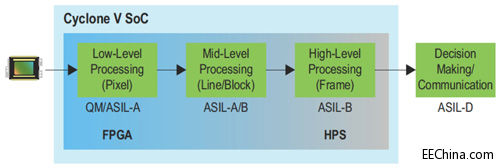

應(yīng)用開發(fā)人員定義了專門的安全目標(biāo),針對每個目標(biāo)分配相應(yīng)的汽車安全完整性等級(ASIL)。對于應(yīng)用中最高級別的ASIL-D,通常定義了每一個組件從開發(fā)直至運(yùn)作到壽命終了時應(yīng)滿足的要求。圖1顯示了從客戶需求角度來看,ADAS應(yīng)符合的ASIL目前的范圍。

圖1 ADAS所需ASIL規(guī)范等級

ASIL-B是市場上的最低級別,而某些應(yīng)用則要求采用ASIL-D,以支持某些功能。越來越多的ADAS應(yīng)用對ASIL有更嚴(yán)格的要求。在某些具體實(shí)現(xiàn)中,組件的通用ASIL或者項(xiàng)目(系統(tǒng))等級都會帶來不必要的復(fù)雜度,影響開發(fā)成本和進(jìn)度。分析系統(tǒng)概念,得出安全概念和要求后,還可以把應(yīng)用分成幾種不同的步驟,具有不同的ASIL,如此一來,系統(tǒng)設(shè)計(jì)則可更容易實(shí)現(xiàn),而且實(shí)現(xiàn)的效率更高。

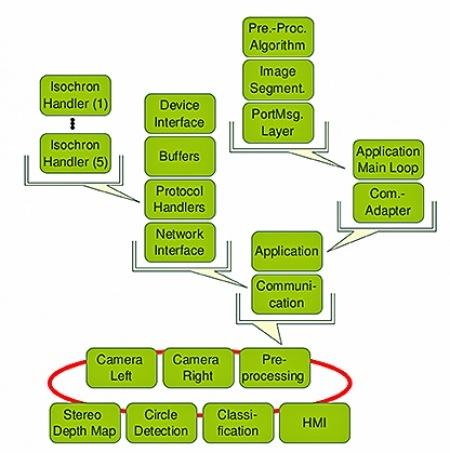

例如,前方攝影機(jī)應(yīng)用使用ADAS中常見的一個影像傳感器,如圖2顯示的高階結(jié)構(gòu)圖。一個影像傳感器連接至圖像處理器,該處理器可以是Altera Cyclone FPGA系統(tǒng)單芯片(SoC)或其他方案。訊號處理鏈路和數(shù)據(jù)流被分成四個部分。首先,透過把影像變換成更實(shí)用的表現(xiàn)方式,在像素層級上進(jìn)行底層處理。然后,對影像或者區(qū)塊圖像進(jìn)行中間層級處理,使用相應(yīng)的算法,提取出邊緣等特征。下一步,則會進(jìn)行高階處理,提取出每一個圖幀的數(shù)據(jù),探測目標(biāo)并進(jìn)行分類。然后,系統(tǒng)會追蹤目標(biāo),如果需要采取措施,則與煞車或者轉(zhuǎn)向引擎控制單元(ECU)進(jìn)行通訊。

圖2 高階單一前方攝影機(jī)ADAS

除了能夠在FPGA上非常高效率的實(shí)現(xiàn)底層和中間層級處理,用戶也可以在Cyclone V系列FPGA SoC硬式核心處理器系統(tǒng)(HPS)的Cortex-A9等處理核心實(shí)現(xiàn)某些中間層級處理。高階處理主要是句柄,可以映像到HPS中的一個或者兩個Cortex-A9上。處理鏈路的最后一步是目標(biāo)追蹤和判斷,可以在外部微控制器(MCU)上完成這一個步驟。

在整個處理過程中,工程師可將輸入數(shù)據(jù)進(jìn)行簡化,以得到更有意義的數(shù)據(jù),數(shù)據(jù)減少意味提高安全臨界值。因此,底層實(shí)現(xiàn)可以分成質(zhì)量管理(QM)或底層ASIL(例如ASIL-A)。會這樣做的原因是因?yàn)閱我粋€像素期間出現(xiàn)的故障對后續(xù)算法的性能影響很小,因此可以忽略。在這個例子中,假設(shè)中間層級處理符合ASIL-A或ASIL-B,識別目標(biāo)并進(jìn)行分類的高階處理功能應(yīng)符合ASIL-B。對目標(biāo)進(jìn)行分類后,會產(chǎn)生目標(biāo)表,并提供給微控制器,進(jìn)行目標(biāo)追蹤和判斷。這是訊號鏈路最關(guān)鍵的部分,我們認(rèn)為它應(yīng)該符合ASIL-D,這對汽車的行為有直接影響。

實(shí)現(xiàn)分級安全處理 FPGA兼顧設(shè)計(jì)可靠度/效率

在這類應(yīng)用中,最好對數(shù)據(jù)流進(jìn)行更全面的分析,每一個層級的安全臨界定義對整個系統(tǒng)的性能會產(chǎn)生直接影響。對前面運(yùn)算層級有太高的安全要求會導(dǎo)致難以滿足系統(tǒng)性能目標(biāo),而且對系統(tǒng)整體安全的影響很小。不過,處理鏈路底層也會出現(xiàn)故障,對系統(tǒng)安全功能產(chǎn)生較大的影響,例如,底層處理功能的永久故障會導(dǎo)致高層上的數(shù)據(jù)永久損害,透過合理性檢查很容易探測到這類故障,對系統(tǒng)性能的影響相對較小。

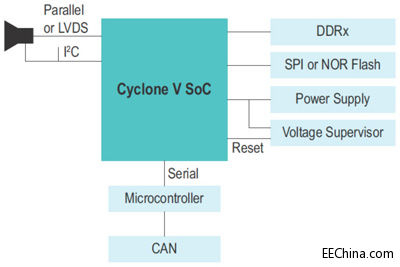

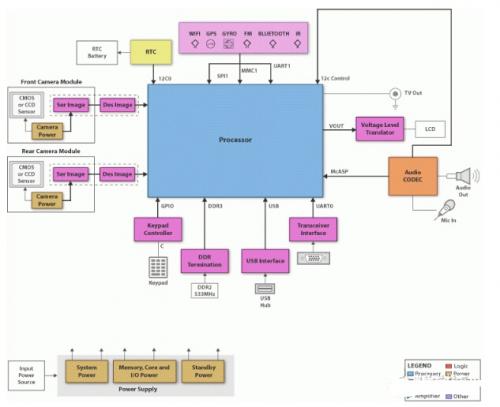

圖3顯示單一前方攝像機(jī)系統(tǒng)實(shí)例的高階結(jié)構(gòu)圖。由一個外部電源管理電路為Cyclone V SoC提供電源,當(dāng)供電電壓不在額定運(yùn)作范圍內(nèi)時,單獨(dú)的電壓監(jiān)控功能會產(chǎn)生重置,外部非揮發(fā)性內(nèi)存連接至四路串行周邊接口(Quad SPI)模塊,系統(tǒng)啟動過程中加載應(yīng)用程序,配置FPGA時會使用這些模塊。我們使用雙倍數(shù)據(jù)率(DDR)內(nèi)存來執(zhí)行應(yīng)用程序代碼、儲存數(shù)據(jù)和影像圖幀,透過SPI連接外部微控制器,進(jìn)行目標(biāo)探測和最終判斷,并利用控制器局域網(wǎng)絡(luò)(CAN)接口與汽車底盤的其他部分進(jìn)行通訊。

圖3 單一前方攝影機(jī)系統(tǒng)實(shí)例

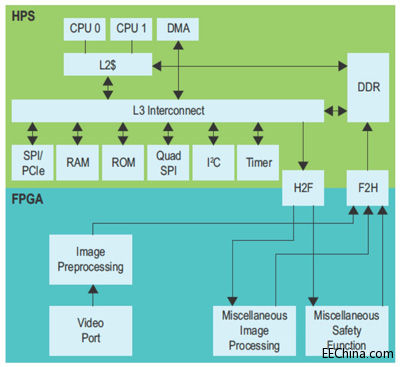

此應(yīng)用所使用的圖像處理器模塊如圖4所示。視訊端口接收來自影像傳感器的數(shù)據(jù),將其傳送至圖像處理模塊,這一個模塊相當(dāng)于底層圖像處理層級,在這個例子中,數(shù)據(jù)透過圖像處理模塊后,通過FPGA至HPS(F2H)橋接被寫入到DDR內(nèi)存中,也可以傳送至下一層級,實(shí)現(xiàn)的效率更高。第二級是中間層級處理,由各種圖像處理模塊來完成,透過HPS至FPGA(H2F)橋接讀出以前儲存在DDR內(nèi)存中的數(shù)據(jù),再次將其寫入到DDR內(nèi)存中。在這個例子中,由HPS完成高階處理層級。

圖4 Cyclone V SoC電路架構(gòu)圖

發(fā)揮可編程效益 FPGA全方位探測系統(tǒng)故障

接下來的段落將說明用于探測設(shè)計(jì)中,不同區(qū)域是否有故障的診斷功能。一些診斷功能能夠探測到永久故障,而有的只能探測到暫時性故障,也有的能探測各種故障。暫時性故障是一種出現(xiàn)后又消失的故障,對于這一類情形,設(shè)計(jì)人員應(yīng)考慮實(shí)現(xiàn)某些功能時內(nèi)存中出現(xiàn)的故障,以及實(shí)現(xiàn)功能時邏輯中可能出現(xiàn)的故障。

在應(yīng)用軟件使用影像傳感器之前,工程師應(yīng)對其進(jìn)行配置,在應(yīng)用程序執(zhí)行過程中不斷修改配置以適應(yīng)不同的光線條件。影像傳感器對于應(yīng)用操作非常關(guān)鍵,因此,建議在容錯時間間隔(FTTI)期間對其配置至少進(jìn)行一次檢查,這并不一定能覆蓋傳感器所有可能的故障,但可以管理好配置緩存器組(表1)。

評論