一文看懂DDS原理、混疊、幅度調(diào)制

注意,DAC輸出(濾波前)的幅度響應(yīng)跟隨著一個sin(x)/x響應(yīng),在時鐘頻率及其整數(shù)倍時,該值為零。歸一化輸出幅度A(fO)的精確計算公式如下:

其中,fO為輸出頻率,fc為時鐘頻率。

出現(xiàn)該滾降的原因是由于DAC輸出并非一系列零寬脈沖(和最佳重新采樣器中一樣),而是一系列矩形脈沖,寬度等于更新速率的倒數(shù)。sin(x)/x響應(yīng)的幅度比奈奎斯特頻率低3.92 dB(DAC更新速率的1/2)。實際上,抗混疊濾波器的傳遞函數(shù)可用來補償sin(x)/x滾降,使整體頻率響應(yīng)相對平坦,達到最大輸出DAC頻率(一般為1/3更新速率)。

另一個重要的考慮因素在于,和基于PLL的系統(tǒng)不同,DDS系統(tǒng)中的基本輸出頻率高階諧波會因混疊而折回至基帶。這些諧波無法通過抗混疊濾波器去除。例如,如果時鐘頻率為100 MHz,輸出頻率為30 MHz,則30 MHz的第二個諧波會出現(xiàn)在60 MHz(帶外),但也會出現(xiàn)在100 – 60 = 40 MHz(混疊成分)。同樣,第三個諧波(90 MHz)會出現(xiàn)在帶內(nèi),頻率為100 – 90 = 10 MHz,第四個諧波出現(xiàn)在120 – 100 MHz = 20 MHz。高階諧波也會落在奈奎斯特帶寬內(nèi)(直流至fc/2)。前4個諧波的位置如圖所示。

用作ADC時鐘驅(qū)動器的DDS系統(tǒng)

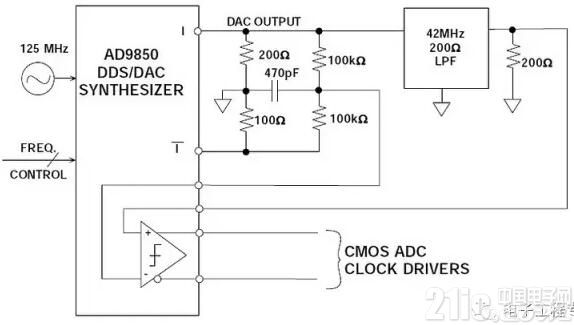

DDS系統(tǒng)(如AD9850)可以提供產(chǎn)生ADC采樣時鐘的出色方法,尤其適合ADC采樣頻率必須受到軟件控制,且鎖定至系統(tǒng)時鐘的情況(參見圖6)。DAC輸出電流IOUT驅(qū)動200 Ω、42 MHz的低通濾波器,源和負載阻抗端接,等效負載為100 Ω。濾波器可以消除42 MHz以上的雜散頻率成分。經(jīng)過濾波的輸出可以驅(qū)動AD9850內(nèi)部比較器的一個輸入端。DAC補償輸出電流可以驅(qū)動100 Ω的負載。位于兩個輸出之間的100 kΩ電阻分壓器輸出經(jīng)過去耦,可以產(chǎn)生參考電壓以供內(nèi)部比較器使用。

比較器輸出有2 ns的上升和下降時間,可以產(chǎn)生與TTL/CMOS邏輯電平兼容方波。比較器輸出邊緣的抖動小于20 ps rms。輸出和補償輸出均可按要求提供。

圖6:將DDS系統(tǒng)用作ADC時鐘驅(qū)動器

在圖6所示的電路中,40 MSPS ADC時鐘的總輸出均方根抖動為50 ps rms,由此產(chǎn)生的信噪比下降在寬動態(tài)范圍應(yīng)用中必須加以考慮。

DDS系統(tǒng)中的幅度調(diào)制

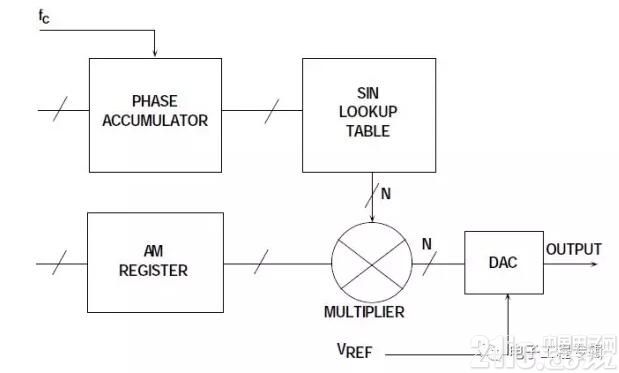

DDS系統(tǒng)中的幅度調(diào)制可以通過在查找表和DAC輸入之間放置數(shù)字乘法器來實現(xiàn),如圖7所示。調(diào)制DAC輸出幅度的另一種方法是改變DAC的參考電壓。在AD9850中,內(nèi)部參考控制放大器的帶寬約為1 MHz。這種方法在輸出幅度變化相對較小的情況下非常有效,只要輸出信號不超過+1 V的規(guī)格即可。

圖7:DDS系統(tǒng)中的幅度調(diào)制

DDS系統(tǒng)中的無雜散動態(tài)范圍考慮

在大多數(shù)DDS應(yīng)用中,首要考慮因素是DAC輸出的頻譜純度。遺憾的是,該性能的測量、預(yù)測和分析十分復(fù)雜,涉及大量相互作用的因素。

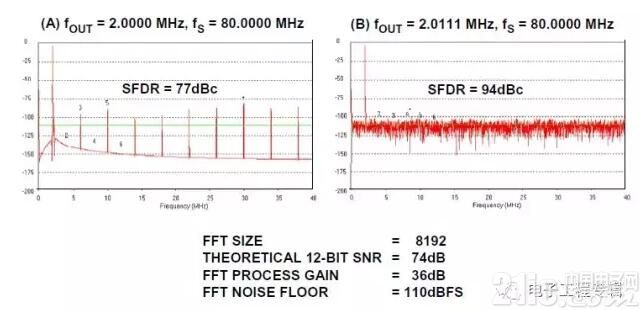

即便是理想的N位DAC,也會在DDS系統(tǒng)中產(chǎn)生諧波。這些諧波的幅度主要取決于輸出頻率與時鐘頻率的比值。原因在于,DAC量化噪聲的頻譜成分會隨著該比值的變化而變化,雖然其理論均方根值仍等于q/√12(其中q是LSB的權(quán)重)。“量化噪聲表現(xiàn)為白噪聲,在奈奎斯特帶寬內(nèi)均勻分布”這條假設(shè)在DDS系統(tǒng)中并不適用(這條假設(shè)在ADC系統(tǒng)中更為適用,因為ADC會給信號增加一定的噪聲,從而“擾動”量化誤差或使其隨機化。但是,依然存在一定的相關(guān)性)。例如,如果DAC輸出頻率精確設(shè)置為時鐘頻率的約數(shù),則量化噪聲會集中在輸出頻率的倍數(shù),也就是說,主要取決于信號。如果輸出頻率稍有失調(diào),量化噪聲會變得更加隨機,從而改進有效SFDR。

圖8說明了上述情況,其中4096 (4k)點FFT基于理想12位DAC中數(shù)字化生成的數(shù)據(jù)計算得出。左側(cè)圖表(A)中,所選的時鐘頻率和輸出頻率的比值恰好等于40,獲得的SFDR約為77 dBc。右側(cè)圖表中,比例稍有失調(diào),有效SFDR增至94 dBc。在這一理想情況下,只是略微改變了頻率比,SFDR就改變了17 dB。

圖8:采用4096點FFT時,時鐘與輸出頻率比值對理論12位DAC SFDR的影響

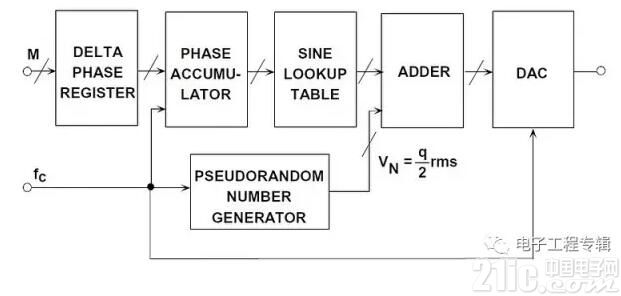

因此,通過仔細選擇時鐘與輸出頻率,就可以獲得最佳SFDR。但是,在有些應(yīng)用中,這點可能難以實現(xiàn)。在基于ADC的系統(tǒng)中,增加少量的隨機噪聲至輸入就可能使量化誤差隨機化,并且減少這種效應(yīng)。DDS系統(tǒng)中也可以實現(xiàn)同樣的效果,如圖9所示。偽隨機數(shù)字噪聲發(fā)生器輸出先增加至DDS正弦幅度字,然后再載入DAC。數(shù)字噪聲的幅度設(shè)置為1/2 LSB左右。這樣就能實現(xiàn)隨機化過程,代價是整體輸出本底噪聲會略微增加。但是,在大多數(shù)DDS系統(tǒng)中,有足夠的靈活性可以選擇不同的頻率比,因此不需要擾動。

圖9:向DDS系統(tǒng)注入數(shù)字擾動以使量化噪聲隨機化并提高SFDR

評論