Achronix高度可編程的嵌入式FPGA解決方案

作者/ Achronix Semiconductor 戰略規劃和業務發展高級總監 Mike Fitton

本文引用地址:http://www.104case.com/article/201806/381007.htm當前我們正處于蜂窩連接的一個轉換時期,無所不在的無線通信這一未來正在到來,而且推動了全世界移動電話擁有量達到了75億臺(數據來自世界銀行)。包括中國許多地區也是一樣,每百人的移動電話擁有量已經大大超過了固定電話的擁有量。

展望未來十年,5G的發展將會使無線基礎設施將會變得更加的無所不在,甚至還將與我們生活的方方面面更緊密地結合在一起。5G在繼續推進以前的蜂窩移動標準持續推動帶寬擴展這種范式的基礎上,還將推動一系列新的設備和應用模式的產生。

由此帶來關鍵的趨勢包括:

1)為增強移動寬帶(eMBB)和其他應用提供擴展的帶寬,特別是將推動瞬時可用帶寬提升到目前吞吐量的10倍。

2)連接到更多更多的設備,這將得益于物聯網對蜂窩通信連接需求的持續增長。現在的預測是到2020年將有500億臺通過蜂窩移動通信網絡連接的設備,雖然現有標準可以滿足這些需求的大部分,但是在3GPP Release 16中的大規模機器類別通信(mMTC)的現有規范將發揮更大的推動作用。

3)新的應用模式將廣泛興起,從而激發對移動設備以及蜂窩移動通信基礎設施的新要求,例如mMTC支持的低帶寬、低功耗、長電池巡航時間的物聯網應用,以及高帶寬、低延遲的新一代車聯網通信。

4)信息的邊緣解析以及移動邊緣計算,這和現有網絡世界中數據由中心化處理轉向更高效、更低延遲的邊緣處理是一樣的。

盡管前景讓人興奮不已,但是5G對吞吐量、可靠性、普及性和邊緣計算的要求,正在為現有的通信基礎設備帶來巨大的、新的挑戰,包括:

1)對低延遲和更高數據吞吐量不斷增加的需求,使這些解決方案為了高效處理數據而轉向一種更加優化的數據流水線,例如傳輸時間間隔(TTI)這一重要的時間單位將從1ms縮短到0.2ms。

2)應用模式和需求的不斷增加意味著不可能再是“一種模式打天下”,這將需要一種基于產品或技術組合的模式,也就是說需要在不同的部署模式間盡可能地實現設計重用的最大化,如從小基站、到宏基站再到Cloud RAN。

3)特別需要的是用靈活性來滿足新的和未來出現的應用模式,更直白地說就是大家都期望這些解決方案應該做到面向未來不過時,可以適應來自最終客戶和運營商的新的和未預見到需求。更進一步地說明就是:這種能夠可編程的、面向未來的解決方案可以支持改善上市時間。因而在ASIC或SoC流片之前不再必須完全固定設計,在規范最終確定時可能產生的變化將由可編程硬件的方式來應對。

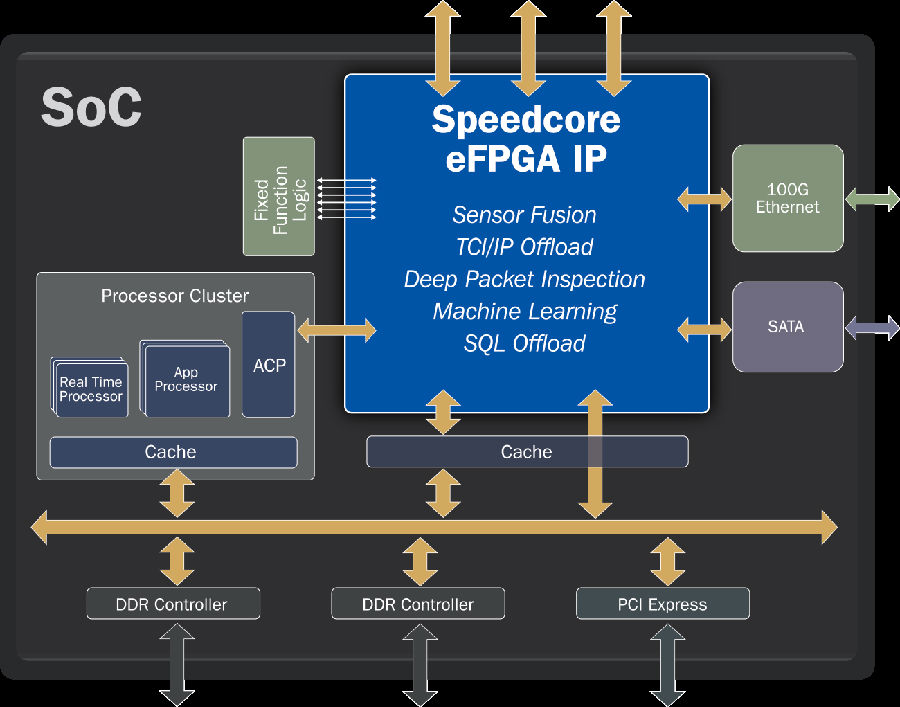

Achronix高度可編程的嵌入式FPGA解決方案

諸如Achornix的Speedcore? eFPGA這類高度可編程的嵌入式FPGA解決方案可為5G系統帶來更快的上市時間。例如,沒有必要把一款SoC的流片推遲到5G標準最終確立之后,后期發生的需求變化可以用軟件或者可編程硬件來解決。這是一種非常強大的優勢,可以用來面對5G早期部署中持續的、甚至不斷增加的壓力,以及一直不斷會發生的新標準融合。

與一款獨立的FPGA芯片相比,Speedcore eFPGA提供了獨有的優勢:

1)更高的性能。一個eFPGA是通過并行的接口直接連接到(沒有I/O緩沖器)ASIC上的,從而提供了顯著更高的數據吞吐量,而延遲可以用一位數的時鐘周期來計算。延遲在需要對快速變化的數據流情況進行實時反應時是至關重要的。

2)低功耗:

在一款獨立的FPGA芯片中,可編程的I/O線路占據了總功耗的一半;而一款eFPGA采用直接線路連接到SoC,從整體上消除了大量的可編程I/O緩沖器。

一款eFPGA可以根據最終應用的要求來準確地選擇規模大小,而且生產工藝技術也可以用來對性能和功耗之間的平衡進行微調。

3)更低的系統成本:

一款eFPGA的晶粒面積比一款等效的獨立FPGA面積小很多,這是因為可編程的I/O緩沖器、不需要的DSP和存儲單元、以及超出預期的查找表和寄存器都可以被消除掉。

4)更高的系統可靠性和良率。將FPGA功能集成到一款ASIC中,可以改善系統級的信號完整性,并消除了因為在PCB板上安裝獨立FPGA芯片所帶來的可靠性和良率損失。

評論