Mentor Tessent VersaPoint 測試點技術(shù)幫助 Renesas 降低成本和改進質(zhì)量

Mentor, a Siemens business 今日宣布在 Tessent? ScanPro 和 Tessent LogicBIST 產(chǎn)品中推出 VersaPoint? 測試點技術(shù),這些產(chǎn)品仍舊符合 ISO 26262 質(zhì)量認證要求。VersaPoint 測試點技術(shù)不僅能夠降低制造測試成本,還能改進在系統(tǒng)測試的質(zhì)量——對于汽車和其他行業(yè)的高質(zhì)量 IC 而言,這兩條要求至關(guān)重要。Mentor 還宣布 Renesas Electronics 已經(jīng)在該公司的汽車 IC 中采用了 VersaPoint 技術(shù),以解決安全關(guān)鍵的測試要求,從而達到汽車安全完整性級別 (ASIL) C 和 D 認證標(biāo)準(zhǔn)。

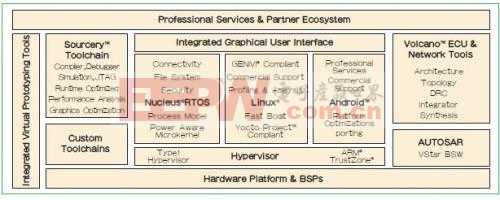

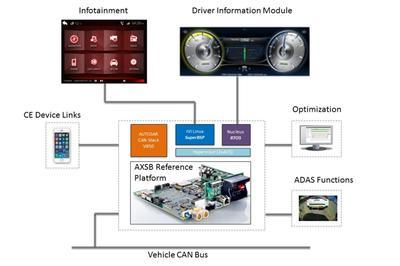

本文引用地址:http://www.104case.com/article/201711/371049.htm汽車 IC 中的數(shù)字電路通常混合采用片上壓縮/ATPG 和邏輯內(nèi)建自測 (LBIST) 技術(shù)來進行測試,從而讓制造測試達到極高的缺陷覆蓋率,進而實現(xiàn)在系統(tǒng)測試和上電自測試。

測試點是用于改進測試效果的專用設(shè)計結(jié)構(gòu)。傳統(tǒng)的 LBIST 測試點通過解決 IC 中的“隨機模式障礙”來改進測試結(jié)果。Mentor 近期專門針對片上壓縮/ATPG 的混合使用開發(fā)了測試點,相對于僅使用片上壓縮的情況,可將 ATPG 模式數(shù)減少 2-4 倍。Tessent VersaPoint 測試點技術(shù)組合了這些技術(shù),并在它們的基礎(chǔ)上進行了改進。

“為了提供業(yè)界領(lǐng)先的汽車 IC 產(chǎn)品,Renesas 使用測試點來幫助達到嚴(yán)格的 IC 測試要求,”Renesas Electronics Corporation 汽車 SoC 業(yè)務(wù)部門副總裁 Hisanori Ito 說道。“利用 Tessent VersaPoint 測試點技術(shù),我們再也無需針對不同類型的 IC 使用單獨的解決方案。如此一來,只需通過制造和在系統(tǒng)測試,我們便能改進質(zhì)量并降低成本。簡化的 DFT 實施流程還可縮短開發(fā)周期,加快產(chǎn)品上市時間。”

與傳統(tǒng)的 LBIST 測試點相比,Tessent VersaPoint 技術(shù)可以提高 LBIST 測試覆蓋率。而與使用片上壓縮/ATPG 測試點相比,它還可以更好地減少 ATPG 模式數(shù)。這種技術(shù)是專為使用 Tessent 混合 ATPG/LBIST 技術(shù)的測試工程師而設(shè)計的,旨在降低測試成本、改進測試質(zhì)量,特別是針對面向汽車應(yīng)用的 IC 產(chǎn)品。

“隨著設(shè)計尺寸不斷增長,質(zhì)量要求變得更加嚴(yán)格,我們的客戶也一直在努力降低測試成本”,Mentor Tessent 產(chǎn)品系列營銷總監(jiān) Brady Benware 說道。“與此同時,市場對高可靠性應(yīng)用中的高效在系統(tǒng)測試的需求也在持續(xù)增長。借助 VersaPoint 測試點技術(shù),我們的客戶可以通過更有效的方法,同時滿足制造和在系統(tǒng)測試要求。”

評論