過孔——PCB設計信號失真的原因,不容小覷

【導讀】目前,數字設計系統的速度按GHz計,這個速度產生的挑戰遠比過去顯著。由于邊緣速率以皮秒計,任何阻抗不連續、電感或電容干擾均會對信號質量造成不利影響。盡管有各種來源會造成信號干擾,但一個特別而時常被忽視的來源就是過孔。

本文引用地址:http://www.104case.com/article/201710/365937.htm多年以來,工程師們開發了幾種方法來處理引起PCB設計中高速數字信號失真的噪音。隨著設計技術與時俱進,我們應對這些新挑戰的技術復雜性也日益增加。目前,數字設計系統的速度按GHz計,這個速度產生的挑戰遠比過去顯著。由于邊緣速率以皮秒計,任何阻抗不連續、電感或電容干擾均會對信號質量造成不利影響。盡管有各種來源會造成信號干擾,但一個特別而時常被忽視的來源就是過孔。

簡單過孔中的隱患

高密度互連(HDI)、高層數印刷電路板和厚背板/中間板中的過孔信號會受到更多抖動、衰減和更高誤碼率(BER)的影響,導致數據在接收端被錯誤解釋。

以背板和子卡為例。當遇到阻抗不連續時,焦點在于這些板子與母卡之間的連接器。通常情況下,這些連接器在阻抗方面非常匹配,不連續實際源自過孔。

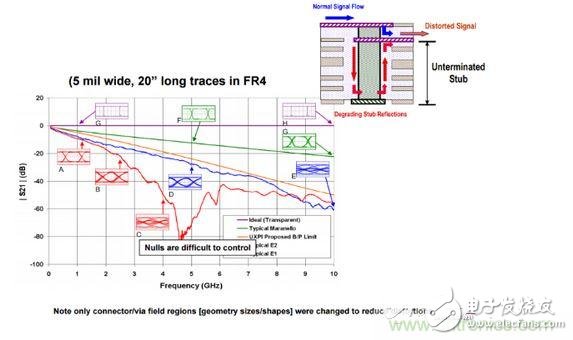

隨著數據速率的增加,由鍍通孔(PTH)過孔結構引起的失真量也會增加——通常以遠高于相關數據速率增量的指數級速率增加。例如,一個PTH過孔在6.25Gb/s時的失真通常比在3.125Gb/s時產生的失真大兩倍以上。

在底層和頂層出現的不需要的過孔殘段延伸層,使過孔顯示為較低的阻抗不連續性。工程師們克服這些過孔額外電容的一個方法是,將其長度最小化,從而減小其阻抗。這就是背鉆的由來。

長過孔殘段信號失真[1]

使用背鉆技術

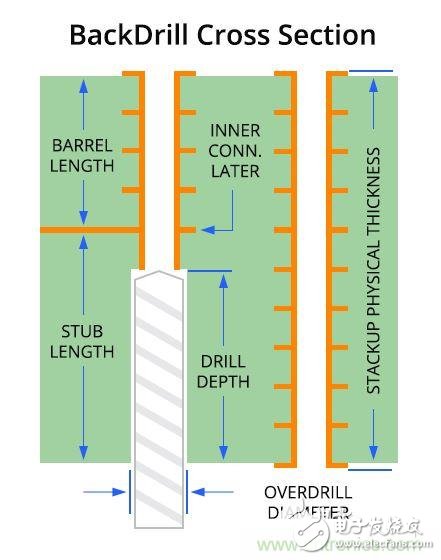

通過清除過孔殘段,背鉆已被廣泛認為是把通道信號衰減降到最低程度的簡單而有效的方法。該技術被稱為定深鉆孔,它采用傳統的數控(NC)鉆孔設備。同時,該技術可應用于任何類型的電路板,而不只是像背板一樣的厚板。

相對于原始過孔,背鉆法使用的鉆頭直徑稍大,以便移除不需要的導體殘段。該鉆頭通常比主鉆規格大8mil,但許多制造商都能滿足更嚴格的規格。

需要記住的是,距離走線與平面的間距需要足夠大,以保證背鉆程序不會穿透附近的走線和平面。為避免穿透走線和平面,建議間距為10mil。

一般而言,通過背鉆減少過孔殘段的長度有許多好處,包括:

按數量級降低確定性抖動,使得誤碼率更低。

通過改善的阻抗匹配降低信號衰減。

降低來自殘段的電磁干擾/電磁兼容性輻射,并增加通道帶寬。

降低共振勵磁模式和過孔間串擾。

以比順序層壓法更低的制造成本,將設計和布局影響降到最低。

背鉆橫截面

通過背鉆溝通設計意圖

隨著背鉆技術在高密度互連和高速設計應用中的頻繁使用,此方法也帶來了可靠性問題。其中一部分問題包括缺乏設計指南、制造公差、以及如何確保將設計意圖良好地傳達到制造單位。

那么,如何確保您的制造商擁有背鉆目標過孔和鍍通孔元件需要的所有信息?如何保持跟蹤整個設計過程中背鉆規格的多個級別?

其實需要的東西非常簡單:集成到設計規則中的簡單可視化配置工具,使您能為所選對象指定不同的背鉆配置。然后,就可以讓了解哪些過孔需要背鉆的軟件來幫您干活了。

評論