多核處理器會(huì)取代FPGA嗎?

有人認(rèn)為諸如圖形處理器(GPU)和TIlera處理器等多核處理器在某些應(yīng)用中正逐步替代現(xiàn)場(chǎng)可編程門陳列(FPGA)。理由是這些多核處理器的處理性能要高很多,例如,由于GPU起初主要負(fù)責(zé)圖形繪制,因此,其尤其善于處理單精度(SP)及(某種情況下)雙精度(DP)浮點(diǎn)(FP)運(yùn)算。TIlera的TILE設(shè)備當(dāng)前不支持硬件FP運(yùn)算,但要求進(jìn)行軟件模擬,且性能代價(jià)高昂。一般而言,FPGA亦是如此,設(shè)備通過(guò)利用多種資源來(lái)處理FP運(yùn)算問(wèn)題。達(dá)到可接受性能要求IP區(qū)塊需消耗多個(gè)門并要求深流水線技術(shù)。例如:當(dāng)前Tesla級(jí)GPU每秒最高可執(zhí)行1012次浮點(diǎn)運(yùn)算或1TFLOPS,而Xilinx Virtex-6設(shè)備則為150 GFLOPS。

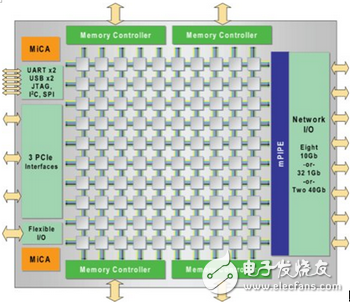

本文引用地址:http://www.104case.com/article/201710/365672.htm當(dāng)考慮到定點(diǎn)運(yùn)算時(shí),情況有所不同。新一代GPU在浮點(diǎn)速率相同的情況下可執(zhí)行整數(shù)運(yùn)算,例如:當(dāng)Virtex-6設(shè)備提高至500GOPS時(shí),GPU每秒可執(zhí)行1012次運(yùn)算或1TOPS。整數(shù)性能是TILE處理器的優(yōu)勢(shì)所在:8位數(shù)據(jù)時(shí),TILE-Gx(圖1)最高執(zhí)行能力為750GOPS,32位數(shù)據(jù)時(shí)為188GOPS。

FPGA能夠利用其并行及適應(yīng)多種算法的特性來(lái)獲得更加接近理論最大值的性能。但是,F(xiàn)PGA需要更大的硅片空間和更長(zhǎng)的開發(fā)時(shí)間來(lái)接近這些理論最大值。對(duì)于適應(yīng)于GPU硬件并行模式的算法,GPU已經(jīng)能夠達(dá)到峰值的20~30%。它們同樣具有合理的硅密度(40nm工藝,32nm研發(fā)中)和開發(fā)時(shí)間(通常只有數(shù)周,而FPGA則需幾個(gè)月)。TILEPro64處理器可提供FPGA相類似的適應(yīng)性和GPU相類似的可編程性,但是,由于其粗糙的任務(wù)級(jí)問(wèn)題分解特點(diǎn)使得其無(wú)法像FPGA和GPU那樣實(shí)現(xiàn)細(xì)粒度并行。

相關(guān)推薦

-

-

-

-

herbertwj | 2004-08-15

-

-

sandman555 | 2005-02-05

-

-

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

技術(shù)專區(qū)

- FPGA

- DSP

- MCU

- 示波器

- 步進(jìn)電機(jī)

- Zigbee

- LabVIEW

- Arduino

- RFID

- NFC

- STM32

- Protel

- GPS

- MSP430

- Multisim

- 濾波器

- CAN總線

- 開關(guān)電源

- 單片機(jī)

- PCB

- USB

- ARM

- CPLD

- 連接器

- MEMS

- CMOS

- MIPS

- EMC

- EDA

- ROM

- 陀螺儀

- VHDL

- 比較器

- Verilog

- 穩(wěn)壓電源

- RAM

- AVR

- 傳感器

- 可控硅

- IGBT

- 嵌入式開發(fā)

- 逆變器

- Quartus

- RS-232

- Cyclone

- 電位器

- 電機(jī)控制

- 藍(lán)牙

- PLC

- PWM

- 汽車電子

- 轉(zhuǎn)換器

- 電源管理

- 信號(hào)放大器

評(píng)論