利用AD7616的V型采樣實現準同步數據采集

作者/ 于克泳1 葉健2 1.亞德諾半導體技術(上海)有限公司(南京 210014)2.亞德諾半導體技術(上海)有限公司(上海 201210)

本文引用地址:http://www.104case.com/article/201709/364882.htm摘要:AD7616是ADI公司推出的一款16位數據采集系統(DAS)。對于多通道非同步采樣型ADC,本文采用“V型采樣+數據平均”的模式在AD7616的應用中實現了準同步采樣,同時基于AD7616的實驗結果也驗證了理論上的誤差分析。

1 AD7616簡介

AD7616是ADI公司推出的一款16位16通道數據采集系統(DAS) ,同一封裝內集成了兩個16位逐次逼近寄存器型(SAR)模數轉換器(ADC),支持對16個通道進行雙路同步采樣。AD7616的模擬輸入端為真雙極性輸入,每個通道的量程可獨立設置,有±10 V、±5 V或±2.5 V供選擇,同時輸入端具有±20V的箝位(CLAMP)保護,而且片內集成有抗混疊模擬濾波器。AD7616采用+5 V單電源供電,擁有1Msps的采樣速率并達到90dB的信噪比(SNR),輸入阻抗與采樣速率無關,恒定為1M?,因此無需外部的驅動電路及雙極性電源。

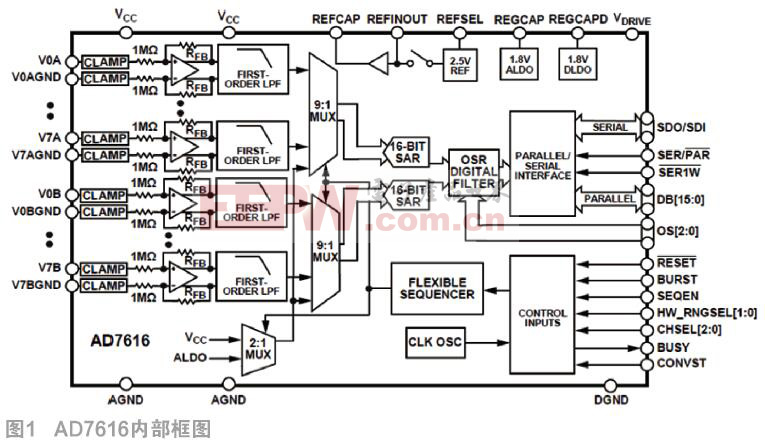

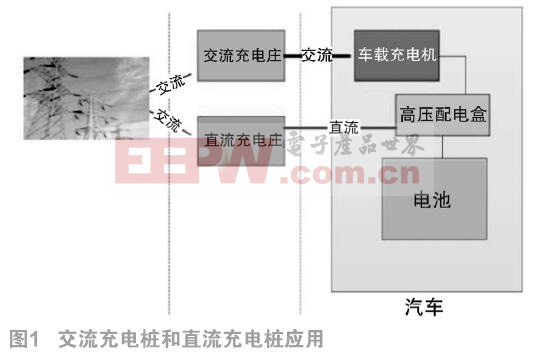

AD7616通過HW_RNGSEL[1:0]管腳進行選擇,工作在硬件模式或軟件模式。硬件模式下,AD7616由引腳進行配置。軟件模式下,AD7616支持并口或串口對內部的寄存器及靈活的序列器(Flexible Sequencer)進行配置,以獲得更多的功能。AD7616的內部框圖如圖1所示。

2 多通道準同步采樣

電力系統保護與測控的應用中,需要實時監測電網中多相的電壓和電流信號。為了滿足各種標準的精度要求,傳統的設計中通常都是對多路信號進行同步采樣,因此一般選用多通道同步采樣型的ADC,例如AD7865,AD7656-1,AD7606等都是典型的應用選擇。

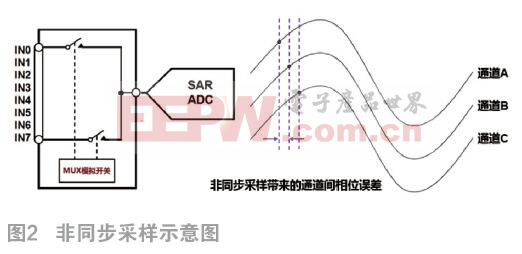

在某些需要低成本但精度要求不高的應用中,工程師嘗試采用一種“MUX模擬開關+單通道ADC”的設計方案,如圖2所示,利用模擬開關切換輸入通道,用單通道ADC循環對輸入信號進行采樣。由于多通道信號的非同步采樣,采樣點的間隔時間會導致通道間采樣的延遲,并由此帶來一定的相位誤差或相位失配,誤差的大小與多個因素相關,取決于輸入信號的頻率、幅值、采樣時刻信號的相位等。

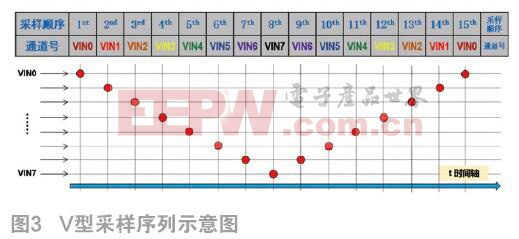

為了減少非同步采樣所帶來的通道間相位誤差,設計一種采樣序列,通道順序為“VIN0→VIN1→ VIN2→…→VIN6→VIN7→VIN6→… →VIN2→VIN1 →VIN0”,如圖3所示。由于采樣序列像一個大寫的字母“V”,我們不妨稱之為“V型采樣”模式。

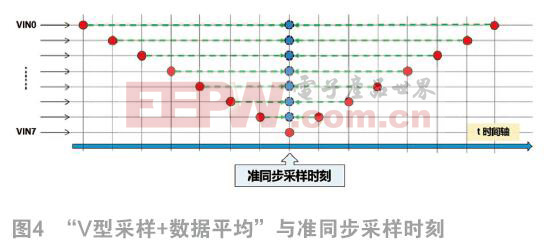

在圖3“V型采樣”配置下,VIN0 ~ VIN6的每個通道前后采樣兩次,而且采樣時刻在VIN7采樣時刻的兩側呈對稱分布。如果ADC的采樣間隔控制為等間距,當輸入信號為線性信號時,VIN0 ~ VIN6通道前后兩次采樣數據的平均值與在VIN7采樣時刻的結果是相同的,這就通過“V型采樣+數據平均”的方式實現了多通道間的準同步采樣,因此把VIN7的采樣時間點稱之為“準同步采樣時刻”,如圖4所示。

如果輸入信號為正弦波,采用“V型采樣+數據平均”的模式會帶來一定的誤差,但相比傳統的“MUX模擬開關+單通道ADC”非同步采樣模式而言,仍然可以大幅減少由于非同步采樣而帶來的通道間誤差。

3 “V型采樣+數據平均”的誤差分析

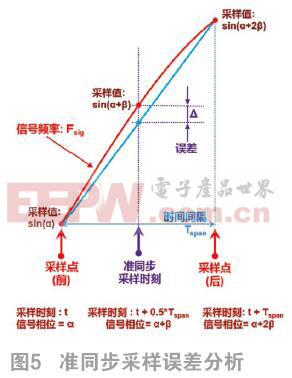

以正弦波為例,分析“V型采樣+數據平均”模式得到的平均值與準同步采樣時刻的采樣值之間誤差的大小。為了簡化分析,將輸入正弦波信號的幅值歸一化為1.0,并假定第一個采樣點時刻對應正弦波的相位為α,第二個采樣點時刻對應正弦波的相位為α+2β,參考圖 5所示。

1)前后兩個采樣點的數據平均值為:[sin(α) + sin(α+2β)] / 2 ;

2)準同步采樣時刻的正弦波實際值為:sin(α+β) ;

3)“V型采樣+數據平均”所帶來的誤差Δ為:

Δ = | [sin(α) + sin(α+2β)] / 2 - sin(α+β) | = | [1 - cos(β)] * sin(α+β) | ;

假定正弦波信號的頻率為Fsig,前后兩個采樣點之間的間隔為Tspan,前后兩個采樣點的相位差:2β = 2π * Fsig * Tspan ,帶入誤差Δ的公式:Δ = | [1 - cos(β)] * sin(α+β) | = | [1 - cos(π * Fsig * Tspan)] * sin(α+π * Fsig * Tspan) |。

由誤差Δ的表達式可以看出,一旦輸入正弦波信號的頻率Fsig及前后采樣點的時間間隔Tspan確定后,“V型采樣+數據平均”帶來的誤差僅與采樣點時刻所對應的正弦波相位α相關,并且誤差的最大值為 [1 - cos(π * Fsig * Tspan)]。

Tspan與ADC的采樣率Fsample及前后采樣點間的采樣次數N相關,即Tspan= N * (1 / Fsample) 。按照圖4的配置時,VIN0到VIN6每個通道的Tspan各不相同,其中VIN0通道的Tspan最大,誤差也將會最大。假定ADC的采樣率為1Msps且連續等間隔采樣,則相鄰兩次采樣的間隔為1μs,此時VIN0通道的Tspan = 14μs。以50Hz的電力系統應用為例,用Tspan = 14μs來計算“V型采樣+數據平均”所帶來誤差的最大值:

對于50Hz (基波),誤差最大值為:1 - cos(π * 50Hz * 14μs) < 0.01‰;

對于250Hz (5次諧波),誤差最大值為:1 - cos(π * 250Hz * 14μs) < 0.1‰;

對于2550 kHz (51次諧波),誤差最大值為:1 - cos(π * 2550Hz * 14μs) < 6.3‰;

從以上的計算結果來看,“V型采樣+數據平均”的模式完全可以滿足電力系統中保護和測控的精度要求。下一步將會用實驗的方法進行驗證。

4 AD7616準同步采樣的實現

在傳統的“MUX模擬開關+單通道ADC”模式中,ADC每收到一個CONVST啟動轉換控制信號后,僅完成一個通道的轉換。這就意味著,要通過“V型采樣+數據平均”的方式來實現“準同步采樣”,需要處理器 (Processor) 發出一系列的CONVST啟動轉換控制信號來實現多個通道的采樣序列,還要求處理器在每次啟動轉換之前讀出ADC的轉換數據,這既增加了處理器的負擔,又降低了系統的可靠性。

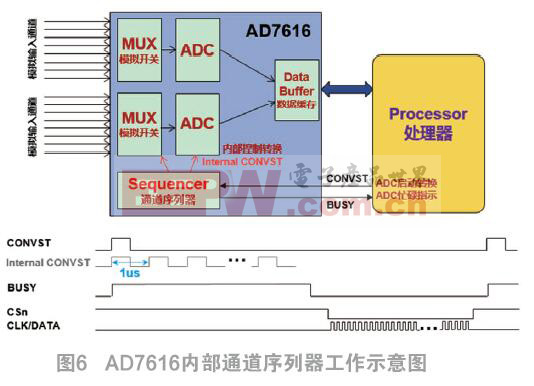

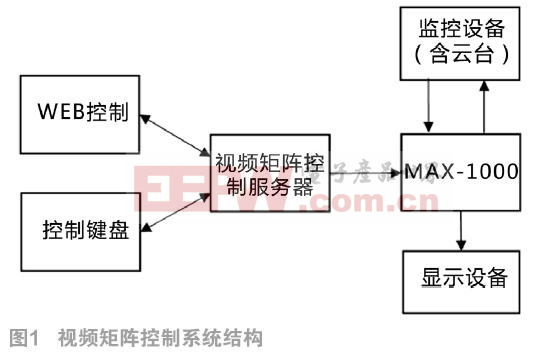

AD7616內部集成了MUX模擬開關和SAR型ADC,特別之處在于還集成有突發模式 (Burst Mode) 和靈活的通道序列器 (Flexible Sequencer) 。當AD7616工作在軟件模式 (Software Mode) 下,通過設置序列棧寄存器 (Sequencer stack registers) ,處理器只需要發出一個CONVST啟動轉換控制信號,AD7616將會自行完成所有設置通道的轉換,并把每一次的轉換結果放在數據緩存區中,待全部通道轉換完成后,AD7616將BUSY忙碌指示信號置低,等待處理器讀取所有通道的轉換結果。AD7616與處理器的連接及內部通道序列器的示意圖如圖6所示。

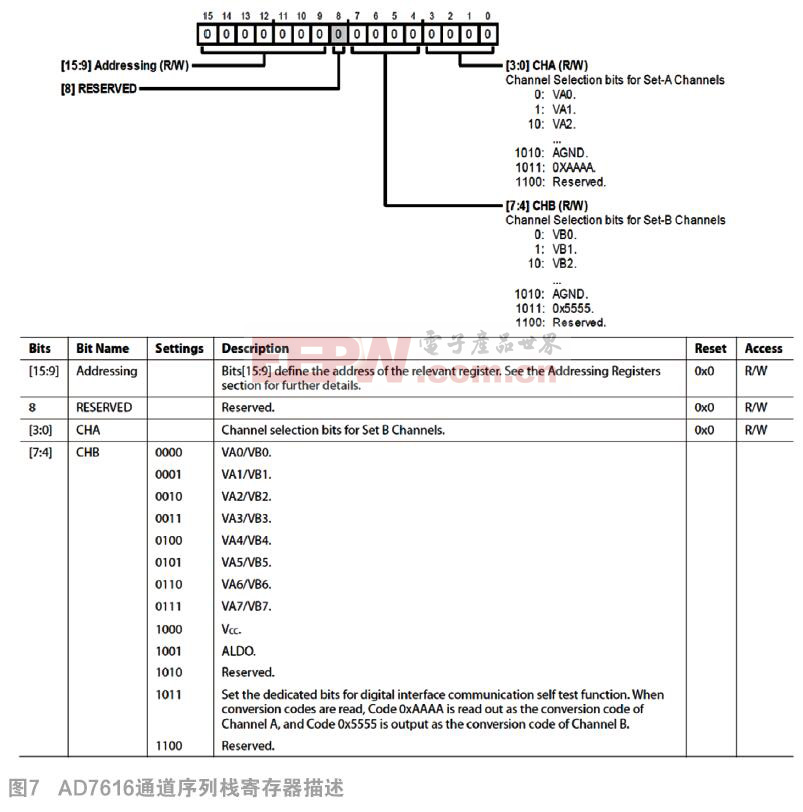

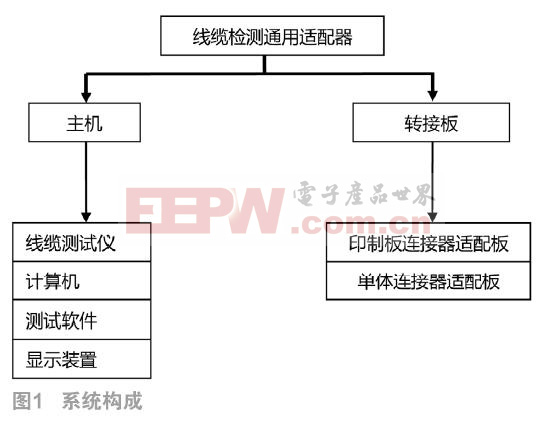

AD7616內部有兩個高速ADC核,稱為A核和B核。通道的序列棧寄存器地址為0x20到0x3F,總共包含32個寄存器,由用戶編程來實現1到32個預定的采樣序列。每個寄存器的寬度為16bit,其中 [7:4] bit定義為BSEL,用來設定B核的轉換通道, [3:0] bit定義為ASEL,用來設定A核的轉換通道。寄存器中的 [8] bit定義為SSREN,是通道轉換序列的結束控制位,如果設定為0,AD7616將調入下一個序列寄存器的設置進行轉換,如果設定為1,通道轉換序列在完成本次轉換后結束。轉換通道的選擇,除了模擬輸入通道VIN0 ~ VIN7,還可以選擇內部Vcc,內部LDO,或者固定輸出一個標志字0x5555或0xAAAA。AD7616序列棧寄存器的描述如圖7所示。

評論