使用QDR-IV設(shè)計(jì)高性能網(wǎng)絡(luò)系統(tǒng)之三

在本系列第二部分,我們探討了總線轉(zhuǎn)換、總線翻轉(zhuǎn)、地址奇偶校驗(yàn)等重要的總線問題。在第三也是最后一部分,我們將探討校正問題,其中包括矯正訓(xùn)練、控制/地址信號校正和讀寫校正,以及糾錯(cuò)碼(ECC)和QDR-IV存儲器控制器的設(shè)計(jì)建議。

校正訓(xùn)練序列

存儲器控制器和QDR IV較高的工作頻率意味著數(shù)據(jù)有效窗口很窄。QDR-IV器件支持“校正訓(xùn)練序列”,它可通過減少字節(jié)通道之間的偏差擴(kuò)大這個(gè)窗口,從而在控制器讀取存儲器的數(shù)據(jù)時(shí),增加時(shí)序余量。校正訓(xùn)練序列是賽普拉斯的QDR-IV SRAM的初始化過程的一部分。該訓(xùn)練序列通常被那些不支持內(nèi)置校正功能的應(yīng)用使用。

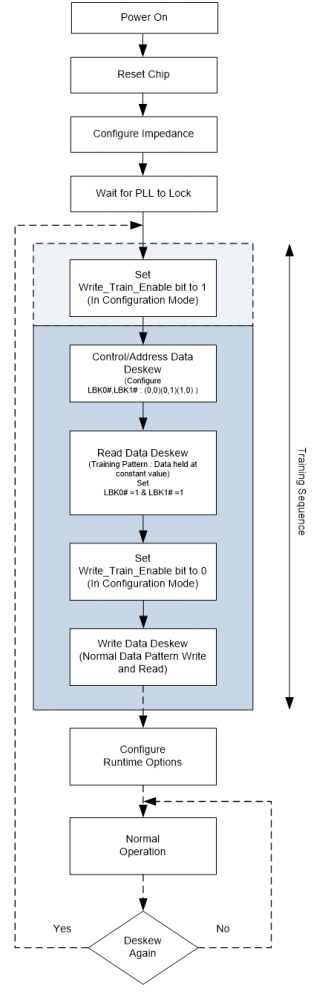

訓(xùn)練序列如圖8所示:

圖8. 校正訓(xùn)練序列

校正訓(xùn)練序列是初始化過程的一部分。對序列進(jìn)行加電和復(fù)位后,在配置模式下進(jìn)行操作的過程中,控制器必須立即設(shè)置選項(xiàng)控制寄存器中的Write_Train_Enable位(位的位置:7)。通過該操作,控制器可以避免在進(jìn)行訓(xùn)練序列前再次進(jìn)入配置模式。設(shè)置該位不會影響到校正訓(xùn)練序列,直到進(jìn)行讀取數(shù)據(jù)校正訓(xùn)練為止。

通過以下三個(gè)步驟,可以實(shí)現(xiàn)校正過程:

1.控制/地址校正

2.讀取數(shù)據(jù)校正

3.寫入數(shù)據(jù)校正

控制/地址校正

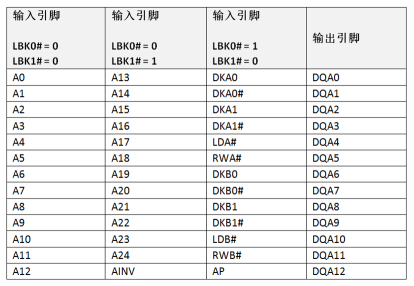

根據(jù)需要校正的信號,將LBK0#和LBK1#設(shè)為它們相應(yīng)的位值。請查看表12,了解環(huán)回信號的映射情況。39個(gè)輸入信號被環(huán)回到端口A上的數(shù)據(jù)引腳。根據(jù)LBK0#和LBK1#的狀態(tài),一次將13個(gè)輸入信號映射到DQA0-DQA12。

表12. 環(huán)回信號映射情況

DKA0、DKA0#、DKA1、DKA1#、DKB0、DKB0#、DKB1和DKB#1等時(shí)鐘輸入都是自由運(yùn)行的,并應(yīng)在訓(xùn)練序列中持續(xù)運(yùn)行。

通過使用輸入時(shí)鐘(CK/CK#)可在上升沿和下降沿上對每個(gè)輸入引腳進(jìn)行采樣。在輸出時(shí)鐘(QKA/QKA#)的上升沿上采樣的輸出值即為在輸入時(shí)鐘的上升沿上所采樣的值。在輸出時(shí)鐘(QKA/QKA#)的下降沿上采樣的輸出值即為在輸入時(shí)鐘的下降沿上所采樣的翻轉(zhuǎn)值。在這種模式下,數(shù)據(jù)翻轉(zhuǎn)無效,在進(jìn)行地址/控制環(huán)回訓(xùn)練過程中,CFG#信號將為高電平。

圖9. 環(huán)回訓(xùn)練框圖

如圖9所示,如果地址/控制信號未校正,DQA 上的信號(應(yīng)在訓(xùn)練期間保持高電平)將變?yōu)榈碗娖健T撔盘栟D(zhuǎn)換應(yīng)由驅(qū)動(dòng)信號的模塊捕獲,控制器則會對信號相應(yīng)進(jìn)行校準(zhǔn)。

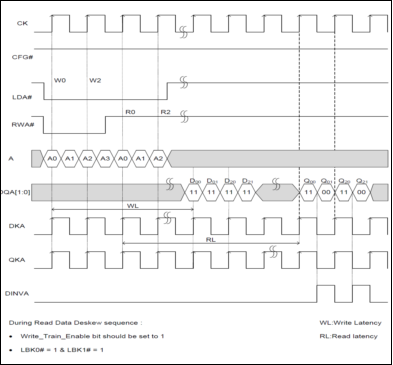

讀取數(shù)據(jù)校正

在該階段,地址、控制和數(shù)據(jù)輸入時(shí)鐘都已經(jīng)得到了校正。在讀取數(shù)據(jù)校正過程中,用于寫入存儲器內(nèi)的訓(xùn)練數(shù)據(jù)模型是一個(gè)常量值(D00,D01,D20,D21),如下面的波形框圖中顯示。在此訓(xùn)練序列中,LBK0#和LBK1#均被設(shè)置為1。

配置選擇控制寄存器時(shí),Write_Train_Enable 位將被設(shè)置為1。第一個(gè)和第二個(gè)數(shù)據(jù)突發(fā)均在同一個(gè)數(shù)據(jù)總線上被采樣的,但第二個(gè)數(shù)據(jù)突發(fā)則在寫到存儲器內(nèi)前完成采樣的。Write_Train_Enable 位不會對讀取數(shù)據(jù)周期產(chǎn)生任何影響。

將數(shù)據(jù)模型寫到存儲器內(nèi)后,標(biāo)準(zhǔn)的讀指令允許控制器訪問這些數(shù)據(jù),并會校正QK/QK#信號。當(dāng) Write_Train_Enable = 1 時(shí),在寫入過程中,DINVA/DINVB 將被忽略,在讀取過程中,它將始終切換。

如下面的讀取數(shù)據(jù)校正框圖中所示,寫入到存儲器內(nèi)的數(shù)據(jù)(D00、D01、D20、D21)全為1,相應(yīng)的讀取數(shù)據(jù)(Q00、Q01、Q20、Q21)則在1 和0 間切換。控制器必需捕捉到這些切換數(shù)據(jù)并進(jìn)行驗(yàn)證。否則,控制器需要一個(gè)精確的校準(zhǔn)來確認(rèn)讀取數(shù)據(jù)校正。

圖10. 讀取數(shù)據(jù)校正序列框圖

在讀數(shù)據(jù)校正序列中:

?設(shè)置Write_Train_Enable位為1

?LBK0# = 1 及LBK1# = 1

寫數(shù)據(jù)校正

此時(shí),地址、控制、時(shí)鐘和數(shù)據(jù)輸出都已經(jīng)得到了校正。執(zhí)行寫入數(shù)據(jù)校正序列前,先再次進(jìn)入配置模式,然后通過將相應(yīng)位設(shè)置為0來禁用Write_Train_Enable。

在正常工作模式下,使用讀指令后,通過使用存儲器的寫指令可校正寫數(shù)據(jù)。所校正的讀取數(shù)據(jù)路徑用于確認(rèn)器件是否已經(jīng)正確地接收到寫入數(shù)據(jù)。這樣使處理器/FPGA能夠校正下列與DK/DK#輸入數(shù)據(jù)時(shí)鐘有關(guān)的信號:DQA、DINVA、DQB和DINVB。

糾錯(cuò)碼(ECC)

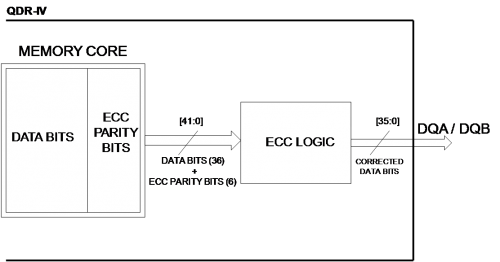

系統(tǒng)設(shè)計(jì)人員必需依賴片外糾錯(cuò)或冗余等技術(shù)提高可靠性。這些技術(shù)會增加PCB空間或處理時(shí)間方面的開銷。QDR-IV是一個(gè)單芯片解決方案,引入了片上糾錯(cuò)碼(ECC),從而節(jié)省了空間和成本,降低了設(shè)計(jì)復(fù)雜性。此外,它還降低了QDR-IV存儲器陣列的總軟失效率(SER)。該特性可應(yīng)用于數(shù)據(jù)總線寬度為x18和x36的選項(xiàng),并在SRAM中始終被啟用。ECC保護(hù)提供了單比特糾錯(cuò)(SEC)。

QDR-IV從輸入數(shù)據(jù)生成ECC奇偶校驗(yàn)位,并將它們存儲在存儲器陣列中。存儲器陣列包含用于存儲ECC奇偶校驗(yàn)的額外位。但是,不會將這些額外的內(nèi)部校驗(yàn)位用于外部引腳。

例如,圖11顯示的是x36器件的輸出數(shù)據(jù)邏輯框圖。36數(shù)據(jù)位需要6個(gè)ECC校驗(yàn)位;存儲器內(nèi)核會將42位(36個(gè)數(shù)據(jù)位 + 6個(gè) ECC校驗(yàn)位)傳輸?shù)紼CC邏輯內(nèi)。因此,ECC邏輯會提供已糾正的36位輸出數(shù)據(jù)。

無ECC位的QDR/DDR SRAM的SER故障率(FIT)通常為200 FIT/Mb。但帶有ECC時(shí),該數(shù)值將為0.01 FIT/Mb,提高了4個(gè)數(shù)量級。

圖11. 輸出數(shù)據(jù)邏輯(x36器件)

QDR-IV存儲器控制器的設(shè)計(jì)建議

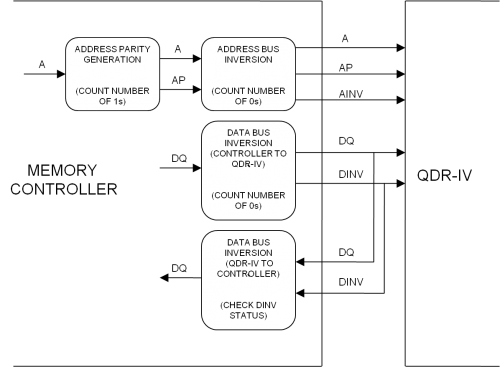

本節(jié)提供一些存儲器控制器啟用QDR-IV的地址奇偶校驗(yàn)和總線翻轉(zhuǎn)功能的設(shè)計(jì)建議。

存儲器控制器首先要根據(jù)地址總線生成地址奇偶。然后,需要在地址總線和地址奇偶位上進(jìn)行地址翻轉(zhuǎn)。

對于數(shù)據(jù)總線轉(zhuǎn)換,將數(shù)據(jù)發(fā)送給QDR-IV前,存儲器控制器需要計(jì)算每個(gè)DQ總線上的邏輯“0”的數(shù)量,以便生成相應(yīng)的DINV位(取決于數(shù)據(jù)總線翻轉(zhuǎn)條件)。

將數(shù)據(jù)發(fā)送給存儲器控制器時(shí),QDR-IV使用相同的數(shù)據(jù)總線翻轉(zhuǎn)邏輯。為了識別QDR-IV的接收數(shù)據(jù),控制器僅要檢查相應(yīng)DINV位的狀態(tài)。如果控制器接收DINV = 1,需要翻轉(zhuǎn)相關(guān)的數(shù)據(jù)總線;否則,保持接收到的數(shù)據(jù)位不變。

圖12顯示的是存儲器控制器的設(shè)計(jì)注意事項(xiàng)。

圖12. 存儲器控制器的設(shè)計(jì)注意事項(xiàng)

結(jié)束語

QDR-IV提供2132 MT/s的最大RTR,是市場上性能最高的標(biāo)準(zhǔn)化解決方案。憑借較高的RTR外加兩個(gè)雙向端口、ECC、總線翻轉(zhuǎn)、ODT、地址校驗(yàn)等差異化特性,它已成為網(wǎng)絡(luò)系統(tǒng)的首選解決方案。QDR-IV的優(yōu)勢還適用于其它需要較高RTR和信號完整性的系統(tǒng),如高性能計(jì)算和圖像處理系統(tǒng)。

評論