CPLD/FPGA在數字通信系統的應用

1 引言

本文引用地址:http://www.104case.com/article/201706/348938.htm

近年來,由于微電子學和計算機技術的迅速發展,給EDA技術行業帶來了巨大的變化。 HDL(hardware description language)硬件描述語言是一種描述電路行為的語言,是設計者和EDA工具的界面,設計者通過HDL描述自己的設計對象。目前比較流行的HDL主要有Verilog HDL、VHDL、AHDL等,其中Verilog HDL和VHDL因為適合標準化的方面而最終成為IEEE標準。但是Verilog HDL比VHDL更容易掌握,并且完成同一功能的Verilog HDL條數一般僅為VHDL的1/3,Verilog HDL 善于描述更低層設計包括結構級和物理層的設計,而VHDL設計技術很不直觀,設計人員需要有EDA編程基礎,經過半年左右的專業培訓才能掌握,所以用Verilog HDL的優越性高一些。作為學習HDL設計方法的入門和基礎,是一種值得大力推廣的硬件描述語言。

2 漢明碼的基本原理

漢明碼是一種能夠糾正一個錯碼且編碼效率較高的線性碼。在偶數監督碼中,無論信息位有多少,監督位只有一位,它使碼組中“1”的個數為偶數,在接收端解碼的時候,實際就是計算S= an-1⊕ an-2⊕。。。。⊕a0,若S=0,就認為無錯,若S=1,就認為有錯。上式稱為監督關系式,S為校正子。由于校正子S的取值只有這樣兩種,它只能代表有錯和無錯兩種信息,而不能指出錯碼的位置。如果監督位增加一位,即變成兩位,可能有四種組合:00,01,10,11,故能表示四種不同虛報許,若用其中一種表示無錯,則其余三種就有可能用來指示一位錯碼 的3種不同位置,同理,r個監督關系式就能指示一位錯碼的(2r-1)個可能位置.一般說來,若碼長為n,信息位數為k,則監督位數r=n-k.如果希望用r個監督位夠造出r個監督關系式來指示一位錯碼的n種可能位置,則要求

2r-1≥n ; 2r≥k+r+1;

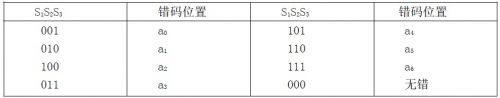

設分組碼(n, k)中k=4.為糾正一位錯碼,要求監督位數r≥3.若取r=3,則n= k+r=7.我們用a6a5a4…a0表示7個碼元,用S1S2S3表示三個監督關系式中的校正子,則S1S2S3的值與錯碼位置的關系如下表.

由表可知,僅當一錯碼位置在 a2 a4 a5 a6時,校正子S1為1,否則S1為0.這就意味著a2 a4 a5 和a6 構成偶數監督關系

S1= a2 ⊕ a4⊕ a5⊕a6

同理

S2= a1 ⊕ a3⊕a5⊕a6

S3= a0 ⊕a3⊕a4⊕a6

在發送端編碼時,信息位a6 a5 a4和 a3 的值決定于輸入信號,因此它們是隨機的。監督位a2 a1 和 a0 應根據信息位的取值按監督關系來確定,即監督位應使上三式中的S1S2S3的值為零。

a2⊕a4⊕a5⊕a6=0

a1⊕a3⊕a5⊕a6 =0

a0⊕a3⊕a4⊕a6=0

有上式移項運算,解出監督位

a2= a4⊕a5⊕a6

a1= a3⊕a5⊕a6

a0= a3⊕a4⊕a6

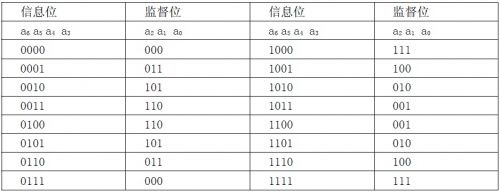

根給定信息位后,可直接計算出監督位,如下表

接收到每個碼組后,先按上式計算出S1 S2 和S3 ,再按上表判斷錯碼情況。例如,若接收碼組為0000110,則計算的S1 =1,S2 =1,S3 =0,由于S1 S2 S3 等于110,可知a5位有一錯碼。上述方法構成的碼稱為漢明碼。表Ⅱ所列的(7,4)漢明碼最小碼距是d0=3,這種碼能糾正一個錯碼或檢測兩個錯碼。漢明碼的編碼效率等于k/n=(2r-1-r)/( 2r-1)=1-r/(2r-1)=1-r/n.當n很大時,則編碼效率接近1。可見漢明碼是一種高效碼。

3 編碼電路的實現

本設計的開發平臺是MAX+PLUSⅡ[4], MAX+PLUSⅡ是Altra公司專為本公司生產的PLD的研制和應用開發的軟件它的突出特點在于其強大的綜合能力和布局布線能力,另外還具有適用范圍廣、器件結構獨立、通用性好、兼容性好、集成度與自動化程度高以及易學易用的特點.

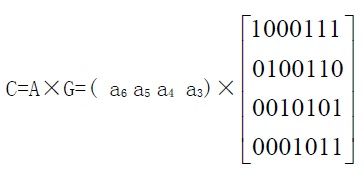

編碼器設計的特點是使用了矩陣的乘法,假設A是輸入至編碼器的數據向量,G是矩陣乘法的發生矩陣,C是漢明碼碼字,那么根據矩陣乘法計算得到漢明碼字。

程序編寫如下

module bianma(clk,reset,data_in,dcin,code_out,dcout);

input clk,reset;//時鐘和復位信號.

input[3:0] data_in;//輸入數據變量,位寬為4bit.

input dcin;//輸入有效控制信號,定義1表無效,編碼器不輸出碼字,定義0表有效.

output[6:0] code_out;//編碼器輸出,位寬為7bit.

output dcout;//輸出有效控制信號,定義1表無效.定義0表有效.

reg[6:0] code_out;

reg dcout;

reg[3:0] datareg;

reg dcinreg;

wire c0=datareg[3];

wire c1=datareg[2];

wire c2=datareg[1];

wire c3=datareg[0];

wire c4=datareg[3]^datareg[2]^datareg[1];

wire c5=datareg[3]^datareg[2]^datareg[0];

wire c6=datareg[3]^datareg[1]^datareg[0];

always@(posedge clk or negedge reset)//根據時鐘信號和輸入使能信號采集數據.

if(!reset)

dcinreg=1;

else

dcinreg=dcin;

always@(posedge clk)//采集是否有效.

if (reset)

datareg=0;

else if(!dcin)

datareg=data_in;

always@(posedge clk)//碼字在數據向量采集后一個時鐘周期計算得到.

if (reset)

dcout=1;

else

dcout=dcinreg;

always@(posedge clk)//碼字輸出是否有效.

if(reset)

code_out =0;

else

code_out={c0,c1,c2,c3,c4,c5,c6};

endmodule

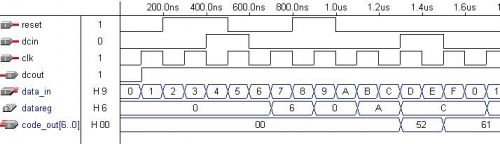

該源程序經過編譯和仿真,時序圖如下所示,得到結果符合系統功能要求

本設計使用的芯片為MAX3000A系列EPM3032ALC44-4,芯片的輸入輸出端口的設計采用D觸發器組來緩存數據,確保采集數據向量和發送的碼字穩定,并于時鐘信號嚴格同步。

4 結束語

本文通過介紹漢明碼的編碼原理,進而用Verilog HDL進行漢明碼編碼器的設計,并通過時序仿真波形圖進行邏輯分析,結果符合實際情況.而Verilog HDL有著類似C語言的編程風格,易于學習和掌握,與傳統的原理圖設計方法相比較, Verilog HDL更適合于規模日益增大的數字系統. Verilog HDL等硬件描述語言進行數字系統的設計是EDA發展的趨勢,在數字系統的設計中有著廣泛的空間.

評論