利用FPGA實(shí)現(xiàn)外設(shè)通信接口之: 典型實(shí)例-VGA接口的設(shè)計與實(shí)現(xiàn)

10.9典型實(shí)例19:VGA接口的設(shè)計與實(shí)現(xiàn)

10.9.1實(shí)例內(nèi)容及目標(biāo)

1.實(shí)例的主要內(nèi)容

本節(jié)旨在設(shè)計實(shí)現(xiàn)了FPGA與VGA顯示器的接口,幫助讀者進(jìn)一步了解VGA接口的時序和設(shè)計方法。

本文引用地址:http://www.104case.com/article/201706/348801.htm2.實(shí)例目標(biāo)

通過本實(shí)例,讀者應(yīng)達(dá)到以下目標(biāo)。

·掌握VGA接口的標(biāo)準(zhǔn)時序。

·掌握利用FPGA設(shè)計驅(qū)動的基本思想和方法。

·熟練掌握狀態(tài)機(jī)的使用。

10.9.2VGA接口實(shí)例內(nèi)容

紅色颶風(fēng)開發(fā)板的VGA接口可以產(chǎn)生8種顏色,可以用來顯示字符和簡單圖形。本實(shí)例要求通過VGA接口,在顯示器上依次顯示8種顏色的彩色條紋,條紋寬度相同。

10.9.3FPGA代碼設(shè)計實(shí)現(xiàn)

按照VGA時序要求產(chǎn)生行/列同步信號,并且在指定的時間(有效像素期間)將要顯示的顏色數(shù)據(jù)輸出到RGB。

不同的顯示模式和刷新頻率下,具體同步信號前、后、同步信號、有效像素數(shù)是不同的,要根據(jù)像素時鐘頻率來設(shè)置。以800×600,60Hz為例,像素時鐘為40MHz,即:

像素時鐘=(800+40+128+88)×(600+1+4+23)×60=40MHz

設(shè)計中可根據(jù)系統(tǒng)時鐘頻率來選擇合適的顯示模式。

10.9.4ModelSim仿真驗證

1.行顯示

設(shè)定一個列計數(shù)器,計數(shù)到相應(yīng)的值時,給出相應(yīng)的同步信號,并在像素有效期間,輸出有效的顏色數(shù)據(jù),行計數(shù)器通過檢測列同步信號來計數(shù),檢測到列同步信號,表示新一行的開始,這樣就可控制在不同的行顯示不同的內(nèi)容。

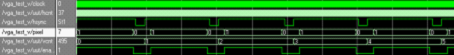

仿真結(jié)果如圖10.45所示。

圖10.45行顯示仿真結(jié)果

其中,hcnt為列計數(shù),列計數(shù)到有效像素時,給出enable信號,只有enable信號為高時,才給出有效像素數(shù)據(jù),并且在每個同步信號后,行計數(shù)器加1。

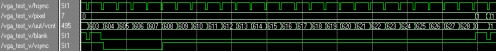

如圖10.46所示為行同步信號產(chǎn)生時仿真結(jié)果,當(dāng)計數(shù)到604-1=603行時,給出行同步信號,同步信號低電平持續(xù)4個行的時間,同步信號后持續(xù)21行的時間,之后再從第一行第一列開始。

圖10.46行同步信號產(chǎn)生后仿真結(jié)果

2.列顯示

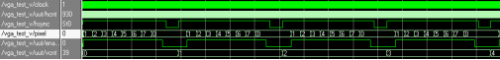

如圖10.47是列顯仿真結(jié)果。列顯示和行顯示不同在于,同一行的像素,計數(shù)到不同的值時,輸出不同的顏色數(shù)據(jù),每一行都是如此,最終就可得到列顯的彩色條紋。

圖10.47列顯仿真結(jié)果

10.9.5小結(jié)

本節(jié)對利用FPGA來驅(qū)動VGA接口顯示器的方法做了介紹,并通過編譯下載在紅色颶風(fēng)的開發(fā)板上實(shí)現(xiàn)

評論