FPGA與DSP協同處理系統設計之: FPGA與DSP的通信接口設計

11.3FPGA與DSP的通信接口設計

·主機型接口,如HPI等。

·總線型接口,如PCI、EMAC等。

·串口型接口,如McBSP、McASP、SPI、UART等。

·特殊類接口,如VLYNQ、VPORT等。

以上的接口中,比較常用的接口是EMIF和HPI。其中總線接口需要協議支持,開發難度較大,串行接口開發簡單,但是速率較慢。VPORT等特殊接口一般是在特定的場合下應用,不具備通用性,而且需要修改DSP驅動,開發周期較長。

11.3.1基于TMS320C64x系列的EMIF接口設計

1.EMIF簡介

TMSC64xEMIF是TMSC621xEMIF的增強版。它具備TMSC621x/TMSC671xEMIF的所有功能,并添加了以下新功能。

(1)EMIFA上的數據總線可以是64位寬,也可以是32位寬。

(2)EMIFB上的數據總線為16位寬。

(3)EMIF時鐘ECLKOUTx為內部生成,并基于EMIF輸入時鐘。器件復位時,以下3個時鐘之一會被配置為EMIF輸入時鐘。

·內部CPU時鐘4分頻。

·內部CPU時鐘4分頻。

·外部ECLKIN與TMSC64xEMIF接口的存儲器應按照ECLKOUTx的時鐘頻率運行。

·可編程同步存儲器接口控制器的同步控制引腳替換了固定的SBSRAM控制引腳。

·PDT引腳提供外部到外部傳輸支持。

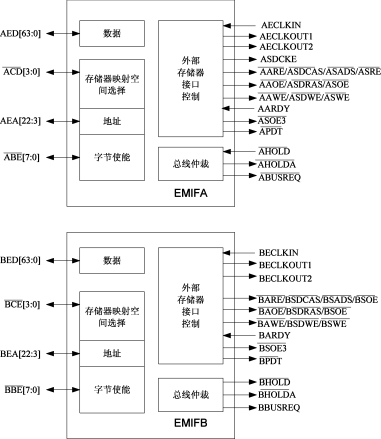

如圖11.4所示為組成EMIFA和EMIFB接口的信號,表11.2對這些信號進行了描述。端口A的信號都帶前綴“A”,端口B的信號都帶前綴“B”。為方便起見,所有信號名稱都省略了EMIF端口前綴。

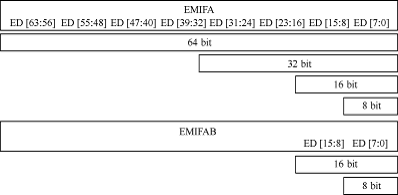

EMIFA接口具備與8、16、32或64位系統接口的功能。EMIFB接口端口僅支持8位和16位系統,如圖11.5所示。

外部器件(主要是存儲器)通常與總線的ED[7:0]字節側右對齊。Endianess(字節順序)決定ED[7:0]位是作為字節0(littleendian(小端))還是字節N(bigendian(大端),其中2N是總線寬度)存取。對不同字節通道的選擇,可通過低有效字節使能信號的應用(如表11.2所示)來完成。

圖11.4EMIFA和EMIFB信號

表11.2 EMIF信號描述

引腳 | I/O/Z | 描述 |

CLKOUT4 | O/Z | CPU時鐘的4分 |

CLKOUT6 | O/Z | CPU時鐘的6分 |

ECLKIN | I | EMIF時鐘輸入 |

ECLKOUT1 | O/Z | 速率為ECLKIN、CPU/4或CPU/6時的EMIF輸出時鐘 |

ECLKOUT2 | O/Z | 速率為ECLKIN、CLKOUT4或CLKOUT6時的EMIF輸出時鐘 |

ED[63:0] | I/O/Z | EMIFA64位數據總線 |

ED[31:0] | I/O/Z | EMIFA32位數據總線 |

ED[15:0] | I/O/Z | EMIFB16位數據總線 |

EA[22:3] | O/Z | EMIFA地址輸出 |

EA[20:1] | O/Z | EMIFB地址輸出 |

CE0 | O/Z | 存儲器空間0的芯片選擇 |

CE1 | O/Z | 存儲器空間1的芯片選擇 |

續表

引腳 | I/O/Z | 描述 |

CE2 | O/Z | 存儲器空間2的芯片選擇 |

CE3 | O/Z | 存儲器空間3的芯片選擇 |

BE[7:0] | O/Z | EMIFA64位字節使能,字節使能僅針對其對應的字節通道有效 如BE[0]對應ED[7:0] |

BE[3:0] | O/Z | EMIFA32位字節使能,字節使能僅針對其對應的字節通道有效 |

BE[1:0] | O/Z | EMIFB16位字節使能,字節使能僅針對其對應的字節通道有效 |

ARDY | I | 異步就緒輸入,低速外設插入等待狀態 |

SOE3 | O/Z | CE3的同步輸出使能 |

AOE | O/Z | 異步輸出使能 |

SDRAS | O/Z | DRAM存儲器的行地址選通脈沖 |

SOE | O/Z | 同步輸出使能 |

ARE | O/Z | 異步讀使能 |

SDCAS | O/Z | SDRAM存儲器的列地址選通脈沖 |

SADS/SRE | O/Z | 同步地址選通脈沖或讀使能 |

AWE | O/Z | 異步寫選通脈沖 |

SDWE | O/Z | SDRAM的寫使能 |

SWE | O/Z | 同步寫使能 |

HOLD | I | 外部總線保持請求 |

HOLDA | O | 外部總線保持確認 |

BUSREQ | O | 總線請求 |

PDT | O/Z | 外設數據傳輸 |

SDCKE | O/Z | SDRAM時鐘使能 |

CLKOUT4 | O/Z | CPU時鐘的4分 |

CLKOUT6 | O/Z | CPU時鐘的6分 |

ECLKIN | I | EMIF時鐘輸入 |

ECLKOUT1 | O/Z | 速率為ECLKIN、CPU/4或CPU/6時的EMIF輸出時鐘 |

ECLKOUT2 | O/Z | 速率為ECLKIN、CLKOUT4或CLKOUT6時的EMIF輸出時鐘 |

ED[63:0] | I/O/Z | EMIFA64位數據總線14 |

ED[31:0] | I/O/Z | EMIFA32位數據總線 |

ED[15:0] | I/O/Z | EMIFB16位數據總線 |

EA[22:3] | O/Z | EMIFA地址輸出 |

續表

引腳 | I/O/Z | 描述 |

EA[20:1] | O/Z | EMIFB地址輸出 |

CE0 | O/Z | 存儲器空間0的芯片選擇 |

CE1 | O/Z | 存儲器空間1的芯片選擇 |

CE2 | O/Z | 存儲器空間2的芯片選擇 |

CE3 | O/Z | 存儲器空間3的芯片選擇 |

BE[7:0] | O/Z | EMIFA64位字節使能。字節使能僅針對其對應的字節通道有效 |

BE[3:0] | O/Z | BE7對應ED[63:56] |

BE[1:0] | O/Z | BE6對應ED[55:48] |

ARDY | I | BE5對應ED[47:40] |

SOE3 | O/E | BE4對應ED[39:32] |

BE3對應ED[31:24] | ||

BE2對應ED[23:16] | ||

BE1對應ED[15:8] | ||

BE0對應ED[7:0] |

圖11.5按Endianess對齊字節

有關EMIF接口及其功能的完整概述,請參閱相關的TI數據手冊(tms320c64xx.pdf,其中xx為15t、16t或18)。

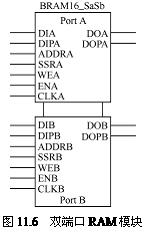

2.FPGA的BlockRAM簡介

Xilinx架構的FPGA都可以訪問模塊存儲器(BlockRAM)。Virtex、Virtex-E和Spartan-II器件中的這些4Kbit的模塊在Virtex-II、Virtex-IIPro和Spartan-3器件中都增加到18Kbit的模塊。

這些模塊都是完全同步、真正的雙端存儲器。用戶可獨立地從每個端口讀出或向每個端口寫入(但同一地址不能同時進行讀和寫)。另外,每個端口都有一個獨立的時鐘,并且對每個端口的數據寬度都可以獨立進行配置。如圖11.6所示為雙端RAM模塊的框圖。

由FPGA邏輯和一批BlockRAM組成的FIFO取決于所構建的FIFO要求的寬度和深度。FIFO可使用XilinxCOREGenerator™工具構建,或者可以用HDL手動組合。

使用COREGenerator工具構建FIFO具有一定優勢,即設計可以達到并實現很高的性能指標。按照設計規范用HDL構建的設計則可賦予設計人員完全的設計自由。

3.FPGA與DSP的EMIF連接

FPGA的靈活性使我們可以將其用做具備可選擇總線寬度(8位~64位)的各類存儲器而創建不同的設計。通過接口設計,可將FPGA用做同步或異步標準存儲器,或同步或異步FIFO。通過接口設計,可將FPGA以同步或異步的方式連接到EMIF。

在同步模式中,ECLKOUTx時鐘用于驅動FPGA接口邏輯。此時鐘甚至可以驅動整個FPGA。FPGA的邏輯功能、專用乘法器、PPC405或MicroBlaze™處理器等使其具備了強大的處理功能。這樣,FPGA就可以用做協處理器或高速數據處理和傳輸器件。

FPGA的存儲器容量小于TMSC64x類型DSP的尋址空間。FPGA存儲器必須使用FPGABlockRAM來實現。上述TMSC64x到FPGA的接口為FIFO結構,可以使用BlackRAM資源來實現。

FIFO接口可使用標準的TMSC64xEMIFFIFO接口機制。如表11.3所示為EMIF信號的總結。

表11.3 EMIF與FPGA的接口信號

信號名稱 | 方向 |

CE | DSP輸出 |

AOE | DSP輸出 |

AWE | DSP輸出 |

ARE | DSP輸出 |

INTx | DSP輸入 |

INTy | DSP輸入 |

INTz | DSP輸入 |

ED[63:0] | DSP雙向 |

FIFO要求連續地讀時鐘和連續地寫時鐘。這些時鐘由ARE和AWE信號生成,使用FPGA的本地時鐘控制功能進行布線。

DSP具有3.3V的接口邏輯,所以用于連接到EMIF的I/O組(bank)必須指定為3.3VVCCIO。如果無法指定,就必須使用電平移位器件。這一器件可為兩個器件間的信號通路引入額外的時間。

4.FIFO接口的設計實例

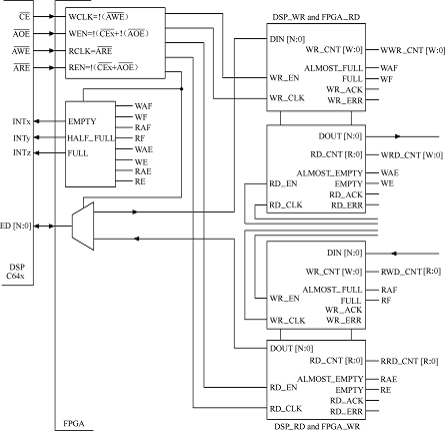

本設計使用了標準的EMIFFIFO設置。如圖11.7所示為用于Xilinx公司的Virtex-IIPro和Spartan-3器件的設計示例。

圖11.7基于FIFO的EMIF接口實例

數據組芯片使能信號(Cex)與異步輸出使能(AOE)一起,用于為設計的寫或讀FIFO部分生成使能信號。此信號還用于為數據多路復用器和標志選擇邏輯生成使能信號。

FIFO的讀寫時鐘通過本地時鐘布線直接布線到FIFO時鐘輸入。

FIFO中使用的RAMB16組件由于沿著與EMIF相連接的I/O塊進行排列,顯著改善了時序。當BlockRAM組件的列的大小與使用的I/O的數量相同時,即可構建快速的矩形接口。

本設計使用常規的FIFO標志輸出。要對標志邏輯施加額外控制,無論是針對DSP端還是FPGA端,可使用寫計數器和讀計數器輸出。

信號AINIT(圖11.7中未顯示)強制所有標志為高有效狀態。AINIT發出后,在第一個WR_CLK上,FULL和ALMOST_FULL標志變為無效,呈低狀態。對于在首個RD_CLK邊沿上的EMPTY和ALMOST_EMPTY標記,也會發生同樣情況。

ALMOST_EMPTY和ALMOST_FULL標志表明只剩下了一個FIFO位置。使用WR_COUNT和RD_COUNT輸出,可以構建用戶定義的FIFO標志。這兩個計數器的值都不反映FIFO內容(地址)的準確位置。FIFO的兩個端口(時鐘域)都存在時鐘延遲,長度為一個時鐘周期。

輸出WR_COUNT和RD_COUNT為被延遲的內部FIFO高位地址計數器。為輸出選擇兩個比特,即可將FIFO的位置確定到總尺寸的四分之一(如下面計數器解碼示例中所示)。

計數器越寬,位置就能越精細。下面是計數器解碼示例。

·COUNT[1:0]=0b00表明FIFO小于1/4滿或1/4空。

·COUNT[1:0]=0b01表明FIFO在1/4和1/2滿之間或1/4和1/2空之間。

·COUNT[1:0]=0b10表明FIFO在1/2和3/4滿之間或1/2和3/4空之間。

·COUNT[1:0]=0b11表明FIFO大于3/4滿或3/4空。

DSP對不同標志的反應取決于FPGA中讀寫FIFO的狀態。

11.3.2基于TMS320系列DSP的主機接口(HPI)設計

1.HPI接口簡介

HPI接口是一種數據寬度為16位的并行端口(C64xx系列DSP中,HPI口的數據寬度達到32位)。通過HPI口,主機可以直接對CPU的存儲器空間進行操作。

在C621x、C671x系列DSP中,沒有留出專門的EDMA通道來執行HPI口的訪問操作,而是直接將HPI口連接到內部的地址產生硬件上,因而提高了對內部存儲空間的訪問速度。

HPI口內部加入了兩個8級深度的讀寫緩沖,可以執行地址自增的讀寫操作,提高讀寫操作的吞吐量。HPI口為內部CPU提供了標準32位的數據接口,同時為外部主機也提供了一個經濟的16位接口,所以對外部主機而言,每次讀寫必須執行成對的16位操作。

對于C64xx系列DSP,HPI可以選擇16位(HPI16)和32位(HPI32)兩種模式。

對于C621x、C671x系列DSP,HPI口內部有3個寄存器,分別是控制寄存器(HPIC)、地址寄存器(HPIA)和數據寄存器(HPID)。這3個寄存器可以直接被主機訪問,主機每執行一次對CPU內部存儲空間的訪問都必須先對控制寄存器和地址寄存器寫入相應的值,然后才能對數據寄存器進行讀寫操作。

HPI口的外部接口是由數據總線HD[15:0]以及一部分用于描述和控制HPI接口的控制信號組成,這些控制信號的具體類型如表11.4所示。

表11.4 HPI信號描述

引腳 | 描述 |

HCNTL[1:0] | 控制HPI的操作類型 |

HHCNTL | 半字確認輸入,“0”、“1”分別表示一次字傳輸的第一個半字和第二個半字 |

HR/W | 讀/寫選擇 |

續表

引腳 | 描述 |

HRDY | 就緒狀態標志 |

HINT | 中斷標志,DSP向主機提出中斷 |

HAS | 區別地址/數據復用總線的數據與地址 |

HDS1、HDS2、HCS | 數據選通輸入,三者配合可用于產生一個HPI內部選通信號HSTROBE,這個信號可以用以下公式來描述: HSTROBE=[NOT(HDS1XORHDS2)]ORHCS |

對于一個寫HPI口的操作,應首先使能HCS,變化HDS1或HDS2,可使HSTROBE信號產生一個下降沿。HPI口在這個下降沿采樣控制信號HCNTL[1:0]、HHWIL和HR/W,同時在使能HCS的同時驅動HRDY,以使主機進入等待狀態。直到HRDY產生下降沿,表明HPID已清空,可以接收新的數據。此時HSTROBE也將產生一個上升沿,并采樣HD[15:0]上的數據并將其送入HPID,以完成第一個半字的寫入。

對于第二個半字的寫入,由于32位的HPID已經清空,可以直接寫入數據。不會出現未準備好的情況,所以HRDY一直保持為低,與第一個字節的寫入相同。該操作也在HSTROBE的下降沿采樣控制信號,并在HSTROBE的上升沿采樣數據總線HD[15:0]的數據并送HPID,以完成一個32位的寫入操作。

2.FPGA與DSP的HPI連接實例

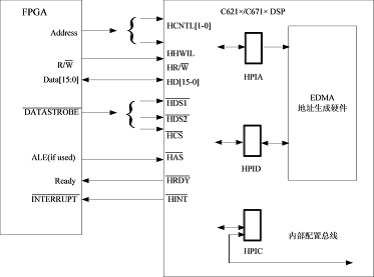

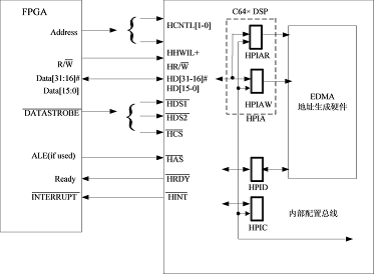

FPGA與HPI的接口連接比較簡單,就是將HPI接口相關的信號全部連接到FPGA的管腳。如圖11.8和圖11.9所示分別是FPGA和TI不同系列的DSP的連接框圖。

圖11.8FPGA與C621x、C671x系列DSP的HPI接口互聯框圖

圖11.9FPGA與C64x系列DSP的HPI接口互聯框圖

評論