如何實現更高的系統效率——第二部分:高速柵極驅動器

在此系列的第一部分中,討論過高電流柵極驅動器如何幫助系統實現更高的效率。高速柵極驅動器也可以實現相同的效果。

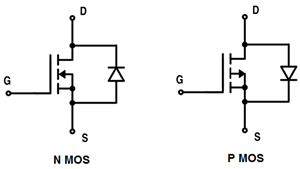

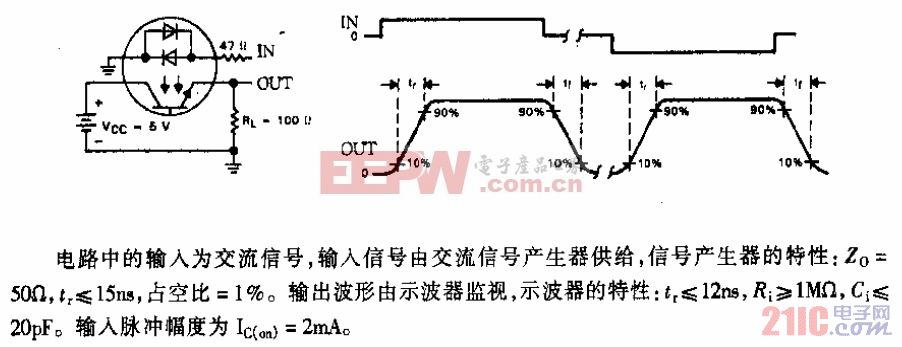

本文引用地址:http://www.104case.com/article/201706/346897.htm高速柵極驅動器可以通過降低FET的體二極管功耗來提高效率。體二極管是寄生二極管,大多數類型的FET固有。它由p-n結點形成并且位于漏極和源極之間。圖1所示為典型MOSFET電路符號中表示的體二極管。

圖1:MOSFET符號包括固有的體二極管

限制體二極管的導通時間將進而降低其兩端所消耗的功率。這是因為當MOSFET處于導通狀態時,體二極管上的壓降通常高于MOSFET兩端的電壓。對于相同的電流水平,P = I×V(其中P是功耗,I是電流,V是電壓降),通過MOSFET通道的傳導損耗顯著低于通過體二極管的傳導損耗。

這些概念在電力電子電路的同步整流中發揮作用。同步整流通過用諸如功率MOSFET的有源控制器件代替二極管來提高電路的效率。減少體二極管導通可以使這種技術的優點最大化。

下面考慮同步降壓轉換器的情況。當高側FET關斷并且電感器中仍然存在電流時,低側FET的體二極管變為正向偏置。死區時間短對避免直通很有必要。在此之后,低側FET導通并開始通過其通道導通。相同的原理適用于通常在DC / DC電源和電動機驅動設計中發現的其它同步半橋配置。

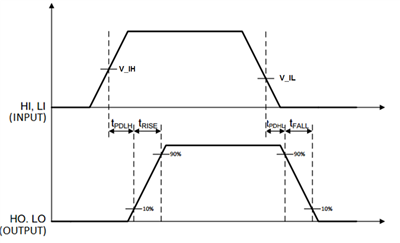

對于高速接通,柵極驅動器的一個重要參數是導通傳播延遲。這是在柵極驅動器的輸入端施加信號到輸出開始變高時的時間。這種情況如圖2所示。當FET重新導通時,體二極管將關斷。快速的導通傳播延遲可以更快地導通FET,從而最小化體二極管的導通時間,進而使損耗最小化。

圖2:時間示意圖,t_PDLH是導通傳播延遲

TI的產品組合包括具有行業領先的高速導通傳播延遲的柵極驅動器。參見表1。

類別 設備 描述 導通傳播延遲

高速驅動器 UCC27517A

4A / 4A高速低側柵極驅動器 13ns

UCC27611

4A / 6A高速低側柵極驅動器 14ns

UCC27201A

3A,120V高側和低側驅動器 20ns

表1:高速驅動器

系統效率是一個團隊努力的結果。本博客系列介紹了高速和高電流柵極驅動器是關鍵件。

評論