PCIE3.0簡介

那么PCI-E 3.0總線究竟有什么特點?對于其測試有什么特殊的地方呢?我們這里就來探討一下。

制定PCI-E 3代規范的目的主要是要在現有的廉價的FR4板材和接插件的基礎上提供比PCI-E 2代高一倍的有效數據傳輸速率,同時保持和原有1代、2代設備的兼容。別看這是個簡單的目的,但實現起來可不容易。

我們知道,PCI-E 2代在每對差分線上的數據傳輸速率是5Gbps,相對于1代數據速率的兩倍;而PCI-E 3代要相對于2代把速率也提高一倍,理所當然的是把數據傳輸速率提高到10Gbps。但是就是這個10Gbps帶來了很大的問題,因為PC和Server上出于成本的考慮,普遍使用便宜的FR4的PCB板材以及廉價的接插件,如果不更換板材和接插件,很難保證10Gbps的信號還能在原來的信號路徑上可靠地傳輸很遠的距離(典型距離是15~30cm)。因此PCI-SIG最終決定把PCI-E 3代的數據傳輸速率定在8Gbps。但是8Gbps比著2代的5Gbps并沒有高一倍,所以PCI-E協會決定在3代標準中把在1代和2代中使用的8b/10b編碼去掉。

我們知道,在PCI-E 1代和2代中為了保證數據的傳輸密度、直流平衡以及內嵌時鐘的目的,會把8bit數據會編碼成10bit數據傳輸。因此,5Gbps的實際有效數據傳輸速率是5Gbps×8b/10b=4Gbps。這樣,如果在PCI-E 3代中如果不使用8b/10b編碼,其有效數據傳輸速率就能比 2代的4Gbps提高1倍。但是這樣問題又來了,數據如果不經編碼傳輸很難保證數據傳輸密度和直流平衡,接收端的時鐘恢復電路也很容易失鎖。為了解決這個問題,PCI-E 3代里面采用了擾碼的方法,即數據傳輸前先和一個多項式進行異或,這樣傳輸鏈路上的數據就看起來就比較有隨機性,到了接收端再用相同的多項式把數據恢復出來。

通過上述方法,PCI-E 3代就可以用8Gbps的傳輸速率實現比2代的5Gbps高1倍的數據傳輸速率。實際應用中PCI-E 3代的總線上也仍然有數據編碼,不過采用的是128b/130b的編碼,編碼效率很高,由此損失的總線有效帶寬比8b/10b編碼小多了。

PCI-E 3.0 發送及接收端的變化

但是問題遠沒有結束,即使數據速率只有8Gbps,要在原有的廉價PCB和接插件上實現可靠傳輸也還要解決一些新的問題。其中最大的問題是信號的損耗,FR4板材對信號高頻成分有很大衰減,而信號速率越高,其高頻成分越多,所以衰減也就更厲害。下圖是不同速率的信號經過10英寸的FR4板材的PCB傳輸以后信號的眼圖,我們可以看到8Gbps的信號在接收端基本上看不到眼圖了,更不要說進行有效的數據接收。

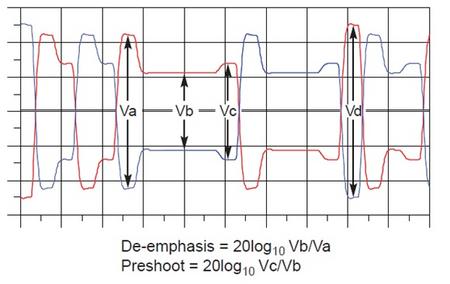

為了解決這個問題,在PCI-E的1代和2代中使用了去加重(De-emphasis)技術,即信號的發射端(TX)在發送信號時對跳變bit(代表信號中的高頻成分)加大幅度發送,這樣可以部分補償一下傳輸線路對高頻成分的衰減,從而得到比較好的眼圖。PCI-E 1代中采用了-3.5db的去加重,PCI-E 2代中采用了-3.5db和-6db的去加重。而對于3代來說,由于信號速率更高,需要采用更加復雜的去加重技術,因此除了跳變bit比非跳變bit幅度增大發送以外,在跳變bit的前1個bit也要增大幅度發送,這個增大的幅度通常叫做Preshoot。下圖是PCI-E 3代中采用的預加重技術對波形的影響的例子(參考資料:PCI Express® Base Specification 3.0 )。

為了應對復雜的鏈路環境,PCI-E 3代中規定了共11種不同的Preshoot和De-emphasis的組合,每種組合叫做一個Preset,實際應用中Tx和Rx端可以在Link Training階段根據接收端收到的信號質量協商出一個最優的Preset值。下圖是11種Preset的組合(參考資料:PCI Express® Base Specification 3.0)。比如P4代表沒有任何預加重,P7代表最厲害的預加重。

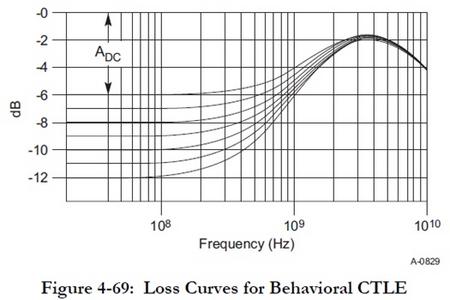

那做了這些工作就夠了嗎?經過實驗發現,僅僅在發送端對信號高頻進行補償還是不夠,于是PCI-E 3代標準中又規定在接收端(RX端)還要對信號做均衡(Equalization),從而對線路的損耗進行進一步的補償。均衡電路的實現難度較大,以前主要用在通信設備的背板或長電纜傳輸的場合,現在也逐漸開始在計算機領域應用,比如USB3.0中和SATA 6G中也采用了均衡技術。下圖是PCI-E 3.0里對均衡器的頻響特性的要求。我們可以看到均衡器的強弱也有很多檔可選,在Link Training階段TX和RX端會協商出一個最佳的組合(參考資料:PCI Express® Base Specification 3.0)。

經過各種信號處理技術的結合以及大量的實驗,PCI-E 3.0總算初步實現了在現有的FR4板材和接插件的基礎上提供比PCI-E 2代高一倍的有效數據傳輸速率。但我們同時也看到,PCI-E 3代的芯片會變得更加復雜,系統設計的難度也也更大。如何保證PCI-E 3代總線工作的可靠性和很好的兼容性,就成為設計和測試人員面臨的嚴峻挑戰。

評論