基于MSP430與FPGA的多功能數(shù)字頻率儀設(shè)計*

作者/ 任歡 顏逾越 廈門大學(xué)嘉庚學(xué)院 信息科學(xué)與技術(shù)學(xué)院(福建 漳州 363105)

本文引用地址:http://www.104case.com/article/201610/311936.htm摘要:本文采用以FPGA為主,MSP430為輔的框架系統(tǒng)處理方式設(shè)計了多功能數(shù)字頻率儀。該裝置采用低頻直接測周期,高頻等精度多周期同步測量的方法,通過進(jìn)一步優(yōu)化標(biāo)準(zhǔn)時鐘頻率的設(shè)置,克服了傳統(tǒng)測頻方法在高精度要求方面的缺陷。將MSP430作為控制處理核心、FPGA作為信號處理單元,將高效控制與快速運(yùn)算能力相結(jié)合,實(shí)現(xiàn)正弦波頻率、兩路方波信號時間間隔以及矩形脈沖占空比的測量。測試表明,該裝置具有高精度、高穩(wěn)定性、裝配簡易和操作便利的特點(diǎn)。

引言

隨著電子產(chǎn)業(yè)的蓬勃發(fā)展,新興產(chǎn)業(yè)對頻率等參量測量結(jié)果的快速性、穩(wěn)定性、精確性等性能指標(biāo)提出了更高的要求[1]。目前,信號頻率的測量已有多種測量方案,如過零檢測法[2]、離散傅里葉變換[3]、離散卡爾曼濾波[4-5]等。其中存在對高頻信號的快速測量的局限性、頻譜泄漏[6]以及準(zhǔn)確性有待提高[7]等問題。本文采用高速現(xiàn)場可編程邏輯陣列(FPGA)及超低功耗單片機(jī)(MCU),結(jié)合多周期測量原理,通過進(jìn)一步優(yōu)化標(biāo)準(zhǔn)時鐘信號頻率的設(shè)置,使用低頻時鐘計數(shù)法直接測周期,高頻等精度多周期同步測量法測頻率的方法,實(shí)現(xiàn)對待測信號頻率、占空比、兩路信號時間間隔等參量的高精度測量。

1 系統(tǒng)設(shè)計思路

1.1 系統(tǒng)總體結(jié)構(gòu)

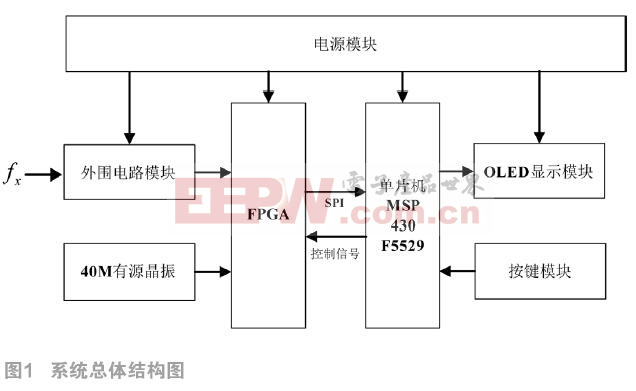

系統(tǒng)由Altera公司CycloneII EP2C8Q208C8型號FPGA、TI公司MSP430F5529型號MCU、外圍電路模塊、顯示模塊、按鍵模塊和電源模塊構(gòu)成,系統(tǒng)的總體結(jié)構(gòu)如圖1所示。其中,MCU是本系統(tǒng)的控制中心,主要負(fù)責(zé)數(shù)據(jù)接收、邏輯處理和命令傳達(dá);FPGA是本系統(tǒng)的核心測量模塊,主要負(fù)責(zé)利用由其內(nèi)含的計數(shù)模塊而構(gòu)成的等精度頻率測量模塊、高電平時間計數(shù)模塊、低電平時間計數(shù)模塊、時間間隔測量模塊進(jìn)行高頻信號的頻率、低頻信號的周期、單路方波信號的占空比和兩路方波信號時間間隔的測量,并根據(jù)MCU給定的控制信號,通過SPI協(xié)議發(fā)送相應(yīng)的測量數(shù)據(jù)至MCU中;外圍電路模塊是本系統(tǒng)的輸入信號調(diào)理模塊,主要負(fù)責(zé)將待測信號f(x)通過一系列的放大、整形等處理輸出為FPGA可直接判別并計數(shù)的方波信號;顯示模塊主要用于已測得信號的頻率、占空比、時間間隔等參量的顯示,并由按鍵模塊進(jìn)行數(shù)據(jù)刷新。

1.2 時間及頻率測頻原理

等精度頻率測量法是指在給定一種標(biāo)準(zhǔn)時鐘信號的情況下,通過對待測信號的上升沿進(jìn)行多次識別及計數(shù),從而得到待測信號頻率的方法。等精度頻率測量法的原理圖如圖2所示,若待測信號在標(biāo)準(zhǔn)時鐘信號上升沿個數(shù)為m的T秒時間內(nèi),上升沿個數(shù)為n個[8],則待測信號頻率為:

(1)

(1)

其中,fx為待測信號頻率,fs為標(biāo)準(zhǔn)時鐘信號頻率。

將式(1)進(jìn)行微分及相應(yīng)變換可得:

其中,dfs/fs為標(biāo)準(zhǔn)信號誤差,即晶振誤差,由于晶振穩(wěn)定性高,這一部分誤差可忽略不計。

則頻率測量誤差為:

(4)

(4)

由此可見,理論中測量誤差與待測信號頻率參數(shù)無關(guān)[9-10],增長標(biāo)準(zhǔn)時鐘信號的同步時間T或增大時鐘信號的頻率皆可進(jìn)一步提高測量精度,且等精度測頻法無法對頻率低于1/T低頻信號進(jìn)行測量。另一方面,在實(shí)際測試中,F(xiàn)PGA計數(shù)結(jié)果可能因硬件延遲存在著兩個計數(shù)值的固定誤差,則有實(shí)際誤差為:

(5)

(5)

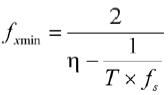

若要求測量誤差小于η時,則符合精度的待測頻率fx的最小值為:

(6)

(6)

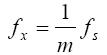

直接測周法是一種對待測信號一個周期內(nèi)標(biāo)準(zhǔn)時鐘信號進(jìn)行計數(shù),從而測量待測信號頻率的方法,其測量原理圖如圖3所示。若標(biāo)準(zhǔn)時鐘信號在待測信號一個周期內(nèi)上升沿個數(shù)為m個[11],則待測信號頻率為:

(7)

(7)

同理可得:

(8)

(8)

同理,省略掉晶振誤差,且考慮FPGA硬件延遲后,可得直接測周法的測量誤差為:

(9)

(9)

由此可見,理論中測量誤差與待測信號頻率參數(shù)有關(guān),若要求測量誤差小于時,則符合精度的待測頻率fx最大值為:

(10)

(10)

若要對低頻段采用直接測周法,高頻段采用等精度測頻法實(shí)現(xiàn)對整個通帶的信號頻率測量,則必須有![]() ,即必須將標(biāo)準(zhǔn)時鐘信號頻率設(shè)置為:

,即必須將標(biāo)準(zhǔn)時鐘信號頻率設(shè)置為:

本文來源于中國科技期刊《電子產(chǎn)品世界》2016年第9期第65頁,歡迎您寫論文時引用,并注明出處。

評論