基于DBL結(jié)構(gòu)的嵌入式64kb SRAM的低功耗設(shè)計(jì)

關(guān)鍵詞:存儲(chǔ)器;SRAM;位線(xiàn)分割;分塊譯碼

嵌入式存儲(chǔ)器的容量及其在系統(tǒng)芯片中所占的面積越來(lái)越大,對(duì)其操作所帶來(lái)的動(dòng)態(tài)功耗成為系統(tǒng)芯片功耗中重要的組成部分,因此,必須尋求有效的低功耗設(shè)計(jì)技術(shù),以降低嵌入式存儲(chǔ)器對(duì)整個(gè)系統(tǒng)的影響。為了降低存儲(chǔ)器的功耗,人們采用了字線(xiàn)分割、分級(jí)字線(xiàn)譯碼以及字線(xiàn)脈沖產(chǎn)生等技術(shù),大大降低了存儲(chǔ)器的動(dòng)態(tài)功耗。 另外一種能有效降低存儲(chǔ)器動(dòng)態(tài)功耗的技術(shù)就是位線(xiàn)分割(DBL)。 針對(duì)系統(tǒng)要求,筆者采用DBL結(jié)構(gòu)以及一種存儲(chǔ)陣列分塊譯碼結(jié)構(gòu),完成了64 kb嵌入式存儲(chǔ)器模塊的設(shè)計(jì)。

參數(shù)的修正與公式的重新推導(dǎo)

DBL結(jié)構(gòu)的原理

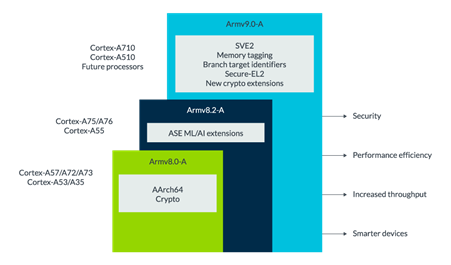

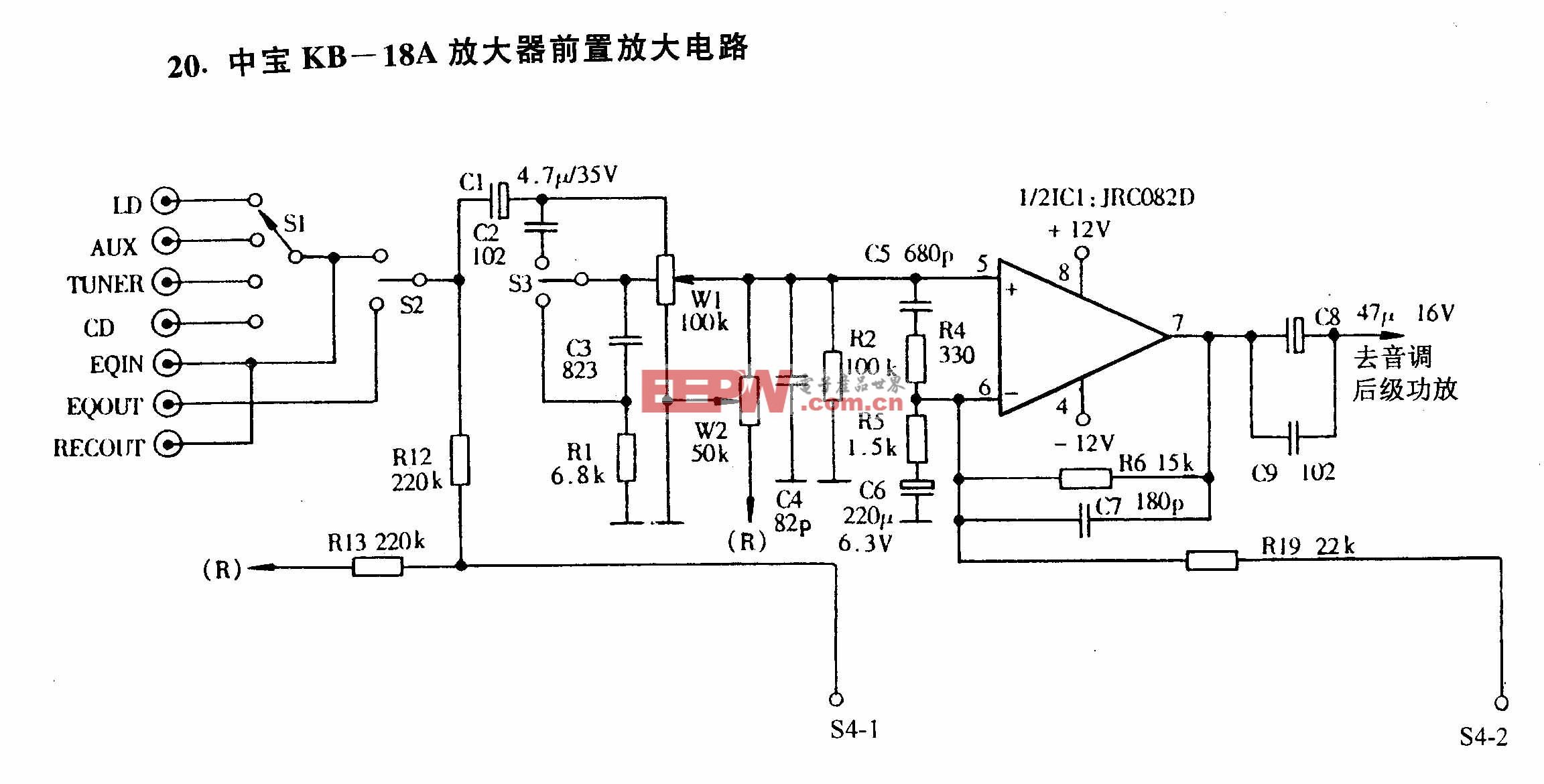

DBL結(jié)構(gòu)就是通過(guò)將兩個(gè)或者多個(gè)SRAM存儲(chǔ)單元進(jìn)行合并,以減少連接到位線(xiàn)上的晶體管數(shù)目,從而減小位線(xiàn)電容,達(dá)到降低存儲(chǔ)器動(dòng)態(tài)功耗的目的。 圖1w給出了將4個(gè)SRAM單元連接在一起并通過(guò)傳輸管連接到位線(xiàn)上的電路示意圖。 與一般布局的位線(xiàn)結(jié)構(gòu)相比,圖1w所示的DBL結(jié)構(gòu)中連接到位線(xiàn)上的傳輸管數(shù)目減少了3 /4。

DBL結(jié)構(gòu)有兩個(gè)關(guān)鍵:第1,確定存儲(chǔ)陣列行數(shù)N 與合并的單元個(gè)數(shù)M 之間的最優(yōu)關(guān)系。 所謂最優(yōu)是指合并后存儲(chǔ)器的動(dòng)態(tài)功耗最小。 對(duì)于這個(gè)關(guān)系,文獻(xiàn)[ 1 ]中給出了相應(yīng)的公式:

pnor = (1 /M + 0.1) + 2 ( (M + 1) / (N (ΔV /V ) ) ) , (1)

Mop t = ( (N /2) (ΔV /V ) ) 1 /2 , (2)

式中ΔV 表示位線(xiàn)上電壓的擺幅, V 表示電源電壓。第2,確定合并后各個(gè)管子的寬長(zhǎng)比。下面,針對(duì)這兩個(gè)問(wèn)題進(jìn)行討論。

DBL功耗公式的修正

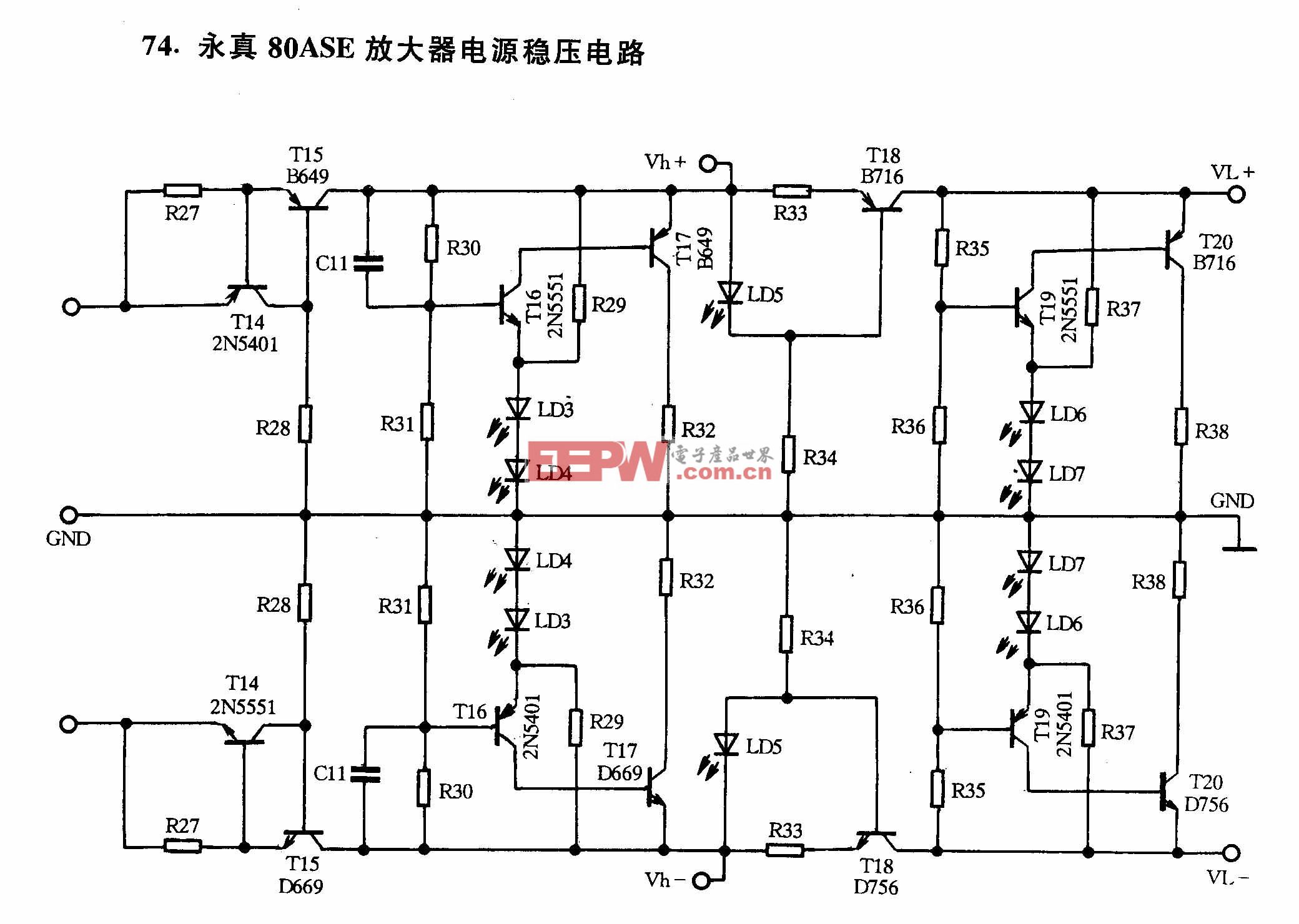

公式(1) , ( 2)是在下述假設(shè)下得出的:在SRAM中,位線(xiàn)的電容主要是由存儲(chǔ)單元中傳輸晶體管的漏極電容和位線(xiàn)的金屬連線(xiàn)電容構(gòu)成,并且金屬線(xiàn)的寄生電容是與位線(xiàn)相連管子漏極總電容C的10% ,則圖2中寄生電容C1 和C2 可表示為

C1 = C M /N , C2 = C /M + 0.1C 。

然而,上述假設(shè)并沒(méi)有真正反映位線(xiàn)電容的構(gòu)成,因?yàn)槲痪€(xiàn)電容的組成包括存儲(chǔ)單元中傳輸晶體管的源/漏電容CBS ,位線(xiàn)間的耦合電容CBB ,位線(xiàn)與橫向字線(xiàn)之間的耦合電容CWW ,位線(xiàn)與地線(xiàn)的耦合電容CBSS ,位線(xiàn)與電源線(xiàn)的耦合電容CBDD ,位線(xiàn)的金屬連線(xiàn)電容CW 等。 隨著深亞微米技術(shù)的發(fā)展,在位線(xiàn)總電容中,傳輸晶體管的源/ 漏電容CBS 所占的比例只有60% ~ 70% ,其他的電容分量共占30% ~40%,在這種情況下公式設(shè)計(jì)電路會(huì)帶來(lái)較大的誤差。 另外,對(duì)C1 的舍入過(guò)大,由此也引入了很大的誤差,必須進(jìn)行修正。 筆者對(duì)公式的重新推導(dǎo)如下。

假設(shè)存儲(chǔ)陣列的行數(shù)為N, DBL 結(jié)構(gòu)中合并的存儲(chǔ)單元數(shù)為M,一般布局結(jié)構(gòu)(N 行) 中, 與位線(xiàn)相連的所有傳輸管漏極的總電容為C,并假定位線(xiàn)上其他的寄生電容是此漏極總電容的30% , 則圖2中電容C1 和C2 可表示為

C1 = C (1.3M + 1) /N , C2 = (C /M ) + 0.3C 。

假設(shè)讀寫(xiě)操作時(shí)子位線(xiàn)不進(jìn)行預(yù)充電,并且其電壓值能夠達(dá)到電源電壓,用ΔV 表示位線(xiàn)上電壓的擺幅,那么,圖2中DBL存儲(chǔ)器的動(dòng)態(tài)功耗可表示為

p =f (M ) = (C2 ΔV V + 2 C1 V2 ) f = [ (C /M + 0.3 C) ΔV V + 2 C ( (1.3M + 1) /N ) V2 ] f (3)

根據(jù)標(biāo)準(zhǔn)存儲(chǔ)單元的功耗表達(dá)式pstan = (C ΔV V ) f , (4)

對(duì)式(3) 歸一化得pnor = (1 /M + 0.3) + 2 ( (1.3M + 1) / (N ΔV /V ) ) , (5)

因此可求得功耗最小時(shí)的M 值Mop t = ( (N /2. 6) (ΔV /V ) ) 1 /2 。 (6)

如果存儲(chǔ)陣列的行數(shù)N = 1 024,位線(xiàn)電壓變化率ΔV /V = 011,則Mop t ≈ 6, pnor ≈ 0164。 但是如果按照公式(1) , (2) 計(jì)算,則Mop t ≈ 8, pnor ≈ 0140,后面的設(shè)計(jì)均基于修正后的公式(5) , (6)。

管子寬長(zhǎng)比的選擇

在6管存儲(chǔ)單元中,為了完成正常的讀寫(xiě)操作,各個(gè)管子的寬長(zhǎng)比必須滿(mǎn)足一定的約束條件,這種約束條件通常用上拉比PR 和單元比CR 來(lái)刻畫(huà)。 對(duì)于圖3@ 所示的存儲(chǔ)單元,有CR = (WN 2 / LN 2 ) / (WN 4 /LN 4 ) PR = (WP1 / LP1 ) / (WN 3 /LN 3 ) 。 為了完成正常的讀出操作,不發(fā)生“讀翻轉(zhuǎn)”,要求CR 大于1.8 (VDD = 3.3V, Vt = 0.5V) [ 7 ] ,因此N2 比 N4 有更好的導(dǎo)通性。 為了完成正常的寫(xiě)入操作, 要求PR 小于1 (VDD = 3.3V, Vtp = 0.5V 和μP /μN =0.5) ,也就是說(shuō), N3 應(yīng)該比P1 有更好的導(dǎo)通性。 在DBL結(jié)構(gòu)中,如果存儲(chǔ)單元中各個(gè)管子的W /L 與 一般結(jié)構(gòu)中的相同,顯然,由于N4 和N6 (N3 和N5 ) 的串聯(lián)等效關(guān)系,使得CR 的條件更容易滿(mǎn)足,而PR 的條件更不容易滿(mǎn)足,從而使寫(xiě)入操作變得更加困難。 因此, 為了完成正常的讀寫(xiě)操作, 應(yīng)合理確定管子N4 和N6 (N3 和N5 ) 的寬長(zhǎng)比。N4 和N6 寬長(zhǎng)比的選擇,可以通過(guò)將N4 和N6 (N3 和N5 ) 近似成串聯(lián)電阻來(lái)估算,如圖3w 所示。 為了方便分析,假設(shè)N4 和N6 的結(jié)構(gòu)相同。 顯然,為了保持原先存儲(chǔ)單元正常的讀寫(xiě)功能,應(yīng)該將N4 和N6 的寬長(zhǎng)比都加倍,而其他管子的寬長(zhǎng)比保持不變。

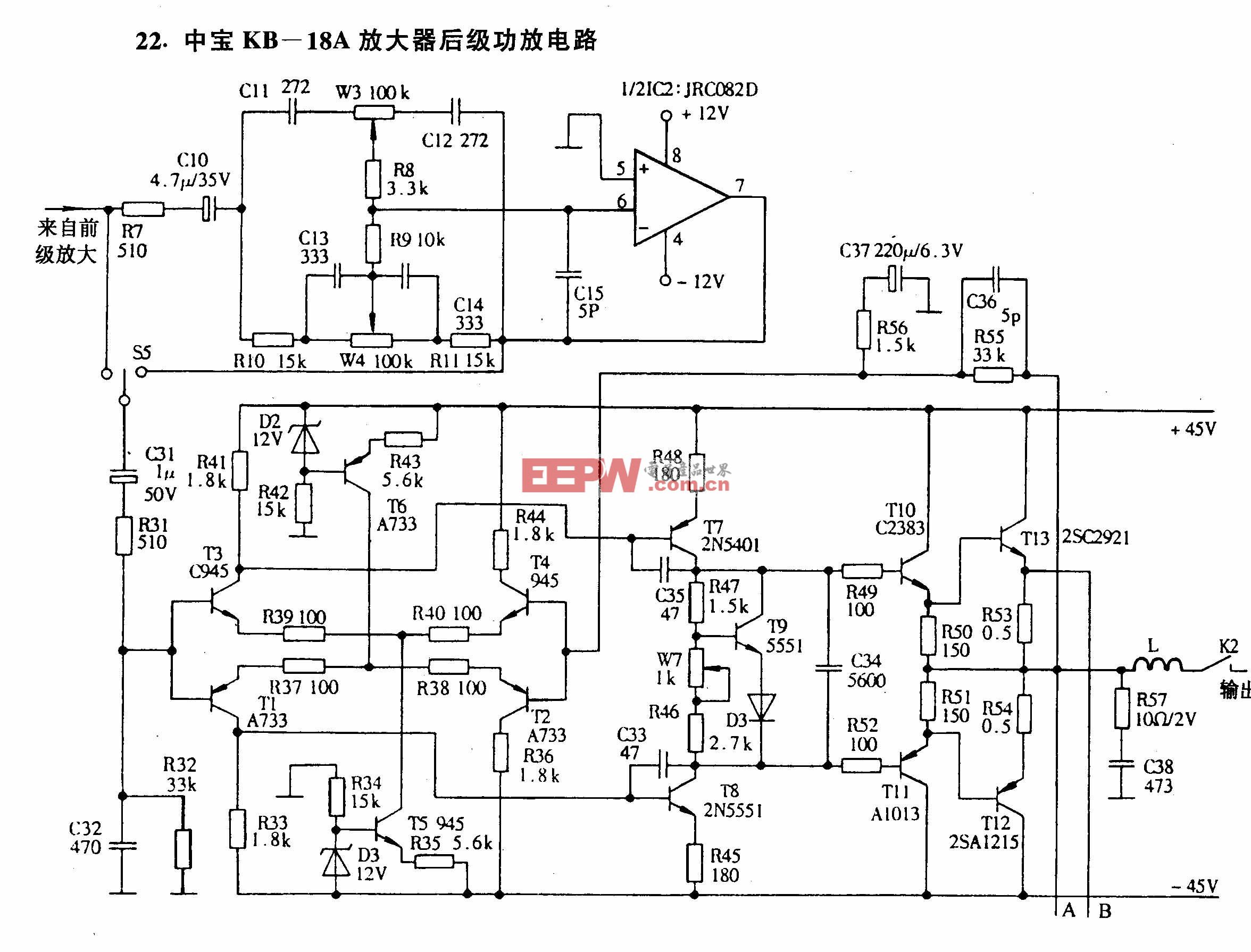

分塊譯碼的DBL 結(jié)構(gòu)

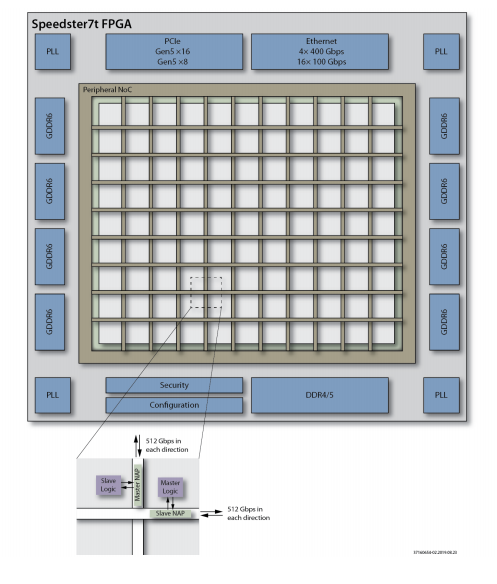

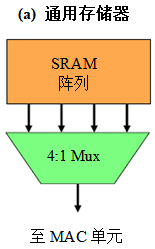

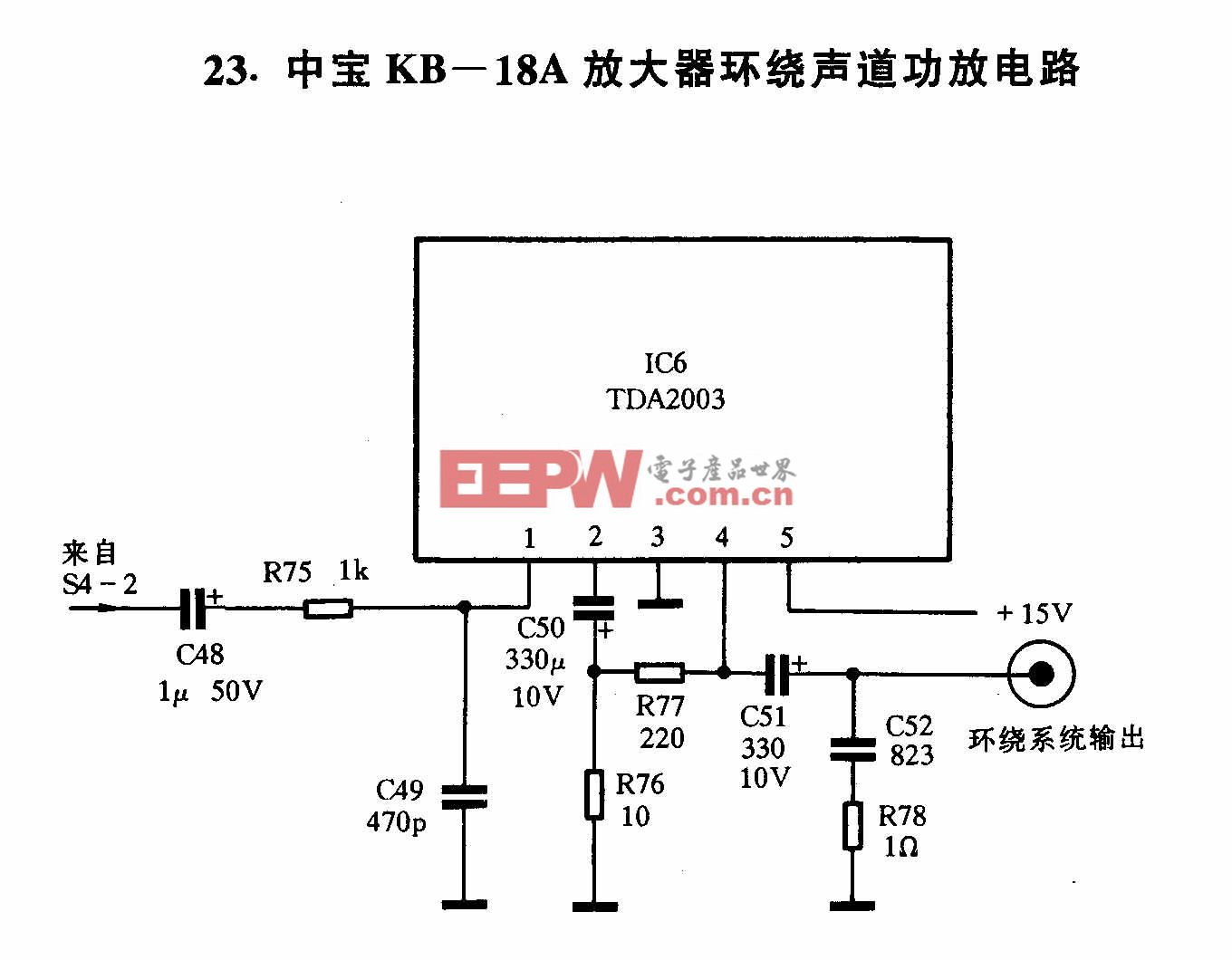

通過(guò)前面的分析可以看出,對(duì)于位線(xiàn)很長(zhǎng)的存儲(chǔ)陣列,通過(guò)采用DBL技術(shù),選取合理的M 值,動(dòng)態(tài)功耗會(huì)有所減小。 然而,以上的分析并沒(méi)有考慮不同尺寸的管子以及不同的版圖布局風(fēng)格等因素的影響。 另外,在DBL結(jié)構(gòu)中,由于還附加了其他的控制邏輯電路,其本身也有功耗,因此,實(shí)際功耗并不能完全按照公式(5)計(jì)算。為了進(jìn)一步降低存儲(chǔ)器的功耗,筆者在DBL結(jié)構(gòu)的基礎(chǔ)上,設(shè)計(jì)了存儲(chǔ)陣列的分塊譯碼結(jié)構(gòu)。首先,為了使版圖形狀滿(mǎn)足要求,將64kb SRAM劃分成8個(gè)8kb的子陣列,并利用地址信號(hào)A1 , A2 , A3 譯碼后對(duì)8個(gè)8kb子陣列進(jìn)行選擇。 這不僅滿(mǎn)足了版圖的布局要求,也降低了存儲(chǔ)器的功耗,整個(gè)布局如圖4v所示。分塊譯碼的DBL結(jié)構(gòu)主要是針對(duì)每個(gè)8kb的存儲(chǔ)子陣列設(shè)計(jì)的,如圖4w所示,每個(gè)8kb的子陣列由左右兩個(gè)存儲(chǔ)陣列模塊構(gòu)成。 其工作原理為:利用列地址線(xiàn)A0 和A0 控制行譯碼器的輸出,使得在任何讀寫(xiě)周期,左右兩個(gè)存儲(chǔ)陣列只有一個(gè)被選中,這樣整個(gè)64kb的SRAM就有1 /16子陣列處于活動(dòng)狀態(tài),從而減小了由于字線(xiàn)充放電引起的動(dòng)態(tài)功耗。

圖4w中,控制邏輯的具體結(jié)構(gòu)如圖4x 所示,子陣列sub DBLmemroy arrayi ( i = 0~7)的結(jié)構(gòu)如圖4y所示,每個(gè)子陣列有512行,即N =512,根據(jù)公式(6) ,合并后的存儲(chǔ)單元數(shù)M =4

按照分塊譯碼的DBL結(jié)構(gòu),采用chartered 0.35μm雙層多晶三層鋁布線(xiàn)的n阱CMOS工藝,完成了嵌入式64kb SRAM模塊的設(shè)計(jì),版圖面積1。 4mm 4. 7mm (一般結(jié)構(gòu)的版圖面積1.3mm 4. 3mm)。 Starsim仿真結(jié)果表明,采用分塊譯碼DBL結(jié)構(gòu)的存儲(chǔ)器的平均電流約為37mA,一般結(jié)構(gòu)存儲(chǔ)器的平均電流約為65mA。

結(jié)束語(yǔ)

以上討論了嵌入式64kb SRAM的低功耗設(shè)計(jì),通過(guò)采用DBL結(jié)構(gòu)以及存儲(chǔ)陣列分塊譯碼結(jié)構(gòu),使得存儲(chǔ)器的功耗降低了43%,而面積僅增加了18%。 仿真結(jié)果表明兩者的最小訪(fǎng)問(wèn)周期都約為15 ns。 因此,根據(jù)A T2 P (A 是面積, T是訪(fǎng)問(wèn)周期, P是功耗)來(lái)衡量,這種低功耗設(shè)計(jì)方法是可行的。隨著嵌入式存儲(chǔ)器容量的加大以及深亞微米技術(shù)的發(fā)展,亞閾值漏電流所造成的靜態(tài)功耗已經(jīng)不可忽略,尋求有效的低功耗設(shè)計(jì)技術(shù)仍然是值得探討的課題。

評(píng)論