FPGA自動加載系統設計實現

摘要:針對FPGA可以在每次上電時自動獲取配置文件的需求,提出了一種由USB芯片和FLASH芯片、CPLD組成的可對FPGA上電后自動加載的系統。該系統可以通過USB芯片和CPLD將PC中的FPGA配置文件寫入FLASH芯片,并且在CPLD的控制下將配置文件以PS模式配置給FPGA。測試表明,該系統可以在上電時自動對FPGA進行加載,彌補了FPGA掉電后數據消失的不足。

本文引用地址:http://www.104case.com/article/201610/308546.htm0 引言

FPGA(Field Programmable Gate Array)即現場可編程門陣列,隨著微電子技術的發展,FPGA的性能變的越來越優越,應用空間也變得越來越廣。FPGA具有支持重復編程的特點,但是掉電后不能保存配置信息。因此在上電后,都需要用戶將設計的FPGA配置文件從外部存儲器中下載到FPGA中才能工作。針對這種情況,本文提出了一種以USB芯片,FLASH芯片和CPLD組成的FPGA自動加載系統。該系統通過USB芯片將PC中的配置文件傳送給CPLD,CPLD再將其寫入FLASH芯片,FLASH芯片可以長久地存儲配置文件。這樣FPGA每次上電后CPLD將FLASH中的配置文件讀出來配置FPGA。從而使FPGA在每次上電后都可以自動獲取配置文件,使其可以作為一個獨立“芯片”工作,具有很強的實用性。在PS模式配置方式上也有改進,在傳統PS模式下配置多個FPGA時通常使用前一級的FPGA的nCEO連接后一級FPGA的nCE來使能后一級FPGA,這樣在第一個FPGA配置好后,nCEO會使能下一級的FPGA開始配置。這樣只能先配置第一個FPGA,而且不能自由控制來配置下一級的FPGA。采用CPLD同時連接兩個nCE,在前一級FPGA配置好后,獲取完成信號來配置第二個FPGA,這樣不受FPGA前后級聯的順序影響,可以自由選擇配置FPGA。

1 系統框架及芯片簡介

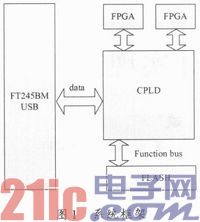

系統由CPLD,USB芯片和FLASH芯片組成,外加PC部分配合系統工作。系統框架見圖1。系統中USB芯片連接PC與CPLD,PC通過USB向CPLD發送命令來操作FLASH。首先發送擦除FLASH命令,擦除完畢或將配置文件寫入FLASH芯片。在FLASH芯片中可以存入多個FPGA的配置文件,在上電后或者需要加載時,CPLD讀取FLASH中的配置文件并且對FPGA進行配置。

2 燒寫FLASH時序

USB、CPLD和FLASH的連接關系如圖2所示。USB將PC的命令和配置文件發送給CPLD,CPLD通過時序邏輯控制FLASH。

系統中所使用的USB芯片是FTDI公司的FT245BL,將USB芯片與PC連接后,USB芯片會自動識別為串口,利用串口調試助手可以向其發送命令或文件。

擦除和燒寫FLASH操作如下所述:

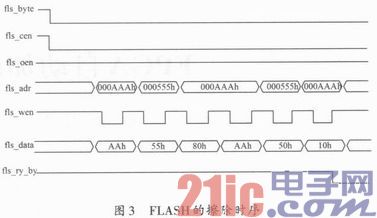

FLASH芯片選用恒憶公司的M29EW系列512MNOR型FLASH。采用異步時鐘操作,時序圖中的fls_byte管腳對應的位寬選擇信號,在本系統中將其拉低表示使用8 b位寬fls_adr表示地址,fls_dat表示數據,fls_cen為芯片使能信號,fls_oen為芯片讀使能信號,fls_wen為芯片寫使能信號。

如圖3和圖4所示,在執行擦除或寫操作時序時,將fls_cen拉低、fls_oen拉高時可以執行寫或擦除命令,fls_wen上升沿采樣地址,下降沿采樣數據。fls_ry_by是芯片的繁忙或空閑信號,是FLASH芯片惟一的輸出信號,用于表示正在執行擦除或者寫操作。

(1)擦除FLASH

在使用FALSH芯片之前需要對其進行擦除,PC通過USB向CPLD發出擦除命令后如圖3所示。寫入連續5個對應的地址和數據后,FLASH芯片將整個芯片的數據擦除,如圖3所示在執行后,fls_ry_by信號拉低表示進入了擦除狀態。

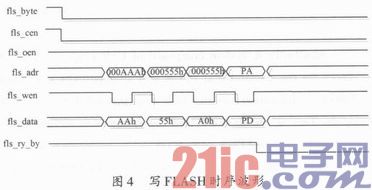

(2)燒寫FLASH

如圖4所示,在執行寫FLASH操作時,首先需要給出寫FLASH三次對應的數據和地址作為前置命令,然后給出需要寫入FLASH的地址和數據。在接到命令后,CPLD根據圖中時序將FPGA的配置文件寫入FLASH。

3 PS模式自動加載FPGA

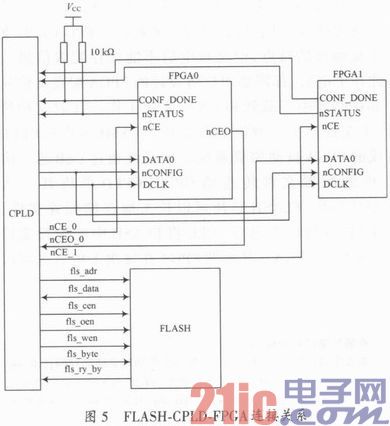

FPGA的配置管腳如圖5所示。

在PS模式下配置FPGA的FLASH,CPLD和FPGA的連接關系如圖5所示。

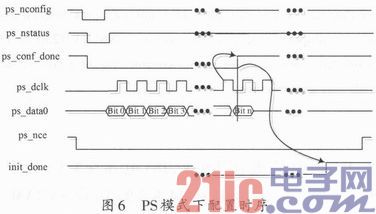

圖6所示為PS模式加載FPGA的流程圖。在加載過程中,將ps_nce拉低并且將ps_nconfig拉低至少40μs后再拉高,正常情況下這個操作會使ps_nstatus產生一個由低到高的一個脈沖信號并且使ps_conf_done由高變低。在ps_nstatus產生上升沿的瞬間立即給出ps_dclk和ps_data0來配置FPGA,其中ps_data0信號是通過讀取FLASH芯片中的數據實現的。FPGA在接收配置文件的過程會自動識別文件的結尾,在配置結束后ps_ conf_done信號會拉高以表明配置結束,配置過程中init_done會由高變低,在經過至少18μs后init_done信號拉高表明完成初始化,隨后進入用戶模式。常規的方式采用nCONFIG,nSTATUTS,CONF_DONE復用,并且前一級FPGA的nCE連接后一級的FPGA的nCEO,這樣加載順序就被固定,而且每次加載只能先加載第一個FPGA,待加載完畢后才能加載第二個FPGA。與常規的配置方式不同之處在于通過使能nCE來選擇需要配置的FPGA,給出相應的配置文件與信號ps_conf_done的時序來判斷是否配置完成,這樣就可以自由選擇配置FPGA。

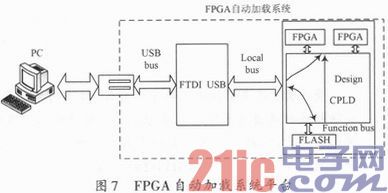

如圖7所示為FPGA自動加載的平臺,通過CPLD的邏輯控制和USB芯片的總線可以將PC端配置文件寫入FLASH芯片中。在需要使用自動加載功能時,在上電后CPLD會立即讀出存取在FLAHS中的FPGA配置文件,以PS模式配置相應的FPGA。

4 結論

經測試系統可以在上電后對FPGA進行自動加載。本文提供了系統的結構框架和實施方案整體流程以及時序要求,具有很強的應用和參考價值。

評論