基于FPGA的多通道高速采樣系統設計

摘要:旋轉機械的振動監測,對于機械的安全運行和提高設備利用率有重大意義。利用FPGA的并行處理能力,采用高速可編程FPGA模塊和嵌入式開發的結合方式,提出了一種基于FPGA的高速、多通道、同步采樣實現方法。闡述了對于高速AD芯片的控制,硬件的布局布線,以及對于系統的功能要求,進行了軟硬件的設計和調試。通過仿真和實驗的結果表明,對于信號發生器發出的高頻率正弦波,上位機上能夠顯示出完好的波形,即基于FPGA的采樣設計能夠達到多通道,高速采樣的要求,可以實現對高速旋轉機械振動的實時監測。

0 引言

大型旋轉機械包括了汽輪機、水輪機、壓氣機等機械設備,是航空、電力、機械、石油化工等領域的關鍵設備。隨著工業生產和運行機組的參數不斷提高,對設備的可靠性、安全性、經濟性提出了更高的要求,促使了對于旋轉機械設備振動監測技術的研究。

目前實現數字信號處理主要有兩種形式:一種是使用數字信號處理器(DSP),DSP芯片的內部采用程序和數據分開的哈夫結構,而且具有專門的硬件乘法器,可以廣泛采用流水線操作,提供特殊的DSP指令,可以用來快速地實現各種數字信號處理算法。然而,由于受到DSP自身性能的限制以及程序指令按順序執行的特點,難以實現大規模、高速運算;另一種則是現場可編程門陣列(FPGA)。FPGA的結構主要分為三部分:可編程邏輯模塊、可編程I/O模塊、可編程內部連線,這樣就大大降低了印刷電路板設計的工作量和難度,同時,FPGA具有強大的邏輯功能,能對多路信號進行并行處理,可以自定義模塊和自定義指令,有效提高了設計的靈活性和效率。因此,在比較低的取樣速率時,整體上很復雜的程序可以使用DSP;而在高速,多通道采樣方面,FPGA具有明顯的優勢。實際中,一般的水輪機,汽輪機的旋轉速度在每分鐘幾千轉,可以利用DSP完成數據采樣,但是遇到超過每分鐘萬轉以上的旋轉機械,就可以利用FPGA來完成高速采樣。

本設計采用高性能的FPGA芯片EP3C25Q240,高速多通道同步采樣AD芯片THS1207,通過良好的PCB布局、模塊化編程、多通道并行處理,實現對于高速旋轉機械的振動監測與分析。

1 并行系統的工作原理

1.1 系統內部構成

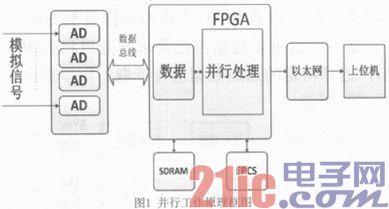

并行系統工作原理框圖如圖1所示。本系統采用自頂向下的設計方法,可以主要分為AD模塊、FPGA控制模塊和以太網通信模塊。外部振動模擬信號經過信號調制電路后進入AD芯片進行12位模數轉換,之后把數字信號并行傳遞給FPGA芯片。得到采樣數據后,FPGA對信號進行并行處理,然后將處理過的數字信號通過以太網完成與上位機的數據通信。

FPGA模塊是信號處理系統的核心,它主要完成對數據采集的控制,對數字信號的并行處理與運算以及以太網通信。

1.2 系統外圍接口

系統外圍主要有AD轉換電路、信號調理電路、鍵相電路、SDRAM和EPCS電路、電源電路、JTAG和AS調試接口、以太網接口和LED顯示接口等。

2 板級電路設計

作為控制核心的FPGA芯片采用Altera公司的Cyclone系列的第三代EP3C25Q240,它具有豐富的資源和引腳數量,足夠滿足本系統需要。憑借其低功耗、高功能、低成本的前所未有的組合,拓寬了大批量、成本敏感的應用。

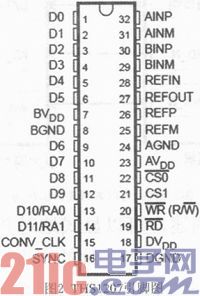

考慮到設計的高速多通道的要求,AD選用了Texas Instruments生產的高速芯片THS1207。THS1207是一個CMOS、低功耗、12位、6 MSPS模擬-數字轉換器。對速度、分辨率、帶寬和單電源操作都非常適合應用在雷達成像、高速采集和通信。輸出誤差校正邏輯的多級流水線架構,并提供了在整個工作溫度范圍內無失碼。該THS1207由四個模擬輸入,同時進行采樣,這些輸入可以單獨選擇,配置為單端或差分輸入。為ADC提供1.5~3.5V的內部參考電壓。外部也可以參考選擇適合ADC精度和溫度漂移要求的應用,如圖2所示。

D0-D11是并行數據輸入/輸出口;CS1為芯片的片選信號;RD和WD分別為讀寫信號;CONV_CLK為提供給AD芯片的工作時鐘信號;SYNC為數據同步信號;REFP和REFM為AD的參考電壓,可以選擇內部或外部參考電壓,本設計中采用了內部參考電壓;BVDD和DVDD是數字正電源,AVDD是模擬正電源;BGND和DGND是數字地,AGND是模擬地;AINP、AINM、BINP、BINM為模擬信號輸入的四個通道。

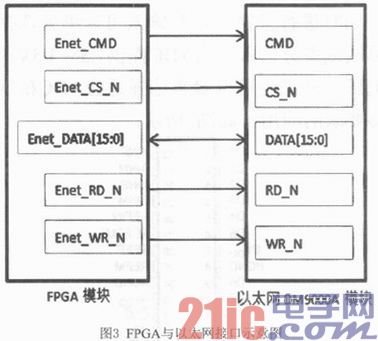

FPGA和上位機的數據通信需要由以太網模塊來完成。以太網采用高速DM9000A芯片,該芯片是臺灣DAVICOM公司推出的一款高度集成、功能強大、引腳少、性價比高的單片快速以太網控制芯片,非常適用于嵌入式系統設計。DM9000A主要特性是:集成10/100M物理層接口;內部帶有16K字節SRAM用作接收發送的FIFO緩存;支持802.3以太網傳輸協議;體積小,只有48個引腳;功耗非常低,單電源3.3V工作,內置3.3V變2.5V電源電路,I/O端口支持3.3~5.0V的容差。FPGA與以太網的接口示意圖如圖3所示。

3 多通道并行處理

由于FPGA具有并行處理的優勢,在高速多通道同步采樣中,更能滿足設計的要求。選擇硬件描述語言為Verilog,它能夠在多種抽象級別對數字邏輯系統進行描述,可以顯式地對并發和定時進行建模。本設計是四片AD芯片的同步高速采樣,利用FPGA具有的自定義外設以及自定義指令的功能,對于四片AD芯片實現了同步采樣的控制,并對數據并行處理。

3.1 單片ADC的控制

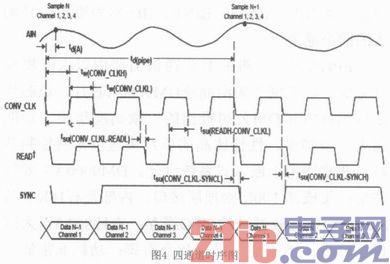

AD芯片THS1207的單通道采樣的最大采樣速度是6MSPS,四通道采樣的最大采樣速度是1.5MSPS,本設計采用的是四通道同步采樣模式,四通道時序圖如圖4所示。

在轉換過程中ADC有一個自由運行的外部輸入時鐘CONV CLK。隨著每一個CONV CLK信號下降沿,四個通道模擬信號轉換后的值提供給相應的讀出信號中的數據總線。READ+是,CS1三者的邏輯集成信號,READ+為低電平時表示讀有效。信號SYNC是低電平時,第一個通道的數據到數據總線,隨后SYNC拉高,第二、三、四通道的數據按順序依次讀取。

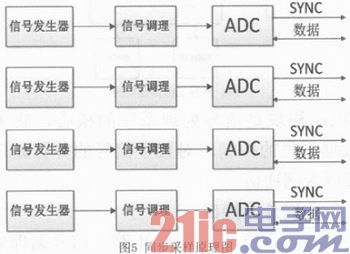

3.2 多片AD的同步采樣及并行處理

單個AD的控制完成后,就很容易擴展到對四片AD的控制。在采集多通道數據時,需要保持同步采樣,本設計采用的方法是每一路信號通過各自的信號調理電路和ADC轉換結束后,ADC保持數據,由FPGA依次讀取。

在硬件布局時,四片AD共用數據線,讀寫信號和AD轉換時鐘信號。因此FPGA通過寫命令同時啟動這四片AD芯片,十六個通道的模擬信號進入AD。每片AD都有一個數據同步信號SYNC,當判斷得到四片AD中的某個SYNC信號是低電平時,則可認為十六道數字信號已同步到位,通過片選信號的切換依次讀取各個AD芯片的數據并暫時儲存在寄存器中。也可以根據自己需求,開啟和關閉某些AD,選擇特定的通道數據進行讀取。同步采樣原理圖如圖5所示。

3.3 自定義指令

自定義指令是FPGA的嵌入式軟核nios ii的一大特色,nios ii有著一個開放式的ALU,用戶可以根據自己的要求添加自定義指令來實現應用需求,大大體現了nios ii軟核的靈活性。自定義指令的功能是運用Verilog語言,由電路模塊來完成的。因此,相比較利用C語言編程來實現功能,自定義指令具有執行速度快的顯著特點。Nios ii支持四類自定義指令:組合邏輯指令、多周期用戶自定義指令、擴展用戶自定義指令、內部寄存器自定義指令來滿足各種應用情況。

本設計中旋轉機械的振動信號雖然在硬件中經過了信號調理,但是由于元器件間參數的問題,仍舊會存在數據的偏差,運用了自定義指令中的多周期用戶自定義指令將數據進行修正。多周期指令需要數據指令和邏輯指令。利用start信號開始執行指令,done信號來表示執行結束,可以返回結果。

同時對于采集得到的數據進行傅里葉變換、濾波等處理,通過自定義指令也能實現,提升了FPGA的信號處理能力。

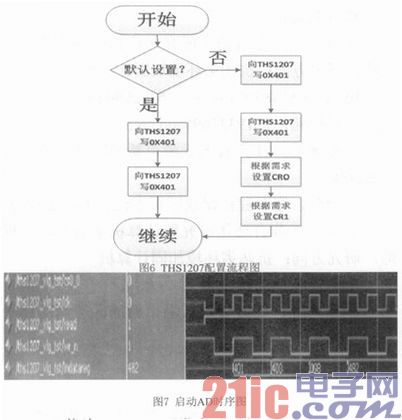

4 AD時序仿真

仿真在FPGA的開發中扮演了重要的角色,利用modelsim仿真軟件來對編好的AD程序進行時序驗證。AD正式工作前,需要通過向AD內部控制寄存器、CR1寫命令啟動AD,然后才能讀取數據。啟動AD芯片THS1207的流程圖如圖6所示,啟動AD的仿真結果如圖7所示。

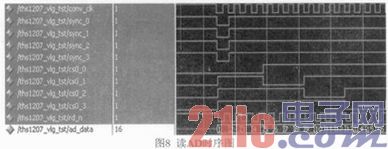

AD芯片THS1207正常啟動后就可以開始讀取各個通道的數據,由于本設計是十六個通道依次采樣,采樣結束后,需要通過片選控制信號依次讀取各個通道的數據,仿真結果如圖8所示。

從仿真結果驗證得到編寫的AD程序可以完成十六道采樣的設計要求。

5 實驗結果

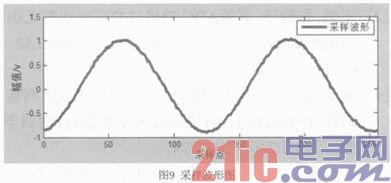

實驗采用AD四通道同步采樣,利用信號發生器產生正弦波,選擇同步采樣方式對每個正弦波采樣128點,通過以太網傳送到上位機,采樣得到的波形如圖9所示。

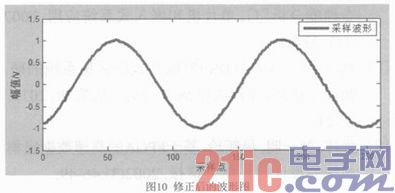

可以利用FPGA的自定義指令,根據需求將得到的數據進行處理,如圖10,對得到的波形數據進行偏置為-10和放大倍數為1.05的修正。

實驗中當信號發生器發出正弦波的頻率達到3000Hz時,即采樣頻率達到384kHz時,FPGA采集波形能力達到了最大值,相當于180000r /min的旋轉機械的基頻信號。當超過3000Hz時,采樣得到的波形會出現毛刺現象。分析原因,主要是由于nios ii進、出中斷服務程序,以及中斷服務程序中對采樣數據的讀取需要花費一定的時間。

6 結束語

本設計利用FPGA并行技術、自定義模塊化設計以及nios ii的特色功能即自定制指令,實現了對于旋轉機械振動信號的多通道高速同步采樣。顯示了FPGA可編程、設計靈活、高速的特點,同時也驗證了基于FPGA的多通道高速采樣系統的可行性。

根據實驗結果和理論的最大采樣速度還有差距,可以進一步改進系統設計,例如采用DMA優化程序,提高速率。

評論