FPGA數字核脈沖分析器硬件設計解析

國內譜儀技術多年來一直停留在模擬技術水平上,數字化能譜測量技術仍處于方法研究階段。為了滿足不斷增長的高性能能譜儀需求,迫切需要研制一種數字化γ能譜儀。通過核脈沖分析儀顯示在顯示器上的核能譜幫助人們了解核物質的放射性的程度。

本文引用地址:http://www.104case.com/article/201610/308486.htm1數字多道分析儀的優勢

國內很大一部分學者采用核譜儀模擬電路的方式實現脈沖堆積的處理。由于整個過程都是由模擬電路來實現,所以一直受到多種不利因素的困擾:模擬濾波成形電路有限的處理能力達不到最佳濾波的要求;模擬系統在高計數率下能量分辨率顯著下降,脈沖通過率低;模擬電路固有的溫漂和不易調整等特點,導致系統的穩定性、線性及對不同應用的適應性不高;在脈沖波形識別、電荷俘獲效應校正等更復雜的應用場合模擬系統無法勝任。

相比來看,數字脈沖幅度分析系統的性能顯著優于模擬脈沖分析器。數字分析器有以下幾點優點:通過軟件實現,提高了系統的穩定性與可靠性;可以利用數字信號處理方法針對輸入噪聲特點實現優化設計,達到最佳或準最佳濾波效果;處理速度快,反堆積能力強,相同能量分辨率下脈沖通過率更高;參數由程序控制,調整方便、簡單。

2總體設計

本方案設計了一種基于可編程門陣列的多道脈沖幅度分析器的硬件平臺。圖1即為總體設計框圖,探測器輸出的核脈沖信號經前端電路簡單調理后,經單端轉差分,由采樣率為65 MHz的高速ADC在FPGA的控制下進行模/數轉換,完成核脈沖的數字化,并通過數字核脈沖處理算法在FPGA內形成核能譜,核能譜數據可通過16位并行接口傳輸至其他譜數據處理終端,也可通過LVDS/RS 485接口實現遠程傳輸。特別需要注意的是,由于高速AD前置,調理電路應該滿足寬帶、高速,且電路參數能夠動態調整的需要,以適應不同類型探測器輸出的信號,從而更好地發揮數字化技術的優勢。

圖1 總體設計框圖

3具體硬件設計

3.1前端電路

前端電路由單端轉差分和高速ADC電路組成。差分電路由于其良好的抗共模干擾能力而應用廣泛。由于調理電路輸出的脈沖信號為單極性信號,若直接送入ADC,將損失一半的動態范圍。設計中在運放中加入一個適當的偏置電壓,將單極性信號轉換成雙極性信號后再送入ADC,以保證動態范圍。將信號由單端轉換成差分的同時,進行抗混疊濾波處理,完成帶寬的調整。

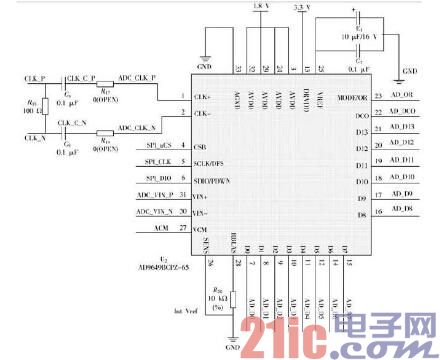

本設計使用AD9649 - 65高速ADC實現核脈沖的模/數轉換,AD9649為14位并行輸出的高速模/數轉換器,具有功耗低、尺寸小、動態特性好等優點。當信號從探測器通過調理電路,過差分轉單端電路后,以差分信號的形式進入ADC,在差分時鐘的控制下,轉換成14位數據,進入FPGA.該高速A/D在外部FPGA的控制下對信號進行采樣。然后將采樣后的數字信號送入FPGA中實現數字核脈沖的幅度提取。圖2為A/D轉換的原理圖,AD9649在差分時鐘的同步下完成A/D轉換,D0~D13為14個有效輸出數據位。

圖2 ADC電路原理圖

3.2 FPGA

目前國內外多道脈沖幅度分析的數字化實現主要有2種方案:純DSP方案、DSP+可編程器件方案。本文將充分發揮FPGA的并行處理優勢,在單片FPGA芯片上實現核脈沖的采集與數字核脈沖處理算法,經Quar-tus-Ⅱ軟件仿真與綜合,本文選用EP3C40 FPGA芯片實現多道分析器的數字化功能。

3.3接口電路設計

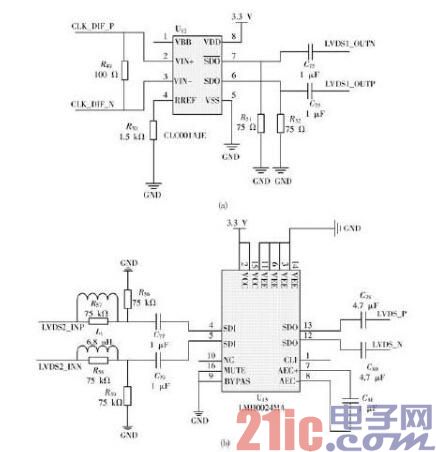

采用了LVDS和RS485兩種長距離數據傳輸接口,用于實現核能譜數據的遠程傳輸。LVDS即低電壓差分信號,是一種可以實現點對點或一點對多點的連接,具有低功耗,低誤碼率,低串擾,低噪聲和低輻射等特點。LVDS在對信號完整性、地抖動及共模特性要求較高的系統中得到了越來越廣泛的應用。圖3為低電壓、最高數據傳輸速率為655 Mb/s的LVDS接口電路。

圖3 LVDS長距離接受發送電路

在高速通信狀態下,其通信距離可達到幾百米。而RS 485接口采用平衡驅動器和差分接收器的組合,有很強的抗共模干擾能力和抗噪聲干擾能力。其最大的通信距離約為1 219 m,最大傳輸速度為10 Mb/s,傳輸速率與傳輸距離成反比,在100 Kb/s以下的傳輸速率下,可以達到最大的通信距離。

3.4電源電路

穩壓電源通常有兩類:線性穩壓電源和開關穩壓電源。開關電源的功率調整開關晶體管工作在開關狀態,極易產生嚴重的開關干擾,若采用開關穩壓電源,這些干擾將嚴重地影響數字多道分析器的正常工作,降低A/D轉換精度。所以本文采用線性穩壓電源為各功能模塊供電。線性穩壓電源的優點是輸出電壓比輸入電壓低,反應速度快,輸出波紋較小,工作產生的噪聲低。

本文設計的電源電路其輸入電壓為9~12 V,輸出電壓有5 V,3.3 V,2.5 V,1.8 V,1.2 V.線性穩壓電路為單端轉差分、ADC、FPGA、LVDS等各模塊供電。

4數字尋峰

NaI(Tl)探測器輸出信號通過調理電路后進入高速ADC,ADC進行連續高速的采樣,然后由FPGA完成數字核脈沖信號的積分、峰值檢測、閾值判斷等功能[8].由于當核能譜達到峰值時,其一階導數為0,據此可在連續的輸入信號中找到各核脈沖的峰值,并將該峰值對應道址的計數值加1,從而形成核能譜。為提高尋峰效率,尋峰之前需要對離散脈沖信號進行閾值判斷,對幅值低于閾值下限的信號不進行尋峰處理,可大大減少參與尋峰的離散核脈沖信號。

5功能測試

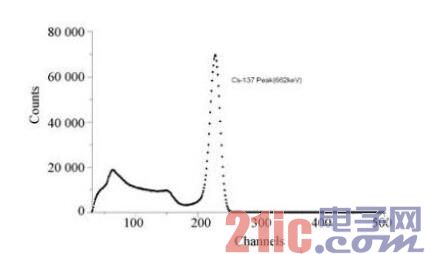

利用Borland C++集成開發環境開發了譜數據處理上位機軟件,軟件實現了能譜顯示、能譜數據管理、系統參數設置、RS 485通信等功能。圖4是本文設計的數字多道分析器分析137CS得到的1 024道能譜,其能量分辨率接近8%.

圖4 數字多道分析器實測

6結語

本文提出了一種基于FPGA的數字核脈沖分析器硬件設計方案。該方案在單片FPGA中實現了多道脈沖幅度的數字分析功能,通過軟件功能仿真和實際運行,說明了數字多道脈沖幅度分析器硬件設計的可行性,將FPGA應用到數字能譜測量系統能充分發揮其并行處理優勢,并能有效降低硬件電路設計的復雜度。

評論