基于CPLD/FPGA的VHDL語言電路優化設計

杜志傳,鄭建立

本文引用地址:http://www.104case.com/article/201610/308440.htm(上海理工大學 醫療器械與食品學院 上海 200093)

0 引 言

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起來的。它是一種面向設計、多層次的硬件描述語言,是集行為描述、RTL描述、門級描述功能為一體的語言,并已成為描述、驗證和設計數字系統中最重要的標準語言之一。由于VHDL在語法和風格上類似于高級編程語言,可讀性好,描述能力強,設計方法靈活,可移植性強,因此它已成為廣大EDA工程師的首選。目前,使用VHDL語言進行CPLD/FPGA設計開發,Altera和Lattice已經在開發軟件方面提供了基于本公司芯片的強大開發工具。但由于VHDL設計是行為級設計,所帶來的問題是設計者的設計思想與電路結構相脫節,而且其在設計思路和編程風格等方面也存在差異,這些差異會對系統綜合后的電路整體性能產生重要的影響。

在VHDL 語言電路優化設計當中,優化問題主要包括面積優化和速度優化。面積優化是指CPLD/FPGA的資源利用率優化,即用盡可能少的片內資源實現更多電路功能;速度優化是指設計系統滿足一定的速度要求,即用更多的片內資源換取更快的處理速度,常用于視頻信號采集系統和通信系統之中。面積優化和速度優化通常是一對矛盾,一般情況下,速度指標是首要的,在滿足速度要求的前提下,盡可能實現面積優化。因此,本文結合在設計超聲探傷數據采集卡過程中的CPLD編程經驗,提出串行設計、防止不必要鎖存器的產生、使用狀態機簡化電路描述、資源共享,利用E2PROM芯片節省片內資源等方法對VHDL電路進行優化。

1 VHDL電路優化設計的方法

優化設計是可編成邏輯設計的精華所在,如何節省所占用的面積、如何提高設計的性能是可編成邏輯設計的核心,這兩點往往也成為一個設計甚至項目成敗的關鍵因素。下面結合超聲探傷數據采集卡設計過程中,并基于Altera公司的EPM7192 CPLD芯片的編程經歷來論述VHDL電路的優化方法。

1.1 采用串行設計代替并行設計

串行設計是指把原來單個時鐘周期內完成的并行操作的邏輯功能分割出來,提取相同的功能單元,在時間上分時復用這些功能單元,在滿足系統速度要求的前提下,用多個時鐘周期來完成單個時鐘周期即可完成的功能。

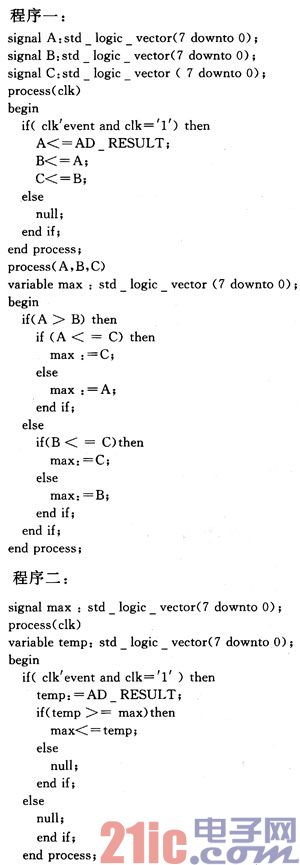

根據項目的要求,超聲探傷數據采集卡要有5個模擬通道,每隔125μs就會采集到330個點。如果等5個超聲通道采樣結束后再進行數據處理和傳輸,幾乎是不可能滿足該超聲探傷系統的實時性要求,而且數據量也遠遠超過ARM板上總線接口的傳輸速率2 MB/s。對于這么高的實時性要求,最好的解決辦法是在CPLD內部進行數據壓縮,即邊采集邊壓縮,以滿足系統使用的ARM板的總線速率要求。經過系統評估,每個超聲通道只需保留一個最大值即可滿足系統的性能要求。在這里,通過在三個8位數A,B,C中找出最大值的例子來說明串行設計方法的優勢,代碼如下所示。

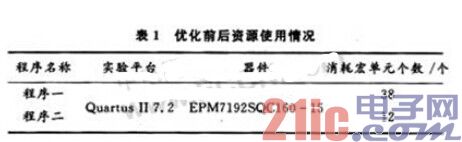

程序一是用并行方法設計,而程序二是采用串行方法設計。從表1的實驗數據可見,采用串行方法以后,電路的優化效果比較明顯。優化前,程序一需要消耗38個宏單元(Micro Cell),一個時鐘周期即可完成找最大值操作;優化后,實現相同的邏輯功能程序二僅需要12個宏單元,但需要3個時鐘周期才能完成一次運算,優化率達 68.4%。值得注意的是,此方法是以速度換取資源的方法,只適用于對速度要求不高的系統。

1.2 防止不必要鎖存器的產生

在 VHDL設計中,使用語句不當也是導致電路復雜化的原因之一,這使得綜合后的電路當中存在很多不必要的鎖存器,降低電路的工作速度。因此,在設計一個邏輯電路時,設計人員應該避免由于VHDL使用習慣的問題,無意識地在電路中添加不必要的鎖存器。由于IF或者CASE語句較容易引入鎖存器,所以當語句的判斷條件不能覆蓋所有可能的輸入值的時候,邏輯反饋就容易形成一個鎖存器。當然,隨著高級編譯軟件的出現,如QuartusⅡ7.2,這樣的問題通過編譯軟件已經得到很好的解決。對一個設計人員而言,有意識地防止不必要鎖存器的產生可以加快編譯速度。

在超聲探傷數據采集卡VHDL程序設計當中,涉及10 MHz系統時鐘clk的同步D觸發器的設計,即每當clk時鐘信號的上升沿到來時,將輸入信號in的值賦給輸出信號out,代碼如下所示。

通過對比,程序四比程序三只多了一條空語句,但這樣做可有效防止綜合器生成不必要鎖存器,并提高電路的工作速度。

1.3 使用狀態機簡化電路描述

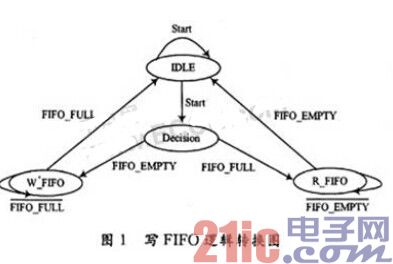

由于狀態機的結構模式簡單,有相對固定的設計模板,特別是VHDL支持定義符號化枚舉類型狀態,這就為VHDL綜合器充分發揮其強大的優化功能提供了有利條件。因此采用狀態機比較容易地設計出高性能的時序邏輯模塊,在超聲探傷數據采集卡的CPLD程序設計中,使用有限元狀態機(FSM)設計CY7CA225 1K×16 b FIFO芯片的讀寫控制模塊,并且達到很好的效果,邏輯轉換圖如圖1所示。實踐證明,實現相同的邏輯功能,使用狀態機設計能使設計的電路得到更好的優化。

1.4 資源共享

資源共享的思想是通過使用數據緩沖器或多路選擇器等方法來共享數據通道中占用資源較多的模塊,如算法單元。通過共享電路單元模塊可有效提高芯片內部資源的利用率,達到優化電路的目的。

1.5 利用E2PROM芯片節省片內資源

在用VHDL進行項目開發的過程中,經常需要存儲一些配置參數值。理論上講,每存儲一個字節的配置參數需要使用8個CPLD宏單元,因此在CPLD內部存儲這些參數并不是好的方案,除非使用的CPLD芯片已集成了E2PROM存儲單元。例如,在設計超聲探傷系統的數據采集卡的過程中,每個通道的采樣數都需要保存在CPLD里面。由于項目初期芯片選型不當,選擇一款EPM7192S160-15,該款芯片內部只有192個宏單元,因此考慮把參數存儲在外擴的 E2PROM芯片24WC02中。經實驗證明,在CPLD內部實現一個I2C控制器僅需要43個宏單元。由此可見,當初始化參數大于5個的時候,通過外擴 E2PROM芯片來存儲配置參數是可行的,只需在CPLD/FPGA芯片內實現I2C控制器即可方便地讀寫E2PROM存儲芯片。

2 結語

使用VHDL進行CPLD/FPGA電路設計時,要根據實際項目的具體情況,合理地劃分項目功能,并用VHDL實現相應的功能模塊。用模塊來構建系統,可有效地優化模塊間的結構和減少系統的冗余度,并在模塊設計過程中始終貫徹以上的優化設計原則,借助于強大的綜合開發軟件進行優化,才能達到最優化電路的目的。

評論