基于FlexRay的飛行仿真計算機1553B單元設計

MIL—STD—1553B(以下簡稱1553B)總線標準是美國于20世紀70年代提出的飛機內部電子系統聯網標準,由于具有可靠性高、實時性好、使用靈活等優點,廣泛應用在軍用有人和無人機中。我國于1987年建立了與1553B相應的國家軍用標準《數字式時分制指令/響應型多路傳輸數據總線》(GJB 289-1987),并于1997年對原標準進行擴充和修訂(GJB 289A-1997),一直沿用至今。

本文引用地址:http://www.104case.com/article/201610/308371.htmFlexRay總線是一款新型時間總線,具有高速率,時間確定性,信道容錯冗余功能,完全滿足新型分布式結構飛行仿真計算機內部總線數據通信需求。根據分布式結構飛行仿真計算機對1553B通信接口的需求,本文設計了基于FlexRay總線的飛行仿真計算機1553B接口單元。

1 分布式飛行仿真計算機簡介

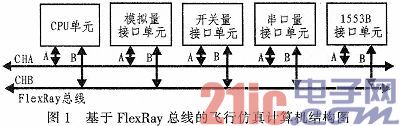

典型的基于FlexRay總線的分布式飛行仿真計算機由中央處理單元、串口量單元、模擬量單元、開關量單元及1553B接口單元組成。其中CPU單元是分布式飛行仿真計算機的核心主控單元,其功能主要通過CAN總線接收其余四個功能模塊的上行數據,經控制律解算及邏輯管理后,將數據下行傳輸給各功能板。其結構圖如圖1所示,本文設計研究一種基于FlexRay新型總線的1553B接口單元。

2 1553B節點硬件電路設計

基于FlexRay總線的飛行仿真計算機1553B接口單元以FPGA作為主控制芯片,FPGA采用Altera公司Cvclone III系列的EP3C25Q240芯片。選擇該芯片的原因是由于FPGA硬件連接靈活,編寫程序簡單,且該芯片IO口資源豐富。

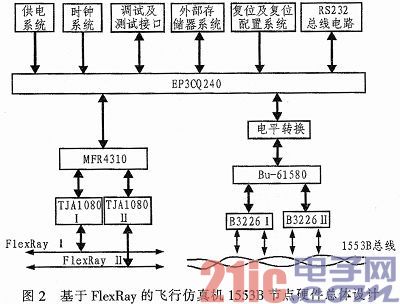

圖2為基于FlexRay的飛行仿真機1553B節點硬件總體設計。如圖2所示,本設計采用BU-61580S3作為1553B主控芯片。BU-61580集成了雙通道1553B信號的收/發器,內部有4K字的RAM用于1553B消息存儲,簡化了用戶程序設計。采用B3226作為1553B總線變壓器,B3226主要功能是將1553B總線電平標準轉換為TTL電平。而由于BU-61580的IO接口為5 V電平接口,而EP3CQ240的IO電平為3.3 V,故在FPGA與BU-61580之間需要通過一個電平轉換模塊進行電平匹配。

FlexRay節點有3種架構方式,分別為微處理器(MCU)+通訊控制器(CC)+總線驅動器(BD),微處理器+總線驅動器,微處理器3種。其中前兩種架構已經實現,本設計采用微處

理器+通信控制器+總線收發器的架構模式,其中通信控制器采用MFR4310,它是飛思卡爾半導體公司推出的一款面向汽車的FlexRay設備,它的物理層通道有兩個獨立的發送/接收通道,每個通道的傳輸速率可達10Mbit/s。通信控制器兩路通道的總線控制器采用TJA1080,TJA1080是恩智浦半導體公司推出的FlexRay收發器,它提供了1Mbit/s到10Mbit /s的傳輸率,可以配置成主動星型或者節點收發器。

為了保證系統正確無誤運行及調試方便考慮,本設計還增加了供電系統、時鐘系統、調試及測試接口、外部存儲器系統、復位及復位配置系統、RS232總線電路6個模塊作為輔助功能。

2.1 1553B接口設計

2.1. 1 BU-61580與FPGA接口設計

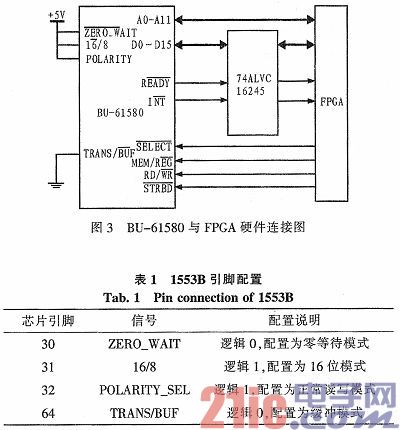

BU-61580芯片為DDC公司使用最為廣泛的控制芯片,擁有多種操作模式,如透明模式、緩沖模式,本設計采用緩沖模式。如圖3所示,通過將BU-61580的16/8引腳連接至VCC,TRANSPARENT/BUFFERED、ZEROWAIT引腳連接至GND,將BU-61580的工作模式設置為16位零等待緩沖模式,具體管腳配置見表1。

由于BU-61580的輸入高電平閾值為2 V,輸出高電平為5 V,而FPGA的工作電平為3.3 V,故FPGA的輸出電平可用于驅動BU-61580,但BU-61580輸出信號至FPGA過程中需要外加電平轉換芯片。本設計采用的是SN74ALVC164245作為電平轉換芯片,該芯片擁有十六位電平轉換長度。

BU-61580的時鐘采用外部有源晶振,CLOCK引腳接16M有源晶振,根據GJB 289A-97要求,晶振的長期穩定性為0.1%,短期穩定性為0.01%。

2.1. 2 BU-61580與收發器接口設計

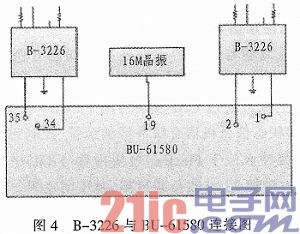

本設計采用的隔離變壓器芯片為B-3226,該芯片每個通道通信可以達到1 Mbit/s,可以提供很好的通信帶寬,具有強大的容錯傳輸功能。耦合變壓器與BU-61580硬件連接如圖4所示,BU-61580內部擁有兩路1553B收發器分別與隔離變壓器B-3226相連,B-3226將1553B電平邏輯轉換為TTL邏輯電平,進而將處理后的信號送入BU-61580內部的收發器中,實現一次1553B接收通信。

2.2 FlexRay接口設計

本設計中,選擇MFR4310作為FlexRay總線主控芯片,該芯片具有兩條通信通道,每條通道速率可配置為:2.5,5,8,10Mbit/s;TJA1080作為獨立的FlexRay收發器,具有低電磁輻射特性。外界傳感器數據通過1553B總線傳輸至本板卡后,經FPGA預處理后通過FlexRay總線發送至CPU單元中,從而實現一次CPU讀取外部傳感器信息。

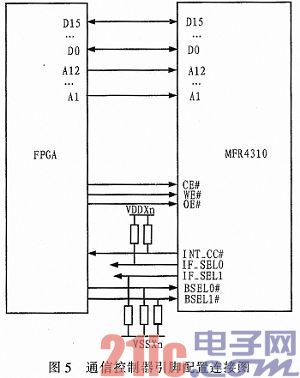

2.2.1 通信控制器與處理器接口設計

MFR4310與處理器擁有3種連接模式,分別為:異步存儲器接口(AMI)、MPC接口、HCS12接口。硬件設計通過配置IF_SEL0和IF_SEL1兩個引腳來選擇哪種接口模式。按照飛思卡爾官方推薦連接電路,MPC接口主要為MFR4310與PowerPC處理所設計的接口,而HCS12接口主要為MFR4310與HCS12系列處理器所設計的接口,由于本設計采用的處理器為FPGA,故采用異步存儲器接口。具體硬件連接圖如圖5所示,AMI接口將通信控制器配置為異步存儲器從設備,進而能夠與多種處理器進行數據交互,在AMI接口模式下,處理器通過控制CE#、0E#、WE#等信號實現與MFR4310數據交換。

圖5為通信控制器引腳配置連接圖,如圖5所示,由于本設計采用AMI模式,需要設置IF_SEL[0:1]為{2’h10},該值可通過將IF_SEL0引腳下拉、IF_SEL1引腳上拉來實現。

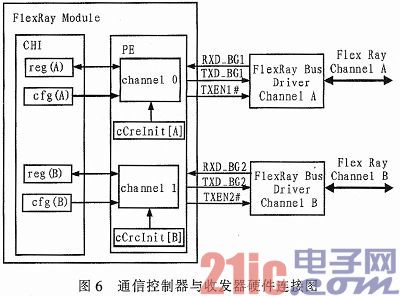

2.2.2 通信控制器與收發器接口設計

通信控制器與收發器硬件連接圖如圖6所示,FlexRay模塊內部主要由由控制主機接口(CHI)與協議引擎(PE)等部分組成,主機可通過CHI模塊訪問FlexRay功能模塊的配置、控制和狀態信息機消息緩沖區的配置、控制和狀態信息。這些消息緩沖區位于FlexRay模塊內存(FRM)中,用于存儲發送和接收的幀頭、有效負載數據、時序消息等。而PE模塊有TxA和TxB兩個發送單元及RxA、RxB兩個接收單元,分別用于兩個FlexRay通道發送和接收幀信息。

通信控制器通過信號引腳TxD、RXD、TXEN與總線收發器進行連接,正常高速通信模式下,當MFR4310通訊控制器的TJXEN [1:2]#引腳為高電平時,TJA1080的發送使能引腳TXEN有效,這時TJA1080的TXD輸入引腳把從通訊控制器TXD_BG[1:2]引腳輸入的數字位流,轉換成相應的模擬總線信號再輸出到FlexRay總線上;同時,TJA1080將FlexRay總線上的模擬總線信號轉換成相應的數字位流,從TJA1080的RXD引腳輸送到通訊控制器MFR310的RXD_BG2引腳上,完成總線與MFR4310通信控制器的數據通信。

3 軟件驅動程序設計

3.1 1553B總線軟件驅動設計

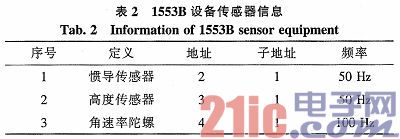

本設備1553B協議芯片工作于BC模式下,而其他傳感器模塊工作于RT模式,即:本設備工作于主模式,傳感器設備工作于從模式。當本設備需要傳感器信息時,發送數據請求幀,傳感器模式將相應數據發送至本設備。本設備要求接受的傳感器信息頻率如表2所示。

從上表可看出,各個傳感器的頻率并非完全一致。而BU-61580可以通過使用大小周期來支持多種頻率的數據傳輸,在自動發送模式下,可以通過設置小周期為100 Hz、大周期為50 Hz,進而實現數據幀按要求的速率進行傳輸。

BU-61580的程序初始化流程如下所示:

1)將該模塊設置為增強型BC模式,設置中斷屏蔽寄存器,初始化配置寄存器、時間標簽寄存器;

2)初始化內存空間,為3個傳感器分配內存初始地址及內存空間;

3)配置復位寄存器,啟動BC。

3.2 FlexRay總線軟件驅動設計

本設備接收外部傳感器信息,通過內部總線FlexRay發送至CPU板卡中,進而實現一次總線收發。FlexRay總線收發主要由總線控制器實現的,FlexRay總線控制器具體的通信流程如下。

總線控制器MFR4310的信息緩沖器(Message Buffer,簡稱MB)是用來存儲幀數據、配置、控制、狀態數據的結構。當總線通信時,MB是暫時存儲數據的物理介質,當數據發送時,應用程序將數據存儲于MB中,當周期輪轉至發送時槽時,硬件節點將數據從MB中取出發送至另一接收節點的相應MB中,實現一次數據通信。

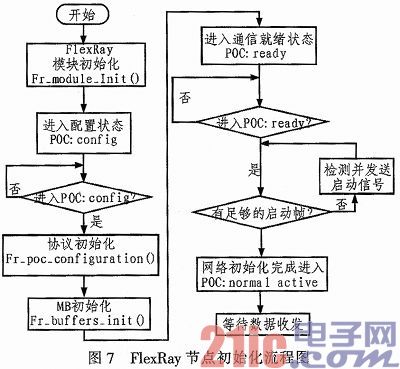

MB在使用前,必須經過初始化。FlexRay網絡節點的初始化包括初始化節點自身和初始化網絡。初始化自身由3步組成:

1)初始化FlexRay模塊。完成FlexRay模塊基地址存儲映射,重啟FlexRay通信控制器,進入配置狀態(POC:config),由函數Fr_module_init()完成;

2)FlexRay協議初始化。該步定義相關數據結構,實現網絡配置和節點通信任務分配,由函數Fr_poc_configuration()完成;

3)消息緩沖器初始化。初始化FlexRay通信控制器消息緩沖器與通信數據報文的對應關系,由函數Fr_buffers_init()完成。節點初始化自身完成后就進入通信就緒狀態(PO C:ready)。之后,進入初始化網絡階段,這階段通過發送啟動幀完成網絡啟動。根據表2的配置,節點ECU1和ECU2分別在時槽1和時槽4發送啟動信息幀,同時偵聽網絡中的啟動幀個數,直到網絡中有足夠的啟動幀啟動網絡,數據在正常主動狀態下(POC:nomal active)完成節點間通信。詳細流程圖如圖7所示。

4 總線網絡通信測試與結果分析

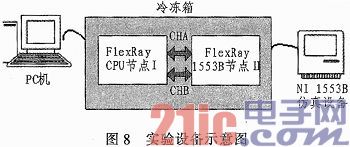

最后對所設計的基于FlexRay總線的1553B節點進行測試,其測試平臺如圖8所示。通過NI測試設備對傳感器數據進行模擬,進而產生一組傳感器數據,實現1553B總線通信。

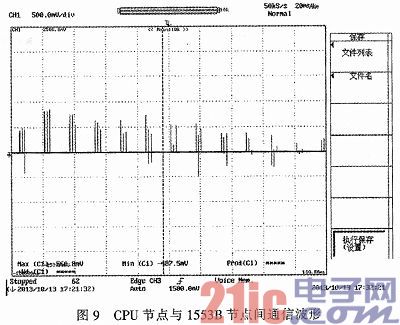

系統上電后,CPU板卡及1553B板卡進行寄存器配置,實現自身初始化,然后CPU板卡作為冷啟動節點發送10個冷啟動幀至FlexRay總線上,進行總線組網,1553B板卡接收到冷啟動幀后,立即加入FlexRay總線集群中,至此,總線準備完成。待總線準備完成,節點間開始通信,圖9為CPU節點與1553B節點間通信波形。

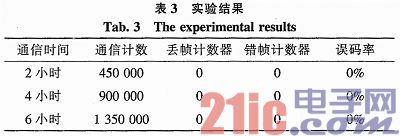

如圖9所示,FlexRay通信周期為16 ms,靜態時隙長度為50μs,將CPU板卡與1553B板卡進行通信實驗6小時,實驗結果如表3所示。

通過實驗結果可以得出,節點設計合理,本設備可準確接收外界1553B傳感器信息,并進行數據處理功能,可為新型分布式無人機飛行仿真計算機提供1553B通信接口。

5 結束語

1553B作為航空內部電子系統聯網標準,可設計為飛行仿真計算機的外部總線,而FlexRay為新型總線,具有速率快,多冗余等特點,可設計為飛行仿真計算機外部總線。這兩種總線各展所長,為飛行仿真計算機提供了快速、穩定的數據傳輸鏈路。本文設計了基于FPGA的1553B總線節點,通過與NI設備進行數據通信,結果正確,能夠滿足飛行仿真計

算機數據鏈路要求,為以后先進飛行仿真計算機新型總線FlexRay與1553B總線的應用打下了基礎。

評論