基于PCI CAN的數據轉換系統設計

CAN總線是當前最流行的工業現場總線之一,PCI則是一種應用普遍的高速同步總線,具有32 bit帶寬,時鐘頻率為0~33 MHz,最大傳輸速率可達132 Mbit·s-1,廣泛應用于數字圖像、語音及數據實時采集與處理等領域。本文利用PCI9054接口芯片、FPGA、微處理器與CAN收發器實現CAN總線與PCI總線問的快速數據交換。

本文引用地址:http://www.104case.com/article/201610/308312.htm1 總體設計

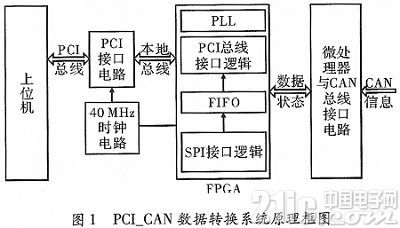

PCI_CAN數據轉換系統用于實現上位機的控制信息與CAN總線上各節點間的狀態、數據信息交換功能。系統通過PCI接口芯片與FPGA將上位機發出的控制信息發送給微處理器,由微處理器控制CAN收發器對CAN總線各節點進行查詢;同時CAN總線節點的狀態、數據信息上傳給CAN收發器,由微處理器控制將其送入FPGA中緩存,再由PCI接口芯片上傳至上位機做進一步數據處理、存儲操作。

PCI_CAN數據轉換系統主要由PCI接口模塊、FPGA邏輯模塊、微處理器與CAN收發器模塊及時鐘電路4部分組成,其原理框圖如圖1所示。

PCI接口模塊完成PCI總線與本地總線間的數據交換。FPGA完成對PCI接口芯片和微處理器的邏輯控制、總線仲裁等任務,且與微處理器之間通過SPI方式進行數據交換。由于CAN節點以“幀”為單位上傳數據,系統使用FPGA內嵌的內存塊生成FIFO,進行數據緩存;同時上位機的控制信號只有一個長字,無需FIFO緩存。微處理器與CAN收發器模塊接收來自上位機的控制信號,實現對各CAN節點的查詢、監視功能;同時控制CAN收發器,將CAN節點上傳的數據打包、發送至FPGA。時鐘電路由40 MHz和25 MHz軍品級晶振組成,提供PCI接口電路局部總線工作時鐘、FPGA主時鐘、微處理器工作時鐘。

2 模塊設計

2.1 PCI接口模塊設計

PCI9054是美國PIX公司生產的PCI橋接芯片,符合PCI總線規范,支持主模式、從模式及DMA傳輸方式,廣泛應用于嵌入式系統中。

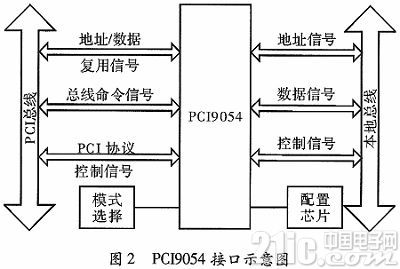

PCI9054在本模塊中的連接框圖如圖2所示,其中PCI總線信號與PCI連接器相連,包括地址/數據復用信號AD[31:0],總線命令信號C/BE[3:0],PCI協議控制信號PAR、FRA ME#、IRDY#、TRDY#、STOP#、PERR#、SERR#、IDSEL;EEPR()M接口信號直接與配置芯片連接,包括EESK、EEDO/EEDI、EECS;本地總線信號與FPGA相連,包括地址總線LA[13:2],數據總線LD[31:0],LBE[3:0]#字節使能信號及控制信號LW/R#、BLAST#、READY#、ADS#。

設置PCI9054芯片的MODE[1:0]管腳,選擇工作模式為C模式;配置PCI9054相關寄存器,設置數據傳輸方式為DMA和PCI從設備方式協同操作。DMA傳輸是在PCI9054控制下,完成PCI端存儲器和LOCAL端存儲器間的大數據量傳輸。

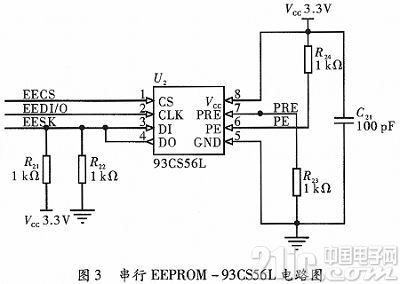

本文選用串行EEPROM芯片93CS56L。在系統復位后,完成對PCI內部寄存器的初始化配置,包括設備標識、狀態寄存器、控制寄存器、中斷寄存器、本地總線上設備的地址、空間等信息。由于需要對串行EEPROM進行寫操作,芯片須處于可編程且非保護狀態,如圖3所示。

2.2 FPGA邏輯模塊設計

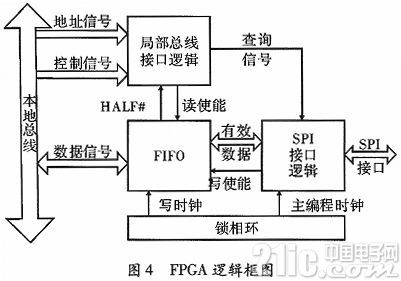

FPGA芯片選用Altera公司的Cyclone IV系列工業級芯片。EP4CE10E22I7,該芯片用戶可用管腳為92個,邏輯單元大小為10 320 bit,分布式RAM總容量144 kbit,嵌入式塊狀存儲器SRAM容量270kbit,可滿足設計需求;采用Verilog HDL語言進行邏輯設計,FPGA邏輯功能框圖如圖4所示。

上位機需查詢CAN節點狀態、數據信息時,PCI9054數據傳輸方式為PCI從設備。PCI總線主設備,即上位機,訪問PCI9054的本地空間,向內存空間寫一個長字的控制數據。本地總線將該數據讀出并發送至FPGA,通過微處理器對CAN總線某節點進行查詢。

CAN總線節點的數據上傳功能通過PCI9054的DMA模式實現。PCI9054集成了兩個相互獨立的DMA通道,每個通道都支持塊DMA和分散/集中DMA傳輸。塊DMA傳輸由上位機提供PCI總線和本地總線的起始地址、傳輸方向及傳輸字節數。在塊DMA傳輸中,作為PCI總線和本地總線的主控設備,PCI9054使能本地總線的中斷等待狀態;FIFO半滿信號HALF#有效時,FPGA拉低本地總線的LINT#信號,產生中斷;PC響應中斷,在中斷處理子程序中調用DMA程序,發起DMA傳輸;傳輸完成時,PCI9054設定DMA“傳輸結束位”結束DMA操作。

SPI接口邏輯接收、處理來自微處理器的幀數據,產生FIFO寫使能信號,并將去掉幀頭后的有效數據存入FIFO;鎖相環PLL用于產生FIFO寫時鐘與SPI接口邏輯主時鐘。

系統設計一次DMA傳輸數據為100 Byte,因此使用FPGA的內嵌內存塊生成FIFO。該FIFO深度為128 Byte,寬度為8 bit;且只緩存CAN節點的上傳數據,而不存儲上位機的查詢控制數據。本地總線接口邏輯單元根據控制信號、地址信號及半滿信號HALF#,產生FIFO讀使能,將有效數據傳輸至PCI9054;其中本地總線端時鐘信號LCLK作為FIFO讀時鐘。

2.3 微處理器與CAN收發器模塊設計

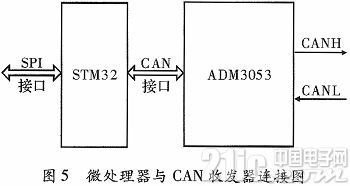

該部分電路由ARM公司的微處理器STM32F105、隔離型CAN收發器ADM3053組成,如圖5所示。

微處理器STM32F105集成CAN協議接口與SPI協議接口,可直接與CAN收發器連接,并將接收到的CAN數據、狀態信息加入幀頭,通過SPI口打包、發送到FPGA。

ADM3053集成了雙通道隔離器、CAN收發器和ADI公司的isoPower DC/DC轉換器;芯片內部振蕩器輸出一對方波,驅動內部變壓器提供隔離電源。該器件采用5 V供電,最高工作頻率為1 Mbit·s-1,其電路設計如圖6所示,圖中CAN_P、CAN_L作為差分信號線,以雙絞線作為物理層傳輸。

3 應用軟件設計

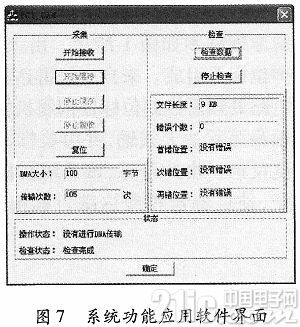

系統設計完成后,在Windows XP操作系統下,用C語言編寫應用軟件,并對系統功能與性能進行測試,軟件界面如圖7所示。

該應用軟件發送開始接收信號,查詢CAN節點數據和狀態,控制CAN節點向上位機發送采集到的數據與當前節點的狀態信息。上位機保存接收到的數據、狀態信息并對其進行檢查,顯示出錯位置。圖7所示為進行了105次DMA傳輸、且保存9 kB數據、對數據進行檢查后的顯示界面。該測試過程中,CAN發送的每幀數據為0~99連續變化的數據,通過測試可以驗證接收到的數據完全正確。

4 結束語

設計開發的PCI_CAN數據轉換系統,數據最高傳輸速率為1 Mbit·s-1,最遠通信距離>10 km,滿足CAN總線的性能要求。采用FPGA+PCI9054的設計使系統便于升級和移植;在多種不同型號計算機中運行,均未出現因與計算機不相容而產生找不到PCI卡或藍屏的現象,達到了設計和使用目的。

評論