基于FPGA的天線選通電路設計

某定向設備采用多普勒效應測向原理,即當天線振子做圓周運動時,天線振子本身與目標信號源就會產生相對速度,使振子感應到的信號產生了多普勒頻移,通過對振子感應信號相位的處理,從而達到測向的目的。而為了提高天線系統的可靠性、穩定性以及數據處理的可行性,采取的措施是利用脈沖電信號依次打通天線8根振子,通過取樣的步進方式代替振子的機械圓周旋轉,因此設計一個穩定可靠的天線選通電路就成為了系統的首要目標。傳統的方式一般都是采用數字集成塊電路實現,一方面需要的集成塊較多,電路板較大;二是容易受到外界的影響,脈沖的相位對準相對較難。為了解決以上問題,本文采用FPGA技術,對此電路進行了重新設計,并在電路設計過程中利用Quartus II軟件對設計電路進行了功能的模擬仿真,提高了電路設計的可靠性,簡化了電路設計與調試的難度,縮短了開發周期,有效的降低了開發成本,提高了設備生產、升級換代的效率。

本文引用地址:http://www.104case.com/article/201610/308306.htm1 電路設計

1.1 設計思想

本電路采用典型的自頂向下(Top—Down)設計結構。就是從系統總體要求出發,在頂層進行功能結構的劃分和設計,在方框圖一級進行仿真與糾錯,并用硬件語言對高層次的系統行為進行描述,在系統一級進行驗證。這樣以來,有利于早期發現結構設計中的失誤,避免設計浪費,同時減少了邏輯功能的仿真量,提高了設計的一次性成功率。

具體到本電路的設計,由于信號源采用的是規格為1224 kHz晶振,所要得到的打通天線振子的脈沖信號是8路有效電平依次到達的脈沖信號,即要求8路脈沖信號的相位依次嚴格對應。最后對低電平有效的打通脈沖進行反向驅動放大,從而得到我們所需要的天線打通脈沖,控制天線振子依次導通,實現多普勒效應測向。結合以上對電路功能的基本分析,利用自頂向下結構對電路進行設計,從輸入輸出信號關系看,需要由頻率高的信號得到信號較低的信號,因此,首先需要對信號進行分頻,同時由于信號源產生的是1路脈沖信號,而要得到的是8路打通信號,所以電路還要包括一個8分路的功能電路,具體可以采用計數、譯碼器來實現。

通過以上的分析,將電路整體功能分步、分模塊實現,首先進行分頻,將晶體振蕩器信號進行分頻,初步得到一路1.36 kHz方波信號,然后再將此一路方波信號分成8路170Hz打通脈沖信號,并使8路脈沖信號的有效電平依次出現,嚴格對準,保證在同一時間內只且只有一根振子被打通,從而滿足系統的要求,綜上所述,本電路中要包含分頻模塊、計數模塊和譯碼模塊(分路)以及外圍電路。

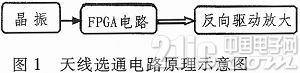

1.2 硬件電路原理示意圖

根據設計思想中對電路設計的分析,信號源和反向驅動放大電路為外圍電路,中間對信號的處理通過FPCA來實現,具體示意圖如圖1所示。

本文中電路采用了典型的Top-Down設計結構,也就是將電路分解成幾個相對獨立的功能模塊,通過VHDL編程實現后,生成獨立的元件,然后在TOP結構下調用生成的功能模塊或庫中已有的模塊,完成所要設計的電路,從而滿足電路功能的要求。因此電路可以分解成了分頻模塊和計數譯碼模塊(8分路)兩大獨立的設計單元,具體實現如下。

1.3.1 分頻模塊

設備中信號源頻率為1 224 kHz,因此要得到1.36kHz信號,就是對信號進行900分頻。通過VHDL語言可以直接實現900分頻,并得到占空比為1:1的分頻信號,但此方案過程中計數值較大,不利于電路實現,因此本文中采用多級分頻電路串聯的方式來實現,即采用三級分頻電路,第一級實現9分頻(輸出信號占空可以為1:1,也可以不是),后兩級采用10分頻(輸出信號占空比1:1),避免了單個過程計數過大的缺點,同時也滿足系統設計的需要。其中9分頻具體程序(占空比不是1:1)如下:

源代碼:

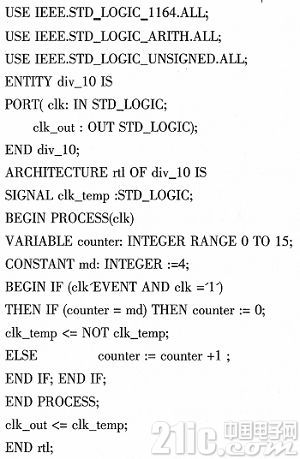

以上是9分頻模塊的源代碼,輸出信號占空比不是1:1,但不影響后面對信號的處理。在10分頻模塊中采用輸出占空比為1:1的方式,具體實現代碼如下。

源代碼:

1.3.2 計數譯碼模塊

要將1.36 kHz方波信號轉換成8路170 Hz的打通脈沖信號,可以通過計數和譯碼來實現。具體模塊設計為采用三位輸出的計數器和3—8譯碼器。其中VHDL源程序可以引用現成的標準源代碼來實現,也可以根據實際情況自行編寫,比較簡單,這里不再羅列。同時對于計數、譯碼這樣的通用模塊,可以在Top結構中直接從庫中調用。

2 電路的功能仿真及結果

2. 1 電路功能仿真

本電路的設計采用了Quartus II軟件進行功能仿真。Quartus II是Altera提供的現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)開發綜合環境。Quartus II支持Altera的IP核,包含了LPM/MegaFunetion宏功能模塊庫,使用戶可以充分利用成熟的模塊,簡化了設計的復雜性,加快了設計速度。此外,Quartus II通過和DSP Builder工具與Matlab/Simulink相結合,可以方便地實現各種DSP應用系統。其支持Altera的片上可編程系統開發,集系統級設計、嵌入式軟件開發、可編程邏輯設計于一體,是一種綜合性的開發平臺,適用于實際電路的設計與仿真,可以大大縮短電路開發的周期,提高設計的效率。

在分層電路設計中,Quartus II可以采用兩種結構。第一種結構就是每個模塊分別建立一個工程文件,在每個工程中分別調試單元電路,調試通過后,生成器件,然后再TOP中調用元件即可;另一種就是所有模塊文件統一放在一個工程文件中,每個模塊調試時設置成置頂即可,相互之間沒有影響,然后生成器件在Top文件中進行調用。本文電路的設計與仿真采用了第二種方法,統一放置在一個工程文件中,便于文件的管理,提高了設計與仿真過程的效率。

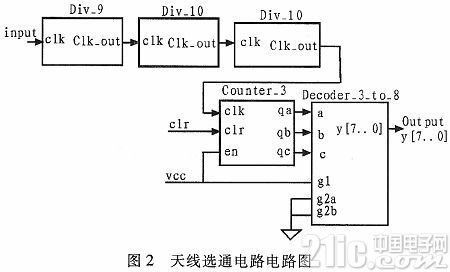

對于TOP-Down結構,頂層設計有兩種輸入方式,一種是采用VHDL語言編程,利用例化語句將各個組成模塊進行邏輯連接,從而實現電路功能;另一種方式就是采用電路圖輸入方式,分別調用庫中已有或編程生成的器件,最終實現電路設計實現。本文設計電路采用原理圖輸入的方式,在Top結構中最后形成的電路原理圖如圖2所示。

2.2 仿真結果與分析

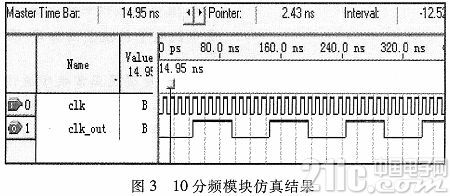

2.2.1 分頻模塊仿真結果

本電路中共有3級分頻電路,采用串聯方式連接,分別為一級9分頻和兩級10分頻,需要得到占空比為1:1的信號,因此10分頻電路輸出必須為占空比為1:1的方波信號,單10分頻模塊仿真結果如圖3所示,能夠得到占空比1:1的方波信號,滿足了電路的設計要求。

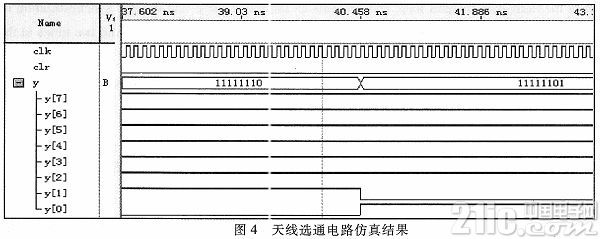

2.2.2 選通電路仿真結果

從上文中可以知道,設計天線選通電路的目的就是產生8路天線打通脈沖,且有效脈沖應該是依次出現的,每一時刻有且僅有一路信號是有效的,同時還應按照順序依次有效。本設計總體電路功能仿真結果如圖4所示。從仿真結果中可以看出,在輸入一路時鐘(CLK)信號的情況下,8路輸出端中每一時刻僅有1位為0,也就是1位有效,且為0的位是按順序依次出現的,因此電路設計輸出結果滿足系統對電路的要求,同時也說明電路設計是成功的。

3 結論

本文采用VHDL語言的層次化和模塊化的設計方法,對系統的邏輯行為進行描述,然后通過綜合工具進行結構的綜合、編譯、仿真,可在短時間內設計出高效、穩定、符合要求的電路系統,而且在不變化頂層文件的情況下即可任意升級、完善模塊電路。硬件描述語言VHDL為設計提供了更大的可移植性和可擴展性,使程序具有更高的通用性,較好的達到了系統對本電路的要求。同時,基于VHDL語言的FPGA技術是近年來新興技術,功能強大,速度快,應用領域光,在軍事、醫療、通信、視頻技術等領域都得到了廣泛的應用。雖然目前利用FPGA成本偏高,但是隨著產量的增加和應用的進一步拓展,成本必將進一步降低。因此,本文中電路設計采用了FPGA技術,符合設備未來發展需求,為將來設備的升級換代提供了必要保障。

評論