基于單通道DRFM的基帶干擾源設計

摘要 通過對單通道數字射頻存儲器的原理和結構分析,總結了單通道數字射頻存儲器的優缺點,并基于單通道數字射頻存儲結構,引入DSP模塊設計了一種基帶干擾源,實現了對寬帶信號的處理。

關鍵詞 數字射頻存儲器;基帶干擾源;數字信號處理

現代新型雷達普遍采用匹配接收和相參信號處理技術,因此具有優秀的目標檢測、識別和跟蹤能力,同時具有良好抗干擾性能。使用傳統噪聲干擾信號對相參雷達進行干擾,由于干擾信號不相參,能量利用率低、干擾效果差,迫使噪聲干擾機過度提高發射功率,為系統工程實現帶來困擾。因此,需要研究相參干擾技術以應對新體制雷達。

數字射頻存儲器(Digital Radio Frequency Memory,DRFM)利用高速模數轉換器件、高速數字邏輯器件進行采樣、存儲、處理雷達信號,可以產生相參干擾信號。DRFM技術已成為現代干擾技術的核心。

1 單通道幅度量化DRFM的結構及特點

幅度量化是指利用ADC對輸入信號幅度進行采樣、量化、編碼處理,得到數字信號。重構時,數字信號經DAC后輸出模擬信號。幅度量化的采樣頻率和量化位數決定了重構信號的保真度。

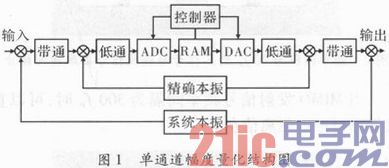

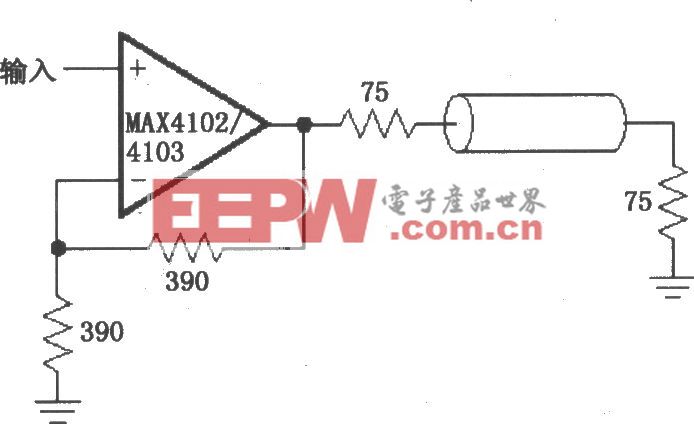

單通道幅度量化DRFM由一路ADC電路組成,其結構如圖1所示。工作流程為:輸入的射頻信號與系統本振進行混頻,經帶通濾波下變頻為中頻信號;中頻信號與精確本振混頻、濾波后,得到基帶模擬信號;ADC在采樣時鐘控制下,實現模數轉換,輸出數字信號存儲到RAM中;在轉發過程中,讀出數據經DAC、低通濾波后,重構為基帶模擬信號;此信號與系統本振混頻后,上變頻為射頻干擾信號。

假設下變頻后輸出信號的頻率范圍為[f0-△B/2,f0+△B/2],為抑制上變頻和下變頻的高次交調,其中心頻率f0與帶寬△B之間須滿足

2(f0-△B/2)>f0+△B/2 (1)

即

f0>3△B/2 (2)

根據采樣理論,采樣時鐘的頻率應滿足

fc>2(f0+△B/2)=2f0+△B>4△B (3)

由式(3)可知,單通道幅度量化的采樣率應該大于輸入信號帶寬的4倍。因此單通道幅度量化即便有結構簡單、不存在通道幅相不一致問題的優點,但由于ADC器件的限制,存在系統瞬時帶寬較小,難以處理寬帶信號的缺點。

2 基于單通道DRFM的干擾源設計

為解決寬帶信號處理問題而產生的正交雙通道DRFM存在幅相要求嚴格、調試困難的特點,為設計者增加了工作量。隨著技術的進步,目前ADC器件的性能有了大幅提高,為采用單通道DRFM處理寬帶信號提供了可能。

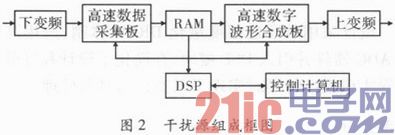

基帶干擾源主要完成對基帶信號的采集存儲、處理分析與基帶干擾信號的生成。包括上下變頻模塊、高速采集板、DSP數字信號處理板、控制計算機和高速數字波形合成器等部分。其組成框圖如圖2所示。

2.1 高速數據采集板

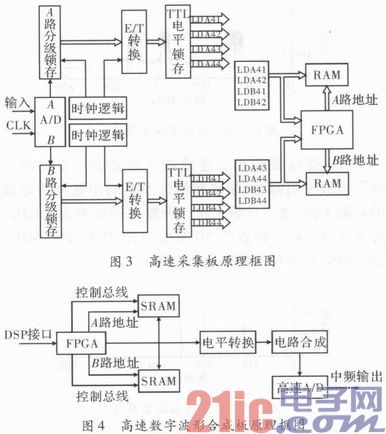

高速數據采集板主要完成模擬中頻信號到數字信號的變換,它將中頻信號進行量化處理,獲得數字信號并存儲。干擾源的瞬時帶寬要求為400 MHz,采用SPT公司的閃存A/D芯片SPT7760。SPT7760采樣率為1 GHz,雙路輸出,每一路均有鎖存時鐘,每個端口的輸出速度為500 MB·s-1。然后采用ADC輸出分為8路的方案,將每一路的數據產生率降為125 MB·s-1,輸出存儲及處理。由于ADC的輸出數據為ECL電平,而

后續的鎖存器和緩存器為TTL電平,所以在降速之前選用MICRE公司的SY100系列,將ECL電平轉化為TTL電平。

解決高速數據存儲的方法一般是在高速數據輸入和速度較低的大容量存儲器之間加入高速FIFO。由于選擇的FPGA與存儲器工作頻率相同,同為200 MHz。FPGA只需產生同步控制信號在一個時鐘周期內將TTL鎖存數據存入存儲器即可。同時FPGA還完成與DSP信號處理器的接口控制和數據轉換等功能。

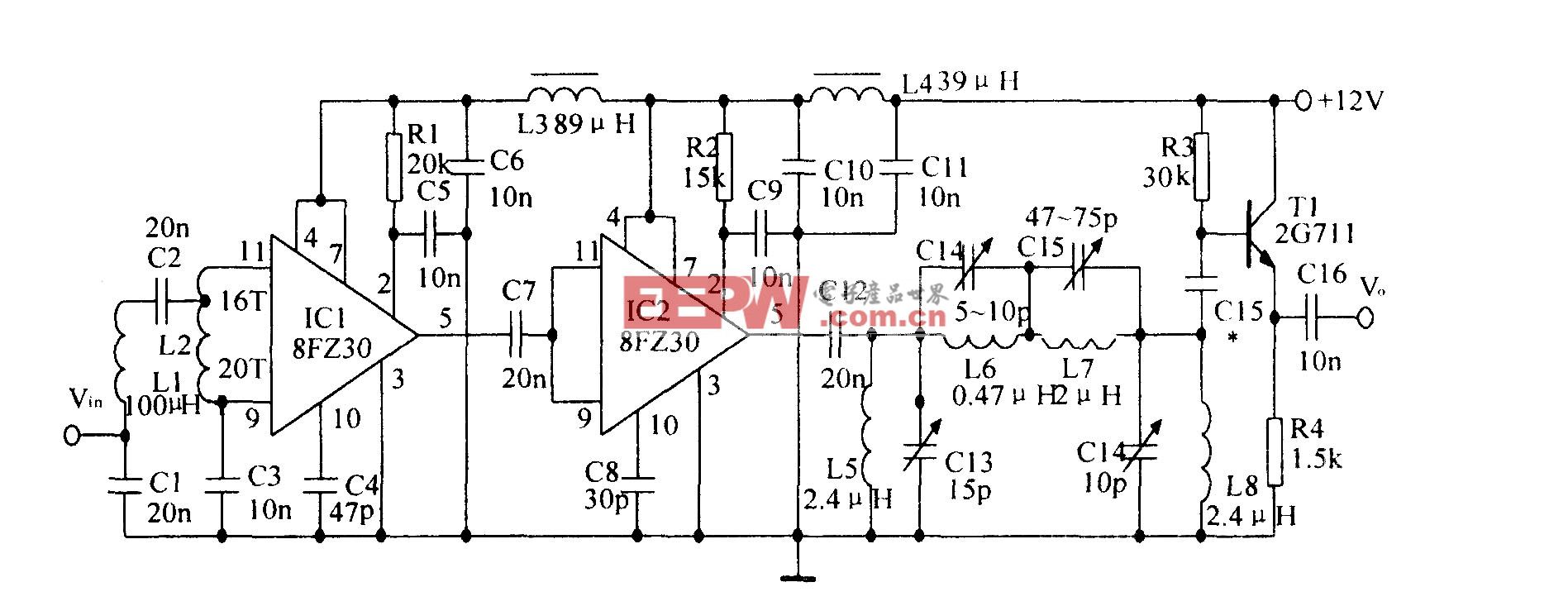

高速采集板的原理如圖3所示。

2.2 高速數字波形合成板

高速數字波形合成板實質是高速數字采集器的逆過程,它和高速數字采集器的區別在于它處理的信號是經過.DSP板分析、計算后的干擾信號,其原理框圖如圖4所示。設計采用Triquent公司的D/A芯片TQ6122。TQ6122是一款高速D/A轉換器,轉換速率為1GSa/s,具有8位數據位,功耗1.3 W。可廣泛用于直接數字頻率合成、高速任意波形發生器、寬帶視頻信號生成等方面。

2.3 DSP處理板

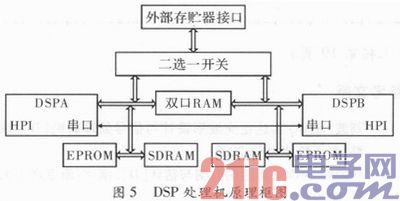

DSP信號處理機用于完成中頻采集后信號處理、分析以及干擾樣式的產生和部分系統控制的功能。核心處理器由兩片TMS320C6701組成,兩片處理器有獨立的存貯器資源,也有相互共享的存貯器資源,它們之間可以獨立工作也可以相互通信和交換數據,通信方式為串口通信或通過雙口RAM交換數據;DSP還提供數據總線、地址總線和讀寫信號等控制信號,并與外部高速數字波形合成器的數據接口或高速采集器的數據接口相接,以便交換數據和提供控制信號。DSP處理模塊組成原理如圖5所示。

3 設計仿真

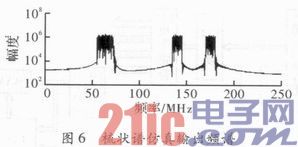

(1)梳狀譜輸出。梳狀譜干擾是針對多個信號或跳頻信號進行的窄帶噪聲干擾。在Matlab中采用3個獨立的帶限白噪聲經濾波,帶寬變為10 MHz、5 MHz、5 MHz后分別與65 MHz、140 MHz、175 MHz的本振混頻后在輸出,采樣時間設為1 ns,仿真結果輸出如圖6所示。

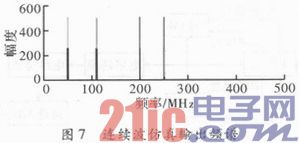

(2)連續波輸出。連續波干擾亦稱“非調制干擾”,連續發射幅度、頻率和相位不變的正弦波所形成的有源干擾,屬于點頻干擾。設置采樣頻率為1 GHz,脈寬1μs,4個頻點為50 MHz、110 MHz、200 MHz、250 MHz,仿真結果輸出如圖7所示。

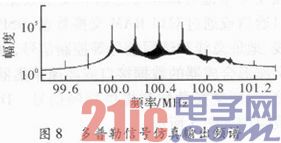

(3)多普勒信號輸出。多普勒干擾的原理是利用多普勒效應在接收到的目標信號上增加或減少多普勒頻移,形成拖速效果。根據多普勒頻移增加或減少,在雷達屏幕上會出現接近或遠離的移動虛假目標。設置3個信號的多普勒頻移為200 kHz、400 kHz、600 kHz,與本振100 MHz進行混頻,仿真輸出如圖8所示。

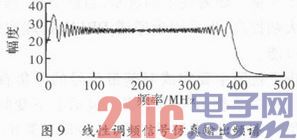

(4)線性調頻信號輸出。線形調頻干擾即掃頻干擾,在需要干擾的頻帶里進行掃頻,需要設置頻率上下限,脈沖寬度。設置采樣頻率為1 GHz,脈寬1μs,帶寬400 MHz,仿真輸出結果如圖9所示。

4 結束語

設計采用單通道幅度量化DRFM體制,選用高性能ADC器件并引入DSP模塊,在簡化了設計和降低了工程實現難度的同時實現了對寬帶信號的處理。

評論