基于ARM的分布式干擾機控制單元設計

在圖形界面編程中,多數時候需要對某些“事件”進行處理。例如,當用戶點擊某個按鈕時,應用程序便開始執行某種操作。在Qt開發中,通過一種被稱為“信號和槽”的機制來實現對象間的通訊。信號和槽機制,即當一個特定事件發生時,一個或幾個被指定的信號就被發射;槽即一個返回值為void的函數,如果存在一個或幾個槽和該信號相連接,那么在該信號被發射后,這個(些)槽(函數)就會立刻被執行。

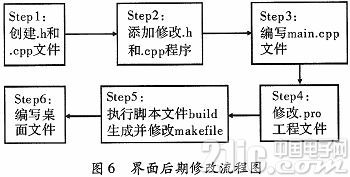

本文引用地址:http://www.104case.com/article/201609/303796.htm由于設計的控制單元采用大尺寸觸摸屏,而觸摸屏性能的調試是個重要問題,因為電磁噪聲的緣故,觸摸屏容易存在點擊不準確、抖動等問題。因此一般都要移植一個tslib來配合,在用戶層對觸摸屏的數據進行濾波和矯正,同時也可給應用程序一個統一接口。tslih能為觸摸屏驅動獲得的采樣提供諸如濾波、去抖、校準等功能,通常作為觸摸屏驅動的適配層,為上層的應用提供了一個統一接口。在PC端的界面設計完成后,后期修改流程如圖6所示。

經過上述步驟,將編譯好的可執行文件拷貝至開發板的opt/Qtopia/bin目錄下,將.desktop桌面文件拷貝至opt/Qtopia/apps/Application目錄下。重啟開發板,就可以在ARM觸屏的桌面應用上看到編寫的應用程序圖標,點擊運行就可以初步看到效果。

3 軟件功能設計

通過以上工作,可以在ARM開發板上看到整體的界面效果,但要實現該ARM控制單元的功能,還需要在界面程序中添加和修改代碼。

3.1 參數設置及數據的發送

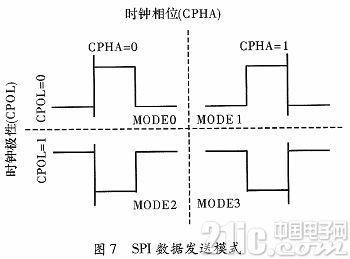

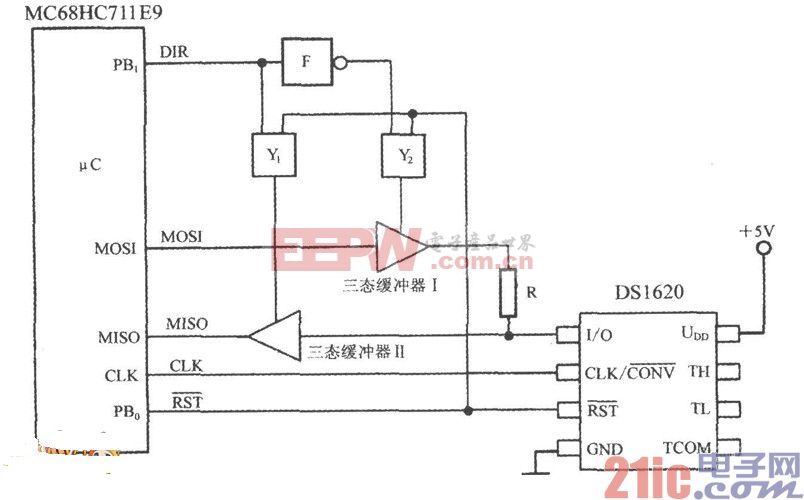

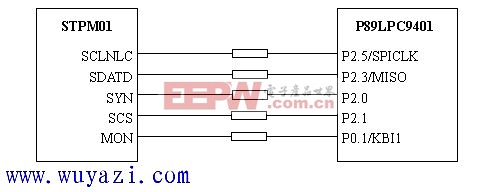

首先對所要發送的數據進行采集并打包。在發送數據之前,還需對已開發成功的SPI做配置。在SPI發送數據時,有4種模式可供選擇:(1)CPOL=0,CPHA=0。(2)CPOL=0,CPH A=1。(3)CPOL=1,CPHA=0。(4)CPOL=1,CPHA=1。4種情況分別為MODE0、MODE1、MODE2、MODE3,其中CPOL指時鐘信號的極性,表示當時鐘信號空閑時,其電平值為低電平0或高電平1。CPOL=0,時鐘空閑時為低電平,所以當時鐘信號有效時,即為高電平;CPOL=1,時鐘空閑時為高電平,所以當時鐘信號有效時,即為低電平。CPHA指時鐘信號的相位,對應著數據采樣是在第幾個邊沿(edge),是第一個邊沿還是第二個邊沿,0對應第一個邊沿,1對應第二個邊沿。

在本干擾機控制單元通信協議中,是采用模式MODE3。除了要對SPI發送數據的模式設置之外,還要設置SPI模式可寫可讀、SPI的bit/word可寫可讀、SPI的波特率可寫可讀等。將參數設置完成后,按照通信協議的約定,將界面信息對應成相應的數據,每8 bit為一組,每個word共16 bit進行發送即可。

3.2 SD卡存儲功能的設計

分布式干擾機在實際使用中,有時需要對設置的某些重要信息進行保存,所以利用Qt中的兩個易于合并使用的類:QFile和QDataStrcam。QFile對象表示磁盤上可讀取和寫入的文件。QFile是代表多種不同設備且應用更廣的QIODevice類的子類。QDataStream對象用于按順序排列二進制數據,以便儲存在QIODevice中并供以后檢索。讀取或寫入QIOD evice就如同打開數據流,然后讀取或寫入一樣簡單,只是參數為不同的設備。

3.3 定時功能的設計

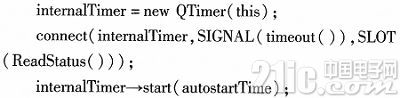

對于實際使用中的干擾機控制單元,需要發送干擾數據時,在界面上進行相應設置,即可直接發送。但是更多時候需要做的是讀取并顯示干擾機從環境中測到的數據,可以通過點擊界面上的更新按鈕,但是無法實時更新,所以這里設計一個能夠定時自動更新界面信息功能是必要的。定時功能主要利用Qt中的QTimmer類,其核心程序如下:

除此之外,在整個程序中的某些功能函數中,還要加上internalTimer→stop();這行令定時器關閉的代碼,原因是在有些界面參數進行設置后或讀取并顯示后,暫時無需定時讀取功能,所以就需關閉定時功能,待需要時再通過internalTimer→start(autostartTime)打開定時器即可。

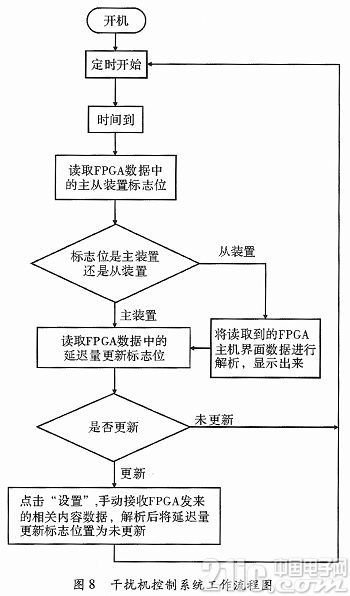

當整個程序的功能全部設計完成后,進行整體測試,流程如圖8所示,開機后,ARM會自動啟動干擾機控制單元界面,并開始計時。當定時時間到,ARM單元會讀取FPGA中的主從裝置標志位并進行顯示,若讀到從機,則將FPGA中的信息顯示到界面中;若為主機,直接讀取FPGA延遲量更新標志位。若為更新,則表示FPGA有新信息,需要點擊設置將當前界面更新為最新參數,然后開始重新計時。

3.4 運行測試

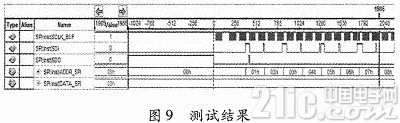

對設計好的分布式干擾機控制單元進行測試,按照與FPGA的通信協議,ARM界面信息轉化為數據后,每8位一組,兩組為一個信息單元進行傳送。反之,當FPGA對ARM發送數據時同理對數據進行解析。利用FPGA的邏輯分析儀對發送與接收的數據進行采樣,結果如下圖9所示。

圖9中,SCLK_BUF為時鐘信號,每8個時鐘脈沖為一個時鐘周期;SDI為ARM發送的數據,SD0為ARM接收的數據;ADDR_SPI與DATA_SPI為ARM發送數據的低8位與高8位。從圖中可以看出,ARM端發送的數據依次為00h,00h,01h,00h,02h,00h,03h,00h……。在FPGA一端,收到的數據同樣是00h,00h,01h,00h,02h,00h,03h,00h……,其中ADDR_ SPI的數據就是收到數據的奇數項,其中DATA_SPI的數據就是收到數據的偶數項。同時,在第3個有效脈沖周期到達時,ARM控制單元接收到來自FPGA的數據,這個數據解析后反映到ARM界面即為裝置屬性選項,界面會自動響應將裝置屬性選項設置為主裝置。

評論