更高性能/更低功耗的異步DSP核心設計

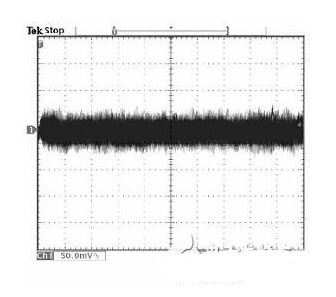

圖 1:同步DSP電壓波紋

本文引用地址:http://www.104case.com/article/201609/303587.htm

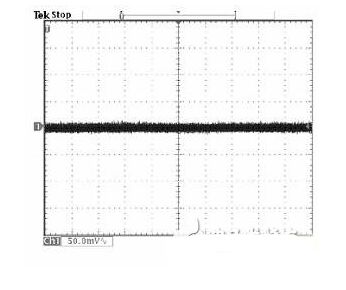

圖 2:異步DSP電壓波紋

在IC 設計人員眼中,更出色的切換性能代表更可靠的電路。電路同時發生大規模切換時,將產生非常大的瞬時電流。在設備的電網上顯示為IR降。這意味著電網的某一區域在此時的電壓較低。這是意料之中的正常情況,通常都通過設計驗證來確保電網能承受預計的最大電壓下降。有時這也是一種限制因素,妨礙設計人員在邏輯的特定區域進行進一步設計。

消除時鐘偏差:采用異步設計還有很多原因。低于90納米的硅片是生產的趨勢。這可以從硅制造商大力投入以糾正一系列問題上得以證明。他們已著手開發干涉計量學(Interferometric Metrology)等高級技術,

盡量使光罩的最小特征尺寸小于當前的曝光波長。

由于這些變量會提高設備的偏差量,因此在過程中控制它們非常重要。時鐘偏差被定義為時鐘信號到達電路中不同點的時間差。

由于相同時鐘上的所有邏輯必須有序地運行,因此時鐘偏差必須保持在最低水平,以確保電路正確運行。設備的時鐘頻率越高,可允許的偏差越小。

隨著特征尺寸的減少,時鐘偏差的問題將更加嚴重。相比以前,特定晶片中將分為“慢速”芯片和“快速”芯片;由于密度大幅增加,單個芯片中的變量也將有所體現。這種狀況的性質對于大型單片同步設備意義非常重大。

采用異步 DSP 核心可避免此類問題。DSP 核心基于小型自計時電路。因此所有定時對于該邏輯塊相關的小區域都是本地的。

穩定性更高:半導體主要受三大物理屬性影響:制作流程速度、電源電壓電平和溫度。如果這些特征發生任何變化,將造成晶體管運轉更快或更慢的情況。

同步電路必須在上述參數的最佳和最差狀態值下進行靜態時序分析(static timing analysis),以確保設備工作正常。換而言之,同步電路有一個可以使電路停止工作的“切斷點”。

由于異步電路是自計時電路,因此它們在物理特征變化時只須加速或減速。因為控制自計時的邏輯與處理邏輯處于相同區域,所以溫度和電壓等環境變化都會對兩者造成影響。所以,異步電路針對抵抗動態電壓下降等瞬時變化的抗影響性能更好,還將根據長期溫度和電壓變化進行自動調整。

橫空出世:通用異步 DSP

由于成功采用異步設計技術的各種設備不斷出現,異步設計正受到越來越多的關注。異步邏輯的優點眾所周知。包括低功耗和更穩定的設計等等。

直到最近,異步電路僅僅在非常必要時才使用。由于學術界的偏見,它們通常被視為邊緣產品。現在,許多商用設備已經開發了上述針對各類小眾市場的功能。

完全基于異步邏輯的通用 DSP 核心的出現表明,現有的工具、技術和知識創造的商用產品可應用于更大的客戶群體。更吸引人的是,該設備可與任何現有DSP一樣進行同樣的編程和操作。也就是說,這個解決方案在絲毫不影響可用性的基礎上,實現了異步技術的所有優點。

評論