基于DM368的視頻捕獲與編解碼系統(tǒng)設(shè)計(jì)

摘要:為了實(shí)現(xiàn)對(duì)視頻進(jìn)行捕獲后壓縮,文中提出一種基于DM368的視頻捕獲壓縮方案,并設(shè)計(jì)完成相應(yīng)的硬件與軟件。該系統(tǒng)主要使用 TI達(dá)芬奇DM368片上系統(tǒng)作為主控芯片,采用TVP5158作為視頻采集前端。采用1G容量的DDR2內(nèi)存作為易失性存儲(chǔ)器。采用1GFlash作為系統(tǒng)內(nèi)核與文件系統(tǒng)的存儲(chǔ)介質(zhì)。軟件部分在Linux平臺(tái)中使用達(dá)芬奇DVSDK進(jìn)行編程。壓縮規(guī)格上使用目前較為流行的MPEG4算法。從而實(shí)現(xiàn)視頻的捕獲與壓縮。經(jīng)實(shí)際測試顯示,使用該平臺(tái)進(jìn)行視頻捕獲壓縮開發(fā)較以往DSP和FPGA方案更加成熟穩(wěn)定,并可以通過TI的開發(fā)工具和現(xiàn)有軟件庫大大減少開發(fā)周期。

本文引用地址:http://www.104case.com/article/201609/303574.htm關(guān)鍵詞:DM368;MPEG4;視頻;TI達(dá)芬奇

隨著人類社會(huì)的進(jìn)步,視頻技術(shù)越來越發(fā)揮著重要的作用。視頻的傳輸也經(jīng)歷了由模擬到數(shù)字的轉(zhuǎn)變。數(shù)字視頻的分辨率也隨著感光元器件的革新而不斷增加,在給人們提供越來越清晰額視覺享受的同時(shí)產(chǎn)生了更大的視頻數(shù)據(jù)。針對(duì)海量的視頻數(shù)據(jù),人們通過改進(jìn)壓縮算法使得視頻數(shù)據(jù)所需的存儲(chǔ)空間大大減小。時(shí)至今日,ITU-T已經(jīng)公布了H.264壓縮標(biāo)準(zhǔn),并且在推進(jìn)H.265壓縮標(biāo)準(zhǔn)。在MPEG會(huì)議的努力下,MPEG-4壓縮標(biāo)準(zhǔn)也開始應(yīng)用于數(shù)字視頻領(lǐng)域。這些標(biāo)準(zhǔn)都使得高分辨率的視頻數(shù)據(jù)以非常高的壓縮率壓縮。最明顯的成果便是以網(wǎng)絡(luò)為媒體的實(shí)時(shí)視頻傳輸技術(shù)。而在硬件方面隨著微電子技術(shù)的進(jìn)步,微處理器體積變得越來越小但是處理能力如摩爾定律那樣快速增長。這些技術(shù)的進(jìn)步使得嵌入式設(shè)備實(shí)現(xiàn)數(shù)字視頻的捕獲壓縮成為可能。目前常用的設(shè)計(jì)方案常用 DSP+FPGA或者DSP+ARM組合實(shí)現(xiàn)。鑒于嵌入式設(shè)備對(duì)數(shù)字視頻壓縮的要求,誕生了許多現(xiàn)成的壓縮芯片,只需要發(fā)送指令和數(shù)據(jù)就可以完成原始視頻數(shù)據(jù)的壓縮。

多處理器組合,雖然可以既利用DSP芯片的數(shù)字信號(hào)處理能力,又利用協(xié)處理器的邏輯處理能力,但是這種組合屬于板級(jí)連接設(shè)計(jì)者在設(shè)計(jì)過程中難免會(huì)引入連接錯(cuò)誤,給項(xiàng)目開發(fā)帶來許多不穩(wěn)定因素,大大延長開發(fā)周期。同時(shí)兩種不同公司的芯片在設(shè)計(jì)過程中,接口邏輯會(huì)有或多或少的不同,也會(huì)給設(shè)計(jì)者帶來意想不到的問題。近年來許多芯片公司將核心處理器如ARM、DSP和其他外圍硬件內(nèi)核集成到一塊芯片中,這種System On Chip(SOC)技術(shù)大大增強(qiáng)了新的嵌入式視頻處理器的穩(wěn)定性。在其中TI公司開發(fā)出達(dá)芬奇系列視頻處理SOC,并提供了相應(yīng)的開發(fā)環(huán)境與成熟的視頻處理算法。2010年4月TI推出DM368視頻處理芯片。與之前DM365視頻庫軟件兼容,但提供了更為豐富的接口。

文中介紹一種使用達(dá)芬奇DM368SOC實(shí)現(xiàn)數(shù)字視頻的捕獲并按照MPEG4標(biāo)準(zhǔn)進(jìn)行壓縮的設(shè)計(jì)。本設(shè)計(jì)將對(duì)模擬視頻信號(hào)進(jìn)行采樣量化,將原始的視頻數(shù)據(jù)按照MPEG4壓縮標(biāo)準(zhǔn)進(jìn)行編碼。最后將編碼后的壓縮視頻解碼輸出,從而驗(yàn)證視頻的編解碼及視頻輸出功能。

1 總體設(shè)計(jì)

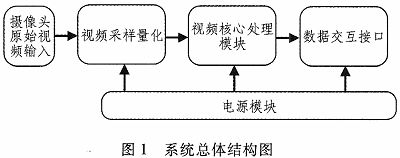

該嵌入式視頻處理設(shè)備整體結(jié)構(gòu)如圖1所示,模擬攝像頭采集的視頻信號(hào)經(jīng)過視頻處理前端,進(jìn)行按照一定視頻格式進(jìn)行采樣量化,將模擬視頻信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)。這些視頻原始數(shù)據(jù)被傳輸?shù)揭曨l處理模塊。然后通過該模塊將原始視頻數(shù)據(jù)進(jìn)行相關(guān)的視頻壓縮處理。本設(shè)計(jì)預(yù)留網(wǎng)口和模擬視頻輸出端口,可以將壓縮的視頻解壓輸出,并通過模擬視頻輸出端顯示在微計(jì)算機(jī)終端或者嵌入式顯示設(shè)備。

2 系統(tǒng)硬件設(shè)計(jì)

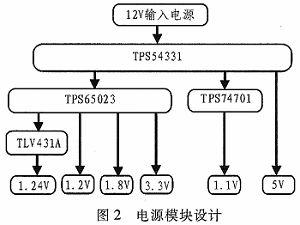

嵌入式視頻處理的硬件設(shè)計(jì)由視頻前端、視頻處理模塊、電源部分和外部接口四個(gè)部分組成。電源部分是一個(gè)嵌入式設(shè)備的最基礎(chǔ)模塊,是一個(gè)設(shè)備能夠穩(wěn)定運(yùn)行的基礎(chǔ)。該設(shè)備由于使用了多個(gè)芯片,每個(gè)芯片需要的供電電壓不同,這就需要使用多個(gè)電源芯片進(jìn)行電壓轉(zhuǎn)換產(chǎn)生對(duì)應(yīng)的供電電壓。本次設(shè)計(jì)中將輸入的12 V電源經(jīng)第一次電平轉(zhuǎn)換產(chǎn)生5 V電源。5 V電源經(jīng)兩個(gè)芯片轉(zhuǎn)換產(chǎn)生1.1 V、1.2 V、1.8 V和3.3V電源。最后產(chǎn)生的3.3 V電源經(jīng)轉(zhuǎn)換產(chǎn)生1.24 V電源。如圖2所示。

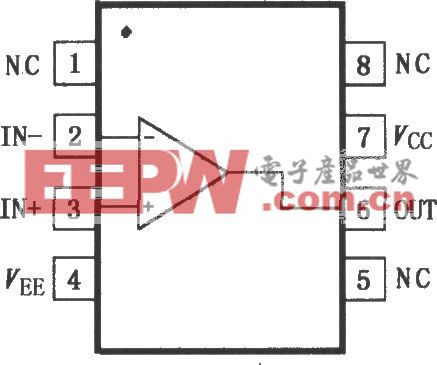

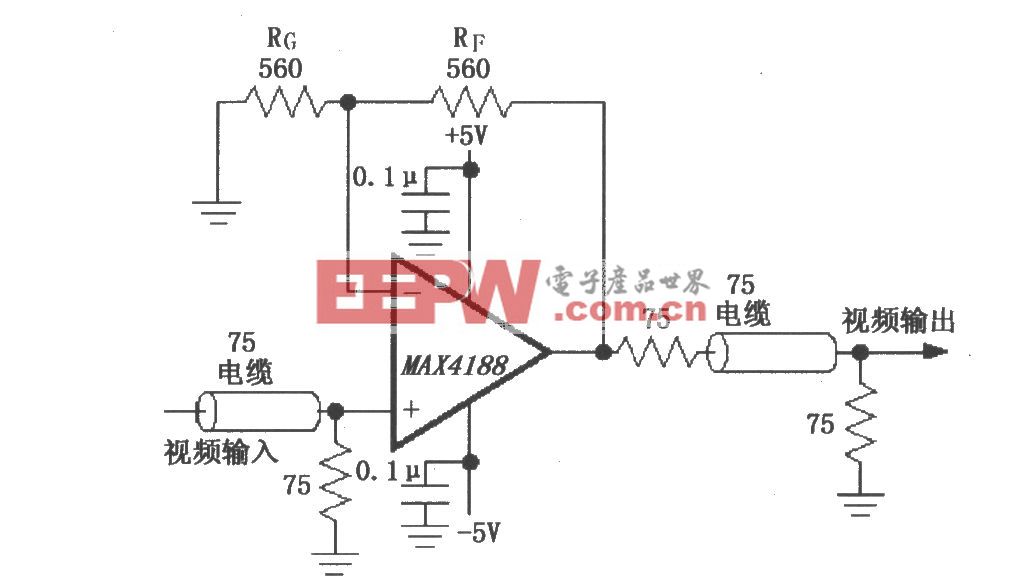

模擬視頻接入端連接至TVP5158進(jìn)行初步處理。TI公司的TVP5158是四路NTSC/PAL視頻譯碼器,具有單獨(dú)的定標(biāo)器,降噪,自動(dòng)對(duì)比度調(diào)整,以及靈活的輸出格式編制器。TV P5158提供和DaVinc處理器的音頻和視頻連接接口,視頻輸出端支持8位ITU—R BT.656和16位4:2:2 YCbCr。輸出端連接DM368視頻處理器。

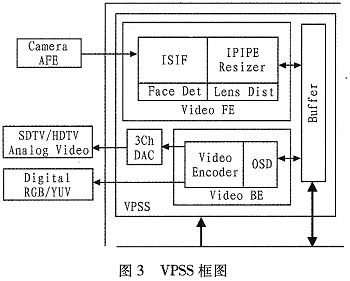

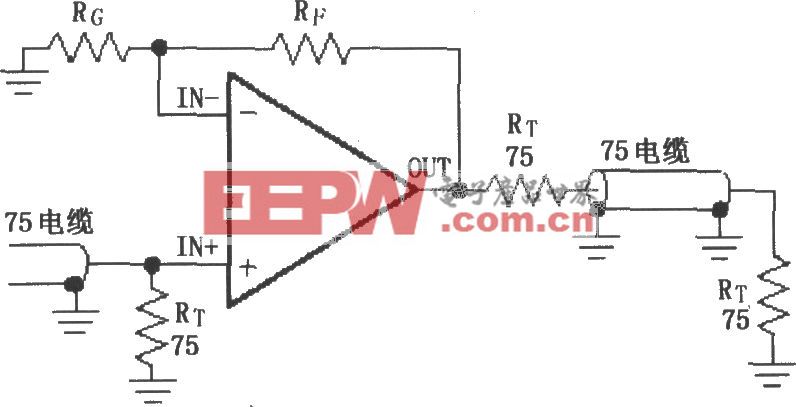

在DM368的片上系統(tǒng)中有許多硬件設(shè)備。對(duì)于視頻處理來說最重要的是其中的VPSS,即視頻子系統(tǒng)(結(jié)構(gòu)如圖3所示)。該系統(tǒng)有若干硬件組件支持對(duì)視頻的處理,可以實(shí)現(xiàn)從YUV422到Y(jié)UV420的格式轉(zhuǎn)換等具體處理操作。其中的VPFE(視頻處理前端)和VPBE(視頻處理后端)可以實(shí)現(xiàn)視頻數(shù)據(jù)的預(yù)處理和解碼輸出功能。除此之外,該系統(tǒng)中還有一個(gè)緩沖器和一個(gè)DMA控制器,可以充分使用外部DDR2存儲(chǔ)器。本次設(shè)計(jì)采用一片1G容量DDR2存儲(chǔ)器,該RAM與DM368的內(nèi)存引腳相連,為該芯片處理大數(shù)據(jù)視頻提供了足夠的運(yùn)行空間。使用三星公司的1G容量FLASH作為Linux系統(tǒng)內(nèi)核、文件系統(tǒng)和視頻應(yīng)用程序的存儲(chǔ)區(qū)域。

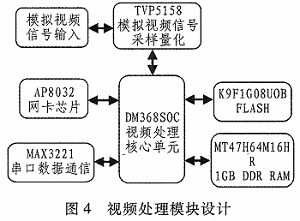

在視頻輸出部分,DM368自帶了模擬視頻輸出接口,另外考慮到嵌入式Linux的開發(fā)調(diào)試需求和目前常用的視頻傳輸方法,本次設(shè)計(jì)還添加了網(wǎng)絡(luò)和串口。網(wǎng)卡主控芯片采用

AR8032,串口部分采用MAX3221實(shí)現(xiàn)通信電平轉(zhuǎn)換。整個(gè)視頻處理模塊硬件設(shè)計(jì)如圖4所示。

3 系統(tǒng)軟件設(shè)計(jì)

TI公司為達(dá)芬奇系列視頻處理器設(shè)計(jì)了軟件開發(fā)構(gòu)架,方便開發(fā)者在這個(gè)構(gòu)架上開發(fā)自己的視頻處理程序。該軟件開發(fā)構(gòu)架核心為CODE ENGINE編程框架,它能夠自動(dòng)地請(qǐng)求和實(shí)現(xiàn)符合eXpress DSP的Codec算法。在code engine中為開發(fā)人員提供3種開發(fā)方向。作為算法開發(fā)人員,可以將設(shè)計(jì)好的視頻處理算法通過Codec部分,按照TI通用的視頻處理算法標(biāo)準(zhǔn)生成算法庫,并進(jìn)行打包。視頻應(yīng)用程序開發(fā)人員可以在APP部分調(diào)用已經(jīng)打包好的算法庫,開發(fā)自己的視頻處理應(yīng)用程序。在應(yīng)用程序與算法庫之間是sever部分,該部分可以實(shí)現(xiàn)Codec算法庫被APP調(diào)用。Server為Codec提供APP調(diào)用過程中所必須的組件(例如BIOS、Framework Component、DSPLink等),并生成可執(zhí)行文件[dv]。系統(tǒng)軟件設(shè)

評(píng)論