基于CPLD的LCD1602顯示系統設計與實現

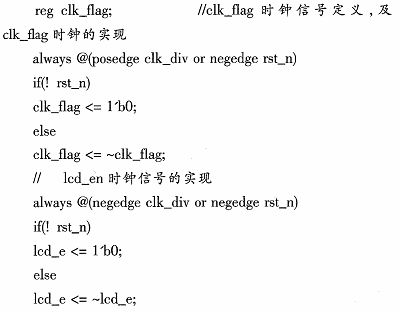

由clk_div時鐘信號獲取lcd_en及lcd_flag兩個時鐘信號,具體如下:

至此,只需捕獲clk_flag的上升沿,并在該跳變沿處送入指令或數據即可。而狀態之間的轉移關系則需按初始化的正確步驟進行,完成初始化后,指定DDRAM的地址,并向lcd_dat送數據即可實現數據的寫入操作。

4 仿真結果及實現效果

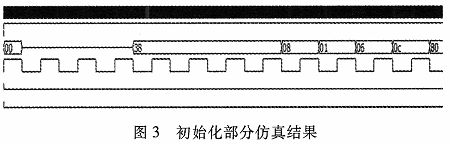

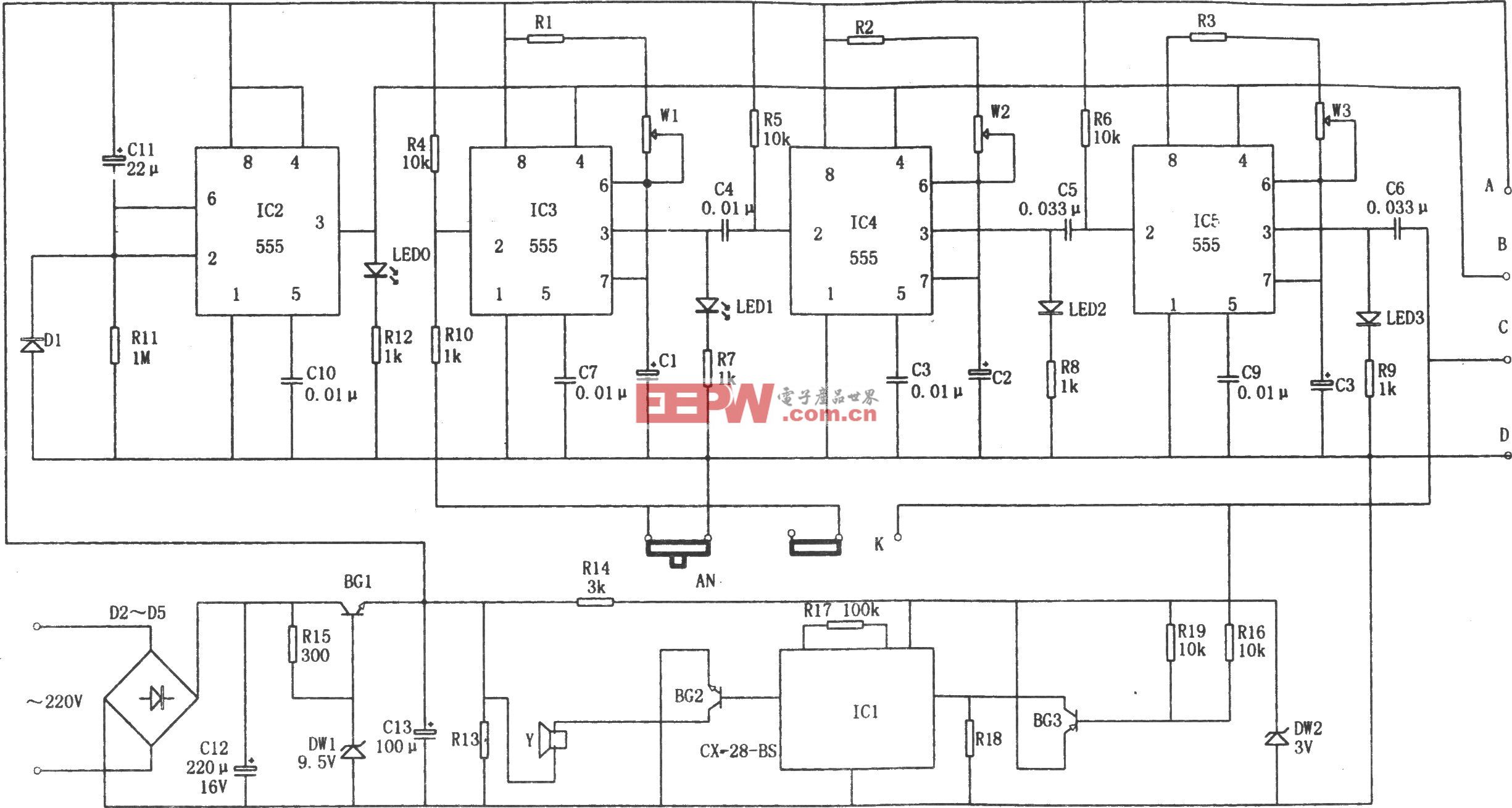

軟件仿真借助了第三方的仿真軟件Modelsim,在QuartusII當中利用Test Bench Template Writer建立仿真模板文件,并在模板當中給出激勵條件,編譯后即可生成用于仿真測試的vt文件了。初始化部分的仿真結果如圖3所示。

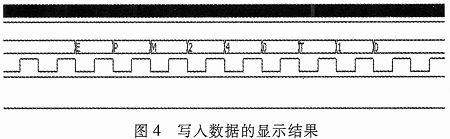

上圖信號從上到下依次為:clk,rst_n,lcd_dat,lcd_en,lcd_rs,lcd_rw。由圖3可知,由于系統時鐘頻率較高,clk已顯示為一條粗線,rst_n僅延時10個仿真單位,即被拉高為高電平,lcd_dat中出線一段藍色線條,占lcd_en的3個周期,即實現了15ms的延時,緊接著的四個周期連續寫入8’h38,然后8’h01等,直到8’h0c完成對LCD1602的初始化。圖4為初始化后向LCD1602寫入的數據,由于顯示內容的編碼與ASCII碼基本一致,可將其設置為ASCII進行觀察。

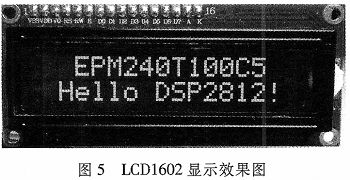

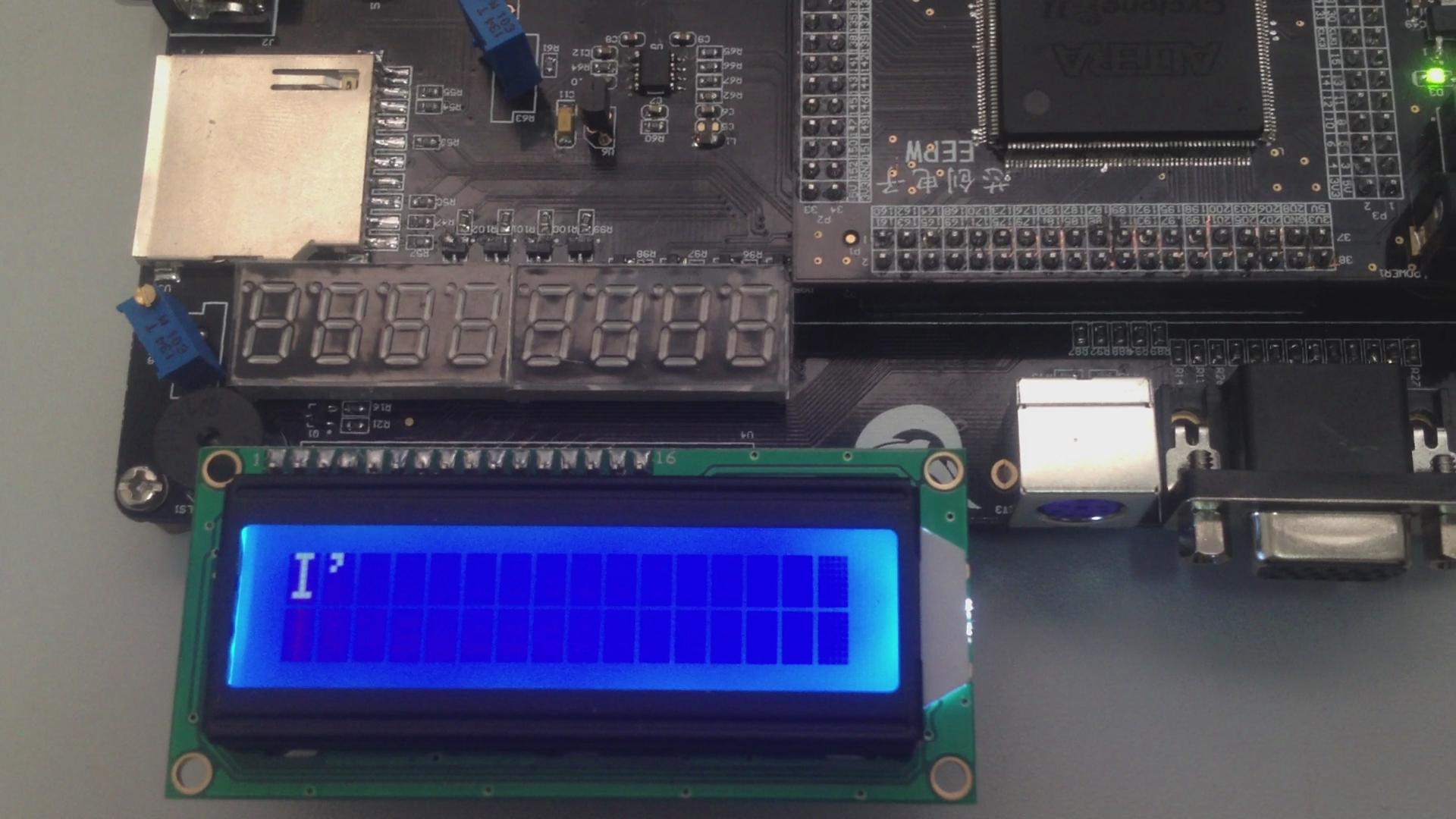

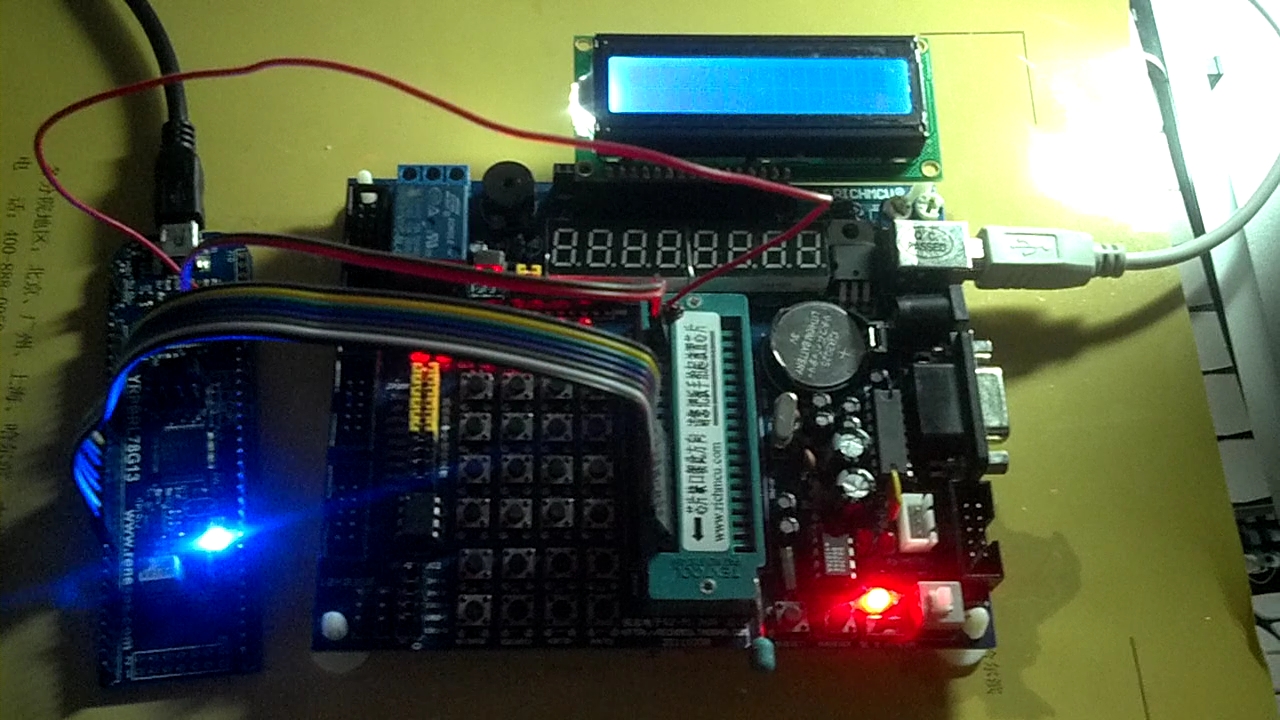

將Verilog HDL編寫的程序進行編譯,并將生的目標代碼下載至EPM240T100C5,最終顯示的效果如圖5所示。

5 結束語

通過對LCD1602時序進行詳細分析,本文實現了用CPLD驅動LCD1602顯示模塊工作的目的。通過仿真及硬件驗證,均說明了設計的合理性與正確性。另外,采用模塊化設計,也為后續系統的大規模化和可擴展性提供了很大方便。相比單片機實現過程,利用CPLD實現顯得更加簡單、方便。另外,CPLD管腳的可配置特點也為CPLD的使用帶來了極大的靈活性。隨著CPLD及FPGA技術的發展,數字系統設計也必將發展到一個新的階段。

評論