Verilog HDL基礎知識2之運算符

Verilog HDL 運算符介紹

本文引用地址:http://www.104case.com/article/202402/455478.htm算術運算符

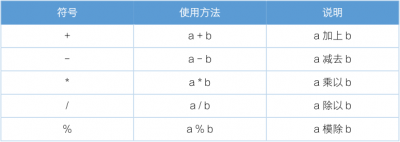

首先我們介紹的是算術運算符,所謂算術邏輯運算符就是我們常說的加、減、乘、除等,這類運算符的抽象層級較高,從數字邏輯電路實現上來看,它們都是基于與、或、非等基礎門邏輯組合實現的,如下。

例子:我們在生成時鐘的時候,必須需選擇合適的timescale和precision。當我們使用“PERIOD/2”計算延遲的時候,必須保證除法不會舍棄小數部分,所以實際上我們應該使用實數除法“PERIOD/2.0”。

parameter PERIOD=15;initial begin clk <= 0; forever #(PERIOD/2) clk = ~clk; end // Not correctinitial begin clk <= 0; forever #(PERIOD/2.0) clk = ~clk; end // Not correct

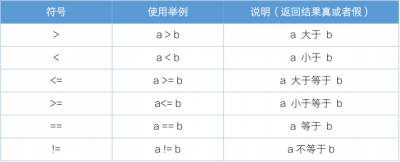

關系運算符

關系運算符主要是用來做一些條件判斷用的,在進行關系運算符時,如果聲明的關系是假的,則返回值是 0,如果聲明的關系是真的,則返回值是 1;所有的關系運算符有著相同的優先級別,關系運算符的優先級別低于算術運算符的優先級別。如下。

邏輯運算符

邏輯運算符是連接多個關系表達式用的,可實現更加復雜的判斷,一般不單獨使用,都需要配合具體語句來實現完整的意思,如下。

條件運算符

Verilog 語言為了讓連續賦值的功能更加完善,于是又從 C 語言中引入了條件操作符來構建從兩個輸入中選擇一個作為輸出的條件選擇結構,功能等同于 always 中的 if-else 語句,如下。

例子:使用?:。wire [15:0] bus = bus_enable ? drive ? bus_data : 16'bz; wire [7:0] data = (sel_a ? data_a : sel_b ? data_b : sel_c ? data_c : 8'bz);

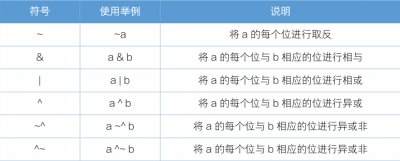

位運算符

位運算符是一類最基本的運算符,可以認為它們直接對應數字邏輯中的與、或、非門等邏輯門。

位運算符的與、或、非與邏輯運算符邏輯與、邏輯或、邏輯非,雖然它們處理的數據類型不一樣,但是從硬件實現角度上來說,它們沒有區別的,如下。

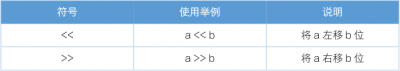

移動位運算符

在 Verilog 中有兩種移位運算符:左移位運算符和右移位運算符,這兩種移位運算符都用 0來填補移出的空位。如下。

例子:<<操作。 //In this example, the reg result is assigned the binary value 0100, // which is 0001 shifted to the left two positions and zero-filled.module shift; reg [3:0] start, result; initial begin start = 1; result = (start << 2); endendmodule

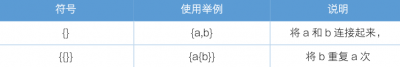

拼接位運算符

在 Verilog 中有一個特殊的運算符,就是我們的位拼接運算符。用這個運算符可以把兩個或多個信號的某些位拼接起來進行運算操作。如下。

例子:連接操作。

{a, b[3:0], w, 3'b101}

等價于

{a, b[3], b[2], b[1], b[0], w, 1'b1, 1'b0, 1'b1}例子:復制操作。

{4{w}} // This yields the same value as {w, w, w, w}。

{b, {3{a, b}}} // This yields the same value as {b, a, b, a, b, a, b}。運算符的優先級

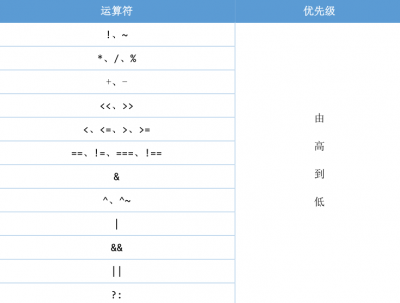

運算符一多,必然涉及到優先級的問題,為了便于大家查看這些運算符的優先級,我們將它們制作成了表格,如下。

評論