基于FPGA實現的PCI-I2S接口轉換電路

在設計PCI接口時,用戶通過發起寄存器讀寫請求tarO_req,去訪問后端寄存器,從寄存器交換數據,在CPU檢測到都算邏輯未使用寄存器時,可發起占用請求并占用寄存器(tarO_gnt被置位),此時,PCI讀寫此寄存器中的數據。

本文引用地址:http://www.104case.com/article/201609/303568.htm3 音頻接口設計

在驅動后端的音頻芯片時首先需要通過I2C接口配置音頻芯片的控制寄存器,此后根據音頻數據不同的采樣級別頻率控制FPGA產生的時鐘,最終音頻數據從FPGA內部的FIFO中通過FPGA產生的時鐘依據I2S協議標準向音頻芯片傳輸。在FPGA中設計的音頻接口包括I2C時序協議接口模塊,I2S時鐘控制接口模塊和I2S時序協議接口模塊。

3.1 I2C接口模塊的設計

I2C總線是由飛利浦公司開發的串行總線,總線由兩根信號線構成,其中SCLK為時鐘信號線,SDA為雙向數據線。I2C總線上的所有設備均可做為主設備,每個設備在總線上都有唯一的地址。

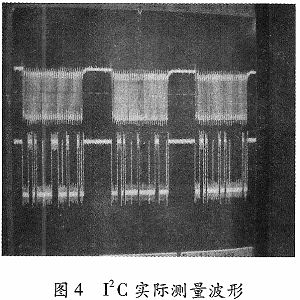

立體聲音頻編解碼器TLV320AIC23B中,共有11個寄存器需要配置,所有寄存器為只寫寄存器。這些寄存器分別控制芯片輸出音頻的左右耳機音量、左右功放音量、芯片電源、采樣率等參數。在芯片的配置參數傳輸時,以I2C的數據線(SDA)在時鐘線(SCLK)為高時下降沿條件作為數據的起始位,此后每當FPGA向TLV320AIC23B傳輸8位數據時,TLV320 AIC23B在第9個時鐘時通過SDA向FPGA返回一個ACK信號。如果FPGA確認收到ACK信號則繼續傳輸下一組數據,否則將重復傳輸此組數據。實際中示波器測量的傳輸波形如圖4所示。

3.2 I2S時鐘控制接口模塊的設計

由于不同的音頻數據有著不同的采樣級別頻率,所以在傳輸不同音頻文件時,FPGA提供給TLV320AIC23B的時鐘頻率不同,為使不同采樣頻率的聲音文件都能在本系統上正常播放,故在FPGA內部使用其DCM由主時鐘12.288 MHz生成16 kHz和32 kHz兩種采樣時鐘頻率,接入緩沖器BUFGMUX中,并且通過在PCI的配置空間中開辟一個寄存器,寄存器的值接至BUFGMUX的選擇端,這樣通過配置PCI總線配置此寄存器即可根據播放音頻的情況選擇時鐘頻率。

3.3 I2S時序協議接口模塊的設計

I2S時序接口模塊的主時鐘由FPGA內部提供,模塊內通過對主時鐘進行分頻產生BCLK與LRCin,模塊在每個LRCin的上升沿由緩存FIFO中讀取一個16 bit的數據放入臨時寄存器,此后在BCLK的每個上升沿依次由高至低讀取寄存器中的每一位并賦值給數據線SDIN,并且在LRCIN的下降延時重復傳輸此數據,從而完成音頻數據的I2S協議傳輸。

4 系統測試及結果

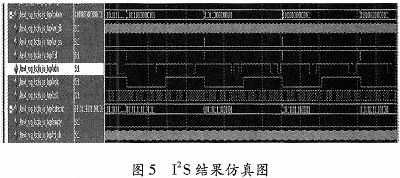

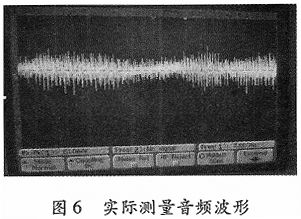

通過在上位機中向CPU內部Flash燒錄一段音頻數據,此后通過訪問FPGA的配置寄存器將此段數據傳入至FPGA內64 kB的FIFO中,后端音頻模塊檢測到FIFO非空即開始工作。首選通過邏輯仿真軟件對系統進行仿真,結果如圖5所示,信號線SDIN、 LRclk,BCLK輸出結果符合I2S協議規范中左對齊模式。此后可以在音頻芯片模擬輸出端接入耳機或功放等音頻播放設備,用示波器測量其模擬輸出。結果證明此系統工作正常,可以按照要求播放16 kbit·s-1與32kbit·s-1WAV音頻文件。通過示波器測量的模擬輸出如圖6所示,可以看出明顯的包絡信號。通過以上結論可以看出,系統可以充分利用FPGA片內資源,從而減少對板內面積占用并減低系統功耗,也易于移植入同類的嵌入式系統中。

在本文的基礎上,可以進一步發揮FPGA的靈活性,比如在開發FPGA上支持PCI從設備DMA模式,以進一步加強PCI總線的讀寫效率、I2S總線的右對齊和DSP模式等,并且可以開發語音芯片上的語音采集功能,使系統實現語音采集、轉換、傳輸等功能。

評論