基于FPGA實現的PCI-I2S接口轉換電路

摘要 提出了一種基于FPGA實現的PCI-I2S音頻系統方法。通過在FPGA中將PCI軟核、FIFO以及設計的接口電路等相結合,在FPGA上實現了 PCI、I2C、I2S等多種總線,并且結合音頻解碼器實現了不同采樣頻率語音數據的傳輸以及播放功能。系統充分利用FPGA的片上資源及其可編程特性,減少了硬件電路的復雜度。

本文引用地址:http://www.104case.com/article/201609/303568.htmI2S總線是一種用于音頻設備間傳輸數據的串行總線標準,該總線采用獨立的時鐘線與數據線,避免了時差誘發的失真。隨著多媒體的廣泛應用,該總線已被應用于越來越多的數字系統中。

PCI總線是一種高性能的32/64位局部總線,理論最大傳輸速率可達132 Mbit·s-1,可支持多組外設,已經被各類主流處理器做為總線標注,是目前應用最廣泛的外圍總線。如今大部分處理器并沒有集成I2S接口,但在嵌入式系統中CPU經常使用PCI總線與外圍設備進行交互,故需設計一種PCI—I2S接口轉換電路,從而實現CPU與外圍音頻設備進行通信。目前實現此種接口轉換電路主要通過PCI接口芯片與音頻接口芯片等專用集成電路芯片在板級電路進行組合從而實現基于PCI的音頻播放設備。此種電路雖然成熟可靠,但電路設計復雜、靈活性小而且需要占用大量的電路板空間。

隨著數字通信技術的發展,由于FPGA的靈活性與其較短的開發周期,在接口電路設計中的應用已經越來越廣泛。本文提出一種使用FPGA實現PIC—I2S 的接口轉換電路,不僅可以避免使用協議轉換芯片,節省電路板上的空間,而且還大幅加強了系統的靈活性,方便維護升級。

1 系統的硬件設計

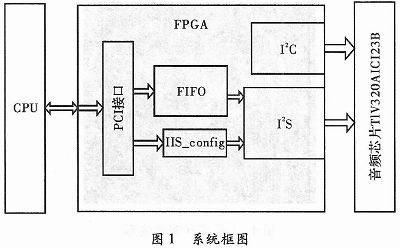

音頻播放系統主要由立體聲音頻編解碼器TLN320AIC23B,FPGA器件XC6SLX75以及處理器PowerPC8270組成。系統框圖如圖1所示,CPU將原始音頻數據通過PCI總線傳至FPGA后以每組數據16 bit的格式串行傳輸至音頻芯片TLV320AIC23B,并由音頻芯片將數字量轉換為模擬音頻信號輸出。FPGA實現PCI接口功能和對音頻編解碼芯片的配置與數據傳輸功能,其內部主要由PCI協議接口,I2S協議接口,I2S配置寄存器,I2C協議接口以及FIFO存儲器等組成。

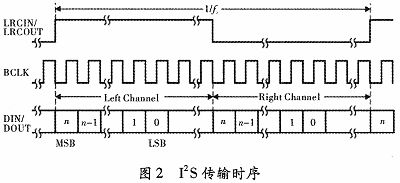

TLV320AIC23B在系統中實現數字音頻信息到音頻模擬量的轉換,在系統上電工作時,首先需要通過I2C接口配置它的多個控制寄存器,此后芯片將根據位傳輸時鐘(Bclk)與左右聲道控制時鐘(LRCIN),按控制寄存器中配置的方式采集由FPGA發送來的音頻數據。接收到的數據將傳至芯片內部進行數模轉換、濾波等處理。

FPGA根據I2S協議規范與芯片要求,由主時鐘(MCLK)分頻產生位傳輸時鐘(Bclk)與左右聲道控制時鐘(LRCIN),與音頻數據同步發送至 TLV320AIC23B。其中左右聲道控制時鐘(LRCIN)應與音頻數據的原始采樣級別頻率相同,根據I。S的協議規范及芯片資料,其位傳輸時鐘 (Bclk)與芯片的主時鐘(MCLK)如下

BCLK=Sampling Size×Sampling Rate (1)

MCLK=Sampling Size×Sampling Rate×384 (2)

式中,Sampling Rate為原始采樣級別頻率;SamplingSize為采樣大小。

系統中,TLV320AIC23B芯片采用左對齊的接口模式,其時序如圖2所示,其中LRCIN為高電平時音頻的左聲道選通,為低時音頻的右聲道選通。在 LRCIN的一個周期內,左右聲道上傳輸同一組數據。由于PCI總線的傳輸速度遠高于I2S總線的傳輸速度,為不使CPU過高頻率的響應中斷,所以在 FPGA中生成一個FIFO,可使得PCI總線可以連續傳入大量數據。此外,由于不同的音頻文件有著不同的采樣級別頻率,而通常音頻文件的采樣頻率為16 kHz或32 kHz,故在FPGA中生成I2S_config寄存器,可以通過PCI總線設置此寄存器以調用FPGA中不同的數字時鐘管理(DCM),從而為 TLV320AIC23B芯片提供不同的時鐘。

2 PCI接口設計

PCI協議比較復雜,它不僅有嚴格的同步時序要求,而且需要許多的配置寄存器,因此實現電路也比較復雜。通常情況下,在FPGA中實現PCI接口通常有3 種方式:(1)用FPGA自行設計PCI接口,該方法可根據需要有選擇地實現PCI接口功能,更貼近系統需要,而且可以降低系統成本,但需要開發者對 PCI協議有著深刻的了解,且在外部環境惡劣時,不容易滿足系統的穩定性要求,開發難度較大。(2)利用PCI硬核來對系統進行開發,PCI硬核即是嵌入在FPCA內部的固化電路,類似于專用的PCI接口芯片,設計者只需完成信號鏈接與驗證即可,但此方法中,PCI硬核已經固化在FPGA中,影響了系統的靈活性。(3)利用PCI軟核進行開發,PCI軟核可以根據用戶自身的需要進行配置,更為靈活,貼近用戶系統,且其已經過設計廠商的驗證,可靠性高。本文采用Mentor公司提供的開源軟核MPCI32用于FPGA上PCI接口的開發。

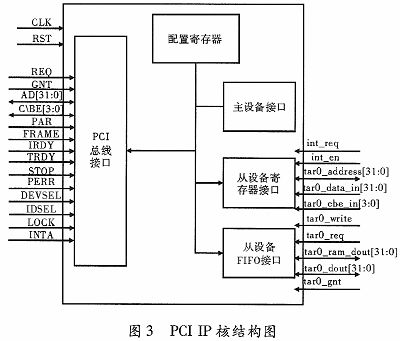

Mentor公司的PCI核完全符合PCI2.2的標準,支持33/66 MHz、32位數據的傳輸,PCI核的結構如圖3所示,該PCI核的功能是將入口測復雜的PCI接口信號轉為出口側較為操作的用戶信號。PCI核內用戶側設置有主控制接口和從控制接口以及配置寄存器等模塊,其中從控制接口分為寄存器接口與FIFO接口。因為本文中僅使用了從控制接口,所以圖中僅對從控制接口的信號展示。可以看出,IP核左側的信號為PCI的標準信號,在使用時與前端PCI總線連接,右側信號為本地數據信號,可以看出IP核將PCI上原本復用的地址線與數據線處理后分別接出為32位的地址線與32位數據線,并且原本總線上雙向的數據線被區分為單向讀信號線與寫信號線。此外還有后端邏輯對寄存器的讀寫地址信號線與PCI訪問邏輯的讀寫地址信號線,后端對寄存器使用時的請求信號線,寄存器被占用的標志信號線等。配置寄存器包含所有PCI配置空間的信息,其中包括表明設備信息的Device ID與Ven dor ID寄存器,以及命令寄存器,Base Address Register等主設備初始化時需要訪問的信息,這些信息在PCI核生成時已經被設定,無需改動。

評論