基于FPGA的IRIG-B碼解碼器設計

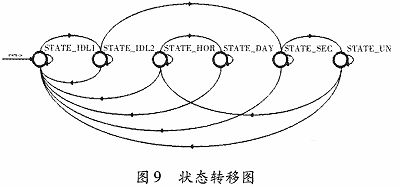

STATE_IDL1表示處于檢測碼元,當檢測出的碼元脈寬為8 ms后,將進入STATE_IDL2。進入狀態STATE_IDL2后,當第一個檢測出的碼元脈寬又是8 ms,則說明此刻檢測出的Pr碼元,即可以進入“秒”、“分”、“時”等后續檢測中;若第一個檢測出的碼元脈寬不是8 ms,則說明此刻不是幀的起始時間,轉入STATE_IDL1狀態,繼續檢測。當進入“秒 ”檢測狀態(STATE_SEC),即可依次提取個位和十位信息,為增強系統穩定性,如果發現STATE_SEC狀態中的第5個碼元不是索引碼元,狀態便轉入STATE_IDL1,否則繼續檢測“分”、“時”等信息。“分”、“時”、“天”信息的檢測過程與“秒”同理。

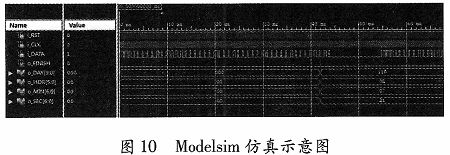

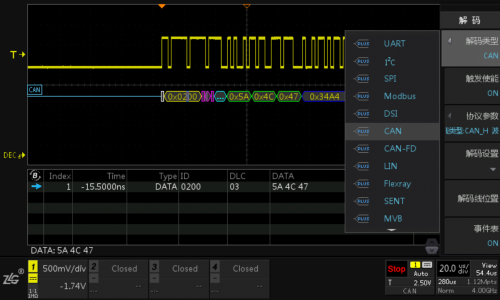

3 Modelsim驗證

根據B碼幀結構可知,“秒”、“分”、“時”和“天”信息的第41個,也就是“秒”起始后大約41 ms時刻。從圖10中可以清晰地看到大致在仿真時間4 1ms處出現o_FINI SH脈沖,o_FINISH作為解碼結束標志,即驗證了代碼的正確性。從圖10可知,解碼出的時間是110天8時7分21秒。

4 結束語

在FPGA系統中,毛刺是影響整個電子系統穩定性的重要因素。本文中采用的去毛刺方法較好地解決了IRIG—B碼解碼中存在毛刺的問題,從而提高了系統的穩定性。由于增加了解碼結束標志,本文的代碼移植性更強。經過Modelsim仿真驗證,該解碼器功能正確,具有較高的可靠性。

評論