某型機載作戰任務加載器的設計與實現

摘要:為了保證飛機作戰任務信息傳輸和傳遞的準確性和安全性,并考慮數據加載的方便快捷,文章提出了一種采用DSP實現安全可靠加載任務數據的解決方案。設計方案采用USB標準線性FLASH存儲卡作為任務數據加密存儲和傳遞載體,在飛機座艙操縱臺安裝一個集成USB存儲卡,集數據讀取解密和1553B總線數據加載等功能為一體的作戰任務加載器。文章從應用需求出發,對加載器的軟硬件設計與實現方法進行了較為詳盡的描述。此作戰任務加載器的應用豐富了任務數據的加載方式,減少了飛行員的操作,并能保證作戰任務數據的可靠傳輸。

本文引用地址:http://www.104case.com/article/201609/303565.htm引言

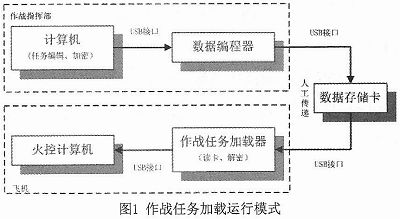

軍用飛機作戰任務具有較高的保密要求,飛行員需要從作戰指揮部獲取作戰任務數據,然后在飛機執行任務起飛前將作戰任務相關參數通過數據加載設備傳輸到火控計算機中。火控系統根據裝訂的信息參數引導飛行,在載機到達程序裝訂的目標區域時提醒飛行員做好戰斗準備,此外攻擊后的退出引導、返場引導等飛行過程都可根據裝訂的信息自動完成。作戰任務加載運行模式如圖1所示。

1 整體方案考慮

作戰任務加載器需要實現三個功能,包括讀取數據存儲卡的數據、數據解密和通過1553B接口向火控計算機發送數據。

數據存儲卡用于存儲和傳遞作戰導航數據,任務規劃系統對數據存儲卡執行編程操作,作戰任務加載器對數據存儲卡執行讀取操作。作戰任務加載器屬于小型機載嵌入式設備,其工作頻率較低,數據存儲卡應選擇工作模式相對簡單、讀取速度快、可靠性較高的產品。作戰任務加載器采用基于USB接口的NOR Flash存儲卡作為作戰導航參數信息的存儲載體。NOR Flash也稱為Linear Flash,擁有獨立的數據總線和地址總線,能快速隨機讀取,可以單字節/單字編程,但必須以塊為單位或整片執行擦除,重新編程之前必須進行擦除操作。 NOR Flash存儲卡簡單的訪問方式、快速讀取速度及較高的可靠性適合機載作戰任務加載器的工作環境和工作模式。

作戰任務編程/加載系統采用數據加解密技術保證移動存儲的安全保密性。所謂數據加密技術是指將信息(或稱明文)經過加密鑰匙及加密函數轉換,變成無意義的密文,而接收方將此密文經過解密函數、解密鑰匙還原成明文的技術。作戰導航參數信息需要任務規劃系統進行數據加密后存儲在數據存儲卡上,作戰任務加載器對數據存儲卡上的密文數據進行解密處理。作戰任務加載器固定安裝在飛機上,應用環境具有較高的安全性。考慮作戰任務加載器的實時性要求較低,且需要解密的導航信息數據量較小,加載器采用軟件解密方法即可滿足要求。雖然會帶來軟件運行開銷,但可降低硬件成本。

本系統采用IDEA(International Data Encryption Algorithm)加密算法實現作戰導航數據信息在數據生成端的加密和數據使用端的解密。IDEA被認為是目前世界上最好最安全的分組密碼算法,且對計算機功能要求不高。IDEA的密鑰長度是128位,相對較長,加密強度高。在窮舉攻擊的情況下,IDEA需要經過2128次加密才能恢復出密鑰,假設芯片每秒能檢測10億個密鑰,需要1013年,它被認為僅循環4次即可抵制差分密碼分析,對IDEA算法也不起作用,隨機選擇密鑰基本沒有危險,故其安全性較高;算法的基礎是16位運算,實現速度與DES相同。加密中從數碼鎖獲得的密鑰為128比特,明文分組長度是64比特。

采用DSP實現IDEA解密算法與硬件實現解密相比具有開發周期短、成本低的優點。另外DSP本身的流水線和運算器設計也能夠有效提高數據解密算法的運算速度。

2 硬件設計

作戰任務加載器由數據處理模塊、電源系統、機箱和數據存儲卡構成,機箱和電源采用一體化設計,數據處理模塊是作戰任務加載器內部唯一的SRU。數據存儲卡直接安裝在數據處理模塊上,可簡化整機結構設計。

2.1 DSP選型

數據處理模塊采用TI公司的數字信號處理器SM320F2812,集成1553B、USB、串口、離散量等數字接口。1553B接口用于向火控系統傳輸數據,USB接口用于訪問數據存儲卡,串口用于顯示維護BIT的測試結果,離散量用于控制作戰任務加載器進入不同的工作模式。SM320F2812的額定工作頻率為150MHz,每秒可執行1.5億次指令,具有單周期32bit ×32bit的乘和累加操作功能,主要實現USB存儲卡數據讀取、解密、發送的功能。

F2812的外部接口映射到5塊固定的存儲空間。每個存儲空間可以單獨設置訪問時的等待狀態數目、選通信號的建立時間和保持時序,且讀和寫操作的時序可以獨立設置。此外,每個空間可以分別選擇是否使用外部等待信號(XREADY)來擴展所需的等待狀態。這些片選信號以及可編程的等待狀態和選通時序使得 DSP芯片可以和許多外部存儲器或擴展外設間實現無縫接口。每個XINTF空間都有自己的時序寄存器XTIMING,改變時序寄存器的值將會影響相應空間的訪問時序。1553B接口、RAM、數據存儲卡可分別映射到不同的存儲空間,實現簡化設計。

2.2 1553B總線接口電路

作戰任務加載器與火控計算機之間的數據傳輸通過1553B總線接口實現。本設計選擇1553B接口芯片HK1553B來實現通信功能。

1553B總線接口電路工作時鐘為12MHz,經過隔離變壓器連接到1553B總線,模塊上1553B芯片工作在RT方式下,1553B協議芯片訪問外部存儲器為一片64k×16bitSRAM存儲器,存儲器的訪問控制及1553B協議芯片請求DSP總線及應答信號由FPGA產生。1553B協議芯片的地址和數據總線全部引入FPGA,1553B協議芯片訪問DSP總線時地址數據通過FPGA掛在EMIF總線上。

2.3 USB接口電路

本系統采用的存儲卡為MagicRAM公司的USBFlash存儲卡,該存儲卡讀取周期最大為200ns,可執行100000次寫/擦除操作。該存儲卡的讀寫訪問時序是典型的異步并行接口訪問時序。DSP提供了對異步存儲器的無縫訪問接口XINTF,將數據存儲卡單獨映射到DSP的 Zone2外部存儲空間。

USB芯片CY7C68013與FPGA相連,在檢測到USB供電后,通過FPGA實現對USB接口芯片的復位,并使能USB接口信號,實現與上位機的通信,完成調試加載功能。USB接口部分結構如圖2所示。

評論