Xilinx MIG IP核的研究及大容量數據緩沖區的實現

摘要:為了使DDR3 SDRAM更方便、多樣地用于工程開發中,本文對XILINX公司DDR3 SDRAM提供的MIG核進行了分析研究,并在此基礎上實現了大容量數據緩沖區的邏輯設計。通過對系統中各模塊的作用及相互間關系的研究,發現該控制器256位接口對工程開發十分不便,通過創建FIFO控制系統和讀寫接口FIFO的方式,將接口轉換為64位。該方案對控制核重新構建并上板測試,均符合高速數據傳輸緩存的要求,使DDR3成為一個大容量且可控的高速FIFO。

本文引用地址:http://www.104case.com/article/201607/294696.htm引言

隨著電子行業的飛速發展,人們對于設備處理速度的期望也越來越高。其中,DDR3的出現給整個行業帶來了不可限量的跨越,這使得我們在工程中對DDR3更加青睞。DDR3(double-data-rate three synchronous dynamic random access memory)是應用在計算機及電子產品領域的一種高帶寬并行數據存儲設備,廣泛應用于工程設計中。

Xilinx公司為DDR3提供了IP核和方便友好的用戶接口,推進了DDR3在FPGA中的使用進程。尤其對于高速數據的傳輸和處理,FPGA內FIFO遠不能滿足性能上的要求。這就使得將DDR3設計成大容量數據緩沖區成為工程中的必要需求。然而由于需求的不同,對核接口的要求也會隨之改變。Xilinx官方核的接口是256位,但實際需求中64位的居多,本文將從邏輯上對該核進行重建。

1 MIG核的分析及重構

1.1 MIG核的結構

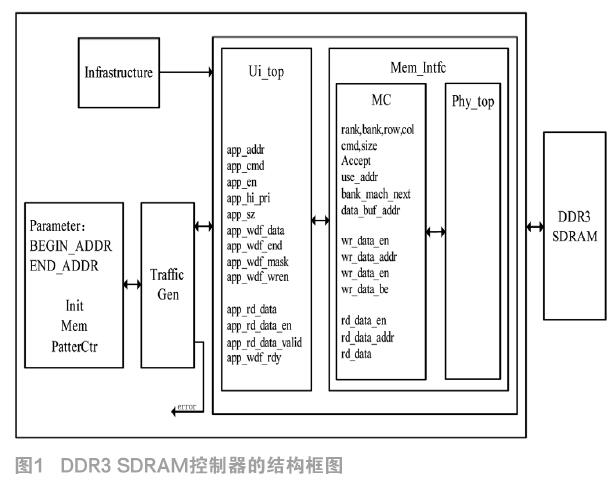

DDR3 SDRAM控制器的主要功能是實現對DDR3 SDRAM存儲器的初始化。此外,DDR3 SDRAM控制器還可以將DDR3 SDRAM接口的上下時鐘沿數據轉變成單時鐘沿用戶數據,同時還可以產生周期性的刷新指令,完成對DDR3 SDRAM存儲器的動態刷新,從而保證數據的完整性。DDR3 SDRAM控制器的結構框圖如圖1所示,其主要包括四個部分,分別是基礎模塊(infrastructure)、用戶界接口模塊(user interface)、物理層模塊(physical layer)和存儲器控制模塊(memory controller)。

基礎模塊首先接收通過FPGA全局時鐘網絡的外部200MHz差分時鐘,然后通過混合模式,時鐘管理器(MMCM)產生用戶接口時鐘、控制模塊使用的時鐘以及DDR3存儲器的時鐘。除此之外,該模塊還生成了一個可以全局復位整個DDR3 SDRAM控制器IP核的復位信號。該模塊還包括一個延時控制單元,用來同步校準設計中的延時單元,以減少功耗。

用戶接口模塊的主要功能是連續地輸入或輸出數據和控制命令,完成對用戶數據、控制命令以及地址等信息的接收和緩存,從而實現對數據的緩沖和同步效果。

物理層模塊通過物理引腳與片外DDR3 SDRAM直接進行數據通信,它可以對片外DDR3 SDRAM存儲器發出的數據進行捕獲,同時產生片外DDR3 SDRAM存儲器所需要的控制信號,通過緩存把數據、命令以及地址等信號發送給片外DDR3 SDRAM,從而保證了數據信號、命令信號與地址信號的同步。

控制模塊的主要功能是實現對DDR3 SDRAM存儲器的初始化操作。DDR3 SDRAM上電之后,首先經過200μs的穩定期,然后等到500μs后,把時鐘使能信號CKE拉高,保持至少10ns,然后開始ODT過程,對擴展模式寄存器和模式寄存器進行配置,使能DLL并對DLL復位。如果信號phy_initial_done拉高,那么表示DDR3存儲器初始化完成,校準結束。初始化結束后,DDR3控制器根據DDR3 SDRAM存儲器的用戶讀寫操作時序要求,自動生成所需命令以及控制信號,發送給DDR3 SDRAM存儲器。當發送完命令信號之后,給用戶發送一個命令應答信號,設計人員可以根據這個命令應答信號判斷是否可以發送下一條指令。整個過程中,DDR3控制器自動完成自刷新、激活以及預充電等命令的發送和相應操作的執行,這個過程完全不需要用戶干涉DDR3 SDRAM存儲器。

1.2 大容量DDR3緩存設計

在本系統設計中,DDR3 SDRAM的主要功能是用于大容量數據緩存,考慮到FPGA不僅處理速度高,而且靈活性和可配置性好,故使用Xilinx公司FPGA提供的DDR3 SDRAM緩存控制器IP核可以輕松實現FPGA與外部存儲器之間的接口設計。根據FIFO的基本原理,采用Xilinx公司的FPGA和Micron公司容量為1GB的DDR3內存MT4JSF12864HZ設計實現了一種大容量虛擬FIFO緩存。

該大容量虛擬FIFO緩存設計主要由上行FIFO、FIFO控制器、寫接口FIFO、讀接口DDR3 SDRAM控制器、時鐘模塊以及外部的DDR3 SDRAM存儲器六部分構成。其整體結構框圖如圖2所示。DDR3 SDRAM緩存接口的設計主要集中在FPGA內部邏輯設計,具體的設計主要包括DDR3控制器設計、讀寫FIFO接口設計、FIFO控制器設計以及時鐘模塊設計。

1.2.1 接口FIFO設計

在該設計中,寫FIFO接口和讀FIFO接口主要完成數據位寬的轉換以及數據的跨時鐘域處理;FIFO控制器主要完成對寫FIFO接口和讀FIFO的控制,按照DDR3控制器用戶接口時序對用戶接口進行讀寫操作;DDR3 SDRAM控制器則主要完成對DDR3 SDRAM的初始化,將復雜的讀寫時序轉化為簡單的用戶讀寫時序。

寫FIFO接口和讀FIFO接口主要功能是實現FPGA與DDR3 SDRAM之間的數據傳輸。由于FPGA與DDR3 SDRAM分別屬于不同的時鐘域,故在設計中需要采用兩個異步FIFO處理數據跨時鐘域傳輸的問題。此外,由于PCI Express總線接口的數據位寬為64位,而DDR3 SDRAM控制器提供的用戶接口數據位寬為256位,因此,還需要通過這兩個FIFO完成數據位寬的轉換。

當信號從一個時鐘域傳遞到另外一個時鐘域時,使用異步FIFO可以解決傳輸過程中出現的亞穩態問題。在ISE 14.2開發平臺下設計FIFO的方法有兩種,一種是設計者自己設計FIFO的控制邏輯,然后通過CORE Generator生成DPRAM,最后將兩者連接起來構成一個FIFO;另一種是利用CORE Generator工具自動生成一個FIFO的IP核,然后在設計中實例化即可使用。第一種方法比較費時,而且有一定的難度,相對而言,第二種方法就簡單很多,設計者可以不用關心FIFO實現的細節,而專注于其頂層的功能和應用。本設計直接調用Xilinx公司FPGA內部IP核對FIFO進行設計。

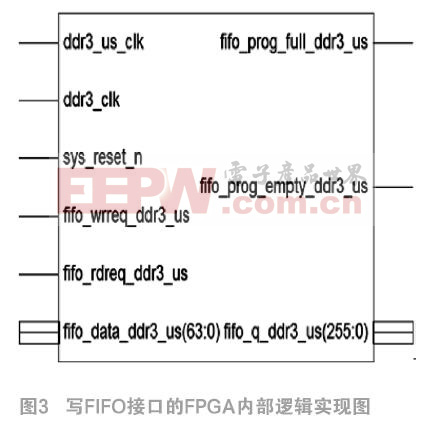

寫FIFO接口包含一個異步FIFO和一個同步FIFO,異步FIFO寫入數據位寬是64位,讀出數據位寬是256位,其寫時鐘為250MHz的PCI-E系統時鐘,讀時鐘為200MHz的DDR3用戶接口時鐘;同步FIFO寫入和讀出數據位寬均為256位,其讀寫時鐘為200MHz的DDR3用戶接口時鐘。寫FIFO接口通過兩個FIFO進行級聯的方式加深其處理數據的深度。寫FIFO接口的FPGA內部邏輯實現如圖3所示。

讀FIFO接口則只包含一個異步FIFO,其寫入數據位寬是256位,讀出數據位寬是64位,寫時鐘為200MHz的DDR3用戶接口時鐘,讀時鐘為250MHz的PCI-E系統時鐘。讀FIFO接口的FPGA內部邏輯實現如圖4所示。

1.2.2 FIFO控制器

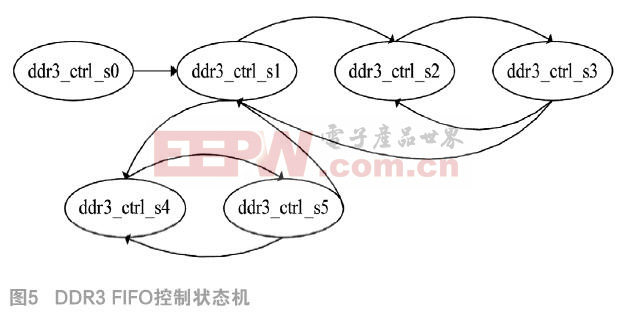

FIFO控制器的主要功能是實現對寫FIFO接口、讀FIFO接口與DDR3 SDRAM之間數據交互的控制。由于DDR3 SDRAM內存工作時鐘頻率為400MHz,此時其理論傳輸帶寬為51.2Gbps,遠遠高于讀FIFO接口和寫FIFO接口的數據傳輸帶寬,故FIFO控制器需要根據讀寫FIFO所緩存的數據量,對DDR3 SDRAM總線進行分時復用。DDR3讀寫控制狀態機設計如圖5所示。下面就將對各狀態含義與跳轉條件做簡要說明:

ddr3_ctrl_s0:復位或異常情況下,默認等待狀態。當DDR3控制器完成初始化后,即phy_init_done有效時,跳轉到ddr3_ctrl _s1狀態。

ddr3_ctrl _s1:當DDR3內存不滿且DDR3寫接口的FIFO非空時,如果命令地址FIFO準備好接收命令且寫數據FIFO準備好接收數據,則跳轉到ddr3_ctrl _s2狀態,同時將app_wdf_wren置為有效,將DDR3寫FIFO接口的讀使能置為有效;當DDR3內存不空且DDR3讀接口FIFO不滿時,如果命令地址FIFO準備好接收命令,則跳轉到ddr3_ctrl _s4狀態;其他情況狀態不跳轉。

ddr3_ctrl _s2:當寫入數據FIFO準備好接收數據時,跳轉到ddr3_ctrl _s3狀態,同時將app_wdf_end置為有效,指示當前是最后一個有效數據,在給出寫命令和地址的同時將使能置為有效;其他情況狀態不跳轉。

ddr3_ctrl _s3:當命令地址FIFO準備好接收命令且寫數據FIFO準備好接收數據時,如果寫入次數等于32,此時剛好寫滿一行,則跳轉到ddr3_ctrl _s1狀態,同時將app_en、app_wdf_wren和DDR3寫FIFO接口的讀使能置為無效;如果寫入次數小于32,即沒有寫滿一行數據,則跳轉到ddr3_ctrl_s2狀態,同時將app_wdf_wren和DDR3上行FIFO讀使能置為有效。當命令地址FIFO沒有準備好接收命令但寫數據FIFO準備好接收數據時,將app_wdf_wren和DDR3寫FIFO接口的讀使能置為無效,同時將app_wdf_end置為無效,狀態不跳轉。

ddr3_ctrl _s4:狀態跳轉到ddr3_ctrl _s5,在給出讀命令和地址的同時將使能置為有效。

ddr3_ctrl _s5:當命令地址FIFO準備好接收命令,如果讀出次數等于32,此時剛好讀完一行數據,狀態跳轉到ddr3_ctrl _s1;如果讀出次數小于32,即沒有讀完一行數據,則跳轉到ddr3_ctrl_s4狀態;其他情況時將app_en置為無效,狀態不跳轉。

1.2.3 時鐘模塊設計

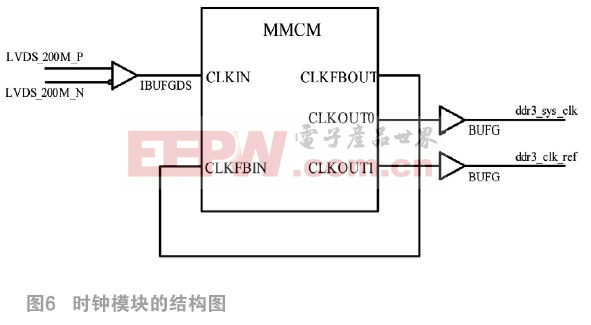

在本系統的時鐘模塊設計中,時鐘模塊的具體結構如圖6所示。它包括一個IBUFGDS(差分信號輸入緩沖)、一個MMCM(混合模式時鐘管理器)和兩個BUFG(全局時鐘輸出緩沖)。在進行設計的時候,需要用戶提供給DDR3 SDRAM控制器兩個時鐘,這兩個時鐘分別是DDR3 SDRAM存儲器工作的系統時鐘(ddr3_sys_clk)和時延單元的參考時鐘(ddr3_clk_ref)。由于DDR3 SDRAM要滿足系統的傳輸帶寬要求,設計的時候需要其工作時鐘頻率為400MHz,因此,DDR3控制器上以工作時鐘頻率運行的系統時鐘頻率為400MHz,提供給時延單元的參考時鐘頻率為200MHz。

考慮到系統提供的是來自全局時鐘網絡的200MHz差分時鐘,但是在DRR3控制器定制的時候,在MIG設置界面選擇的時鐘輸入形式是單端輸入,因此,首先需要將輸入的全局差分時鐘連接到IBUFGDS(差分信號輸入緩沖)上,然后再通過一個MMCM倍頻出DDR3 SDRAM控制器所需要的兩個時鐘。該時鐘模塊的FPGA內部邏輯實現如圖7所示。

2 運行和測試

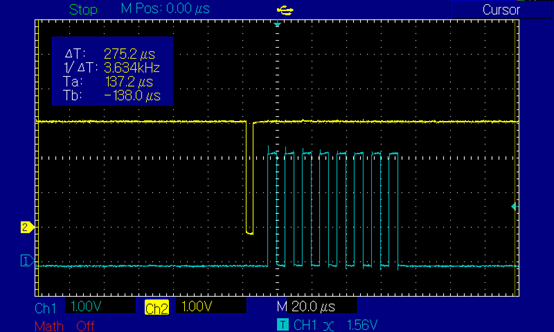

本文測試所選芯片為XILINX V6系列FPGA,所選環境為ISE14.6。在該環境中創建支持DDR3的IP核,根據設計目的對核進行修改。將程序燒寫至FPGA后,可通過邏輯分析儀ChipScope來抓取內部想要觀察的信號。下圖是實時抓取的FIFO數據。

其中fifo_q_ddr3_us是256位的核接口信號,fifo_data_ddr3_us和fifo_data_q_ds分別為改造后的對外接口,均為64位。由上述所抓取的fifo_data_ddr3_us的數據可以看到,數據最先到達該fifo,然后經過緩存進入256位fifo_q_ddr3_us,最后存入DDR3。讀出數據是從fifo_data_q_ds輸出。測試數據是遞增的,由上述信號可以看到,該改造達到了預期目的。

3 結束語

本文通過基于FPGA DDR3 SDRANM IP核的邏輯重構,將256位寬的接口改造為64位接口,使得工程上數據接口更為通用。為后期工程開發提供便捷可控的接口。隨著電子行業的飛速發展,對高速大容量緩存的需求也隨之增大。怎樣利用當前的快速緩存技術于自己的設計中成為開發中的一個門檻。本文正是結合實際需求給出了這一答案。

參考文獻:

[1]Virtex-6 FPGA Memory Interface Solutions (UG406). Xilinx Corporation,2010.

[2]夏玉立, 雷宏, 黃瑤.用Xilinx FPGA實現DDR SDRAM控制器[J].微計算機信息. 2007(26).

[3]陳雨, 陳科, 安濤.高速圖像處理系統中DDR2-SDRAM接口的設計[J].現代電子技術. 2011,34(12).

[4]任穎, 黃建國.基于FPGA的DDR2 SDRAM控制器接口的簡化設計方法及實現[J].電子質量.2008(11):31-33.

[5]Xilinx. Virtex-6 FPGA user guide[R]. USA: Xilinx,2008.

[6]庾志衡, 葉俊明, 鄧迪文.基于FPGA與DDR2 SDRAM的大容量異步FIFO緩存設計[J].微型機與應用.2011,30(6).

本文來源于中國科技期刊《電子產品世界》2016年第7期第43頁,歡迎您寫論文時引用,并注明出處。

評論