Vivado IPI 為 Aurora 設計開放 FPGA 共享資源

3X4 信道設計

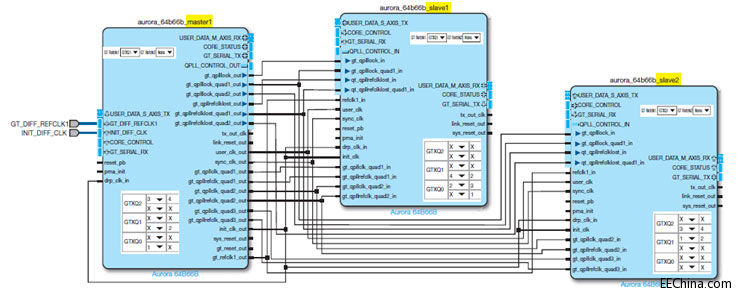

本文引用地址:http://www.104case.com/article/201601/286363.htm假設需要 3 個四信道設計,如果沒有共享邏輯特性,您可能要創建 3 個主機模式的四信道 Aurora 內核,然后對生成的設計進行手動處理,以獲得最佳的時鐘資源利用率。如果您能直接實現同樣的結果呢?您可按圖 3 所示對一個主機內核和兩個從機內核進行定制,以實現此目的。

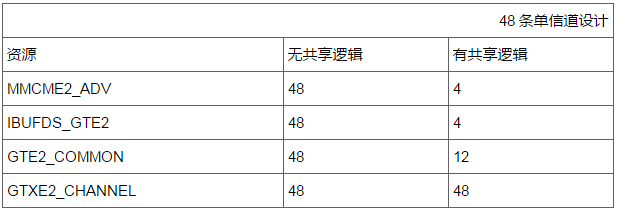

而更大尺寸(16 個或以上)的單信道 Aurora 設計就更加需要共享邏輯。有時候甚至需要 48 個單信道獨立雙工鏈路。允許的 Aurora單信道鏈路數量僅受所選器件的可用 GT 資源數量限制。在這種情況下,如果不有效利用共享邏輯特性,很難實現這類系統設計。

該設計覆蓋 12 個 Guad,因此需要 2*12 個差分時鐘資源,從電路板設計角度看,這實在是項令人生畏的艱巨任務。您可利用“12 條單信道設計”案例中所提到的技術方法,減少整個系統的差分時鐘和 MMCM 需求(參見表 5)。

非對稱信道和其它定制優化

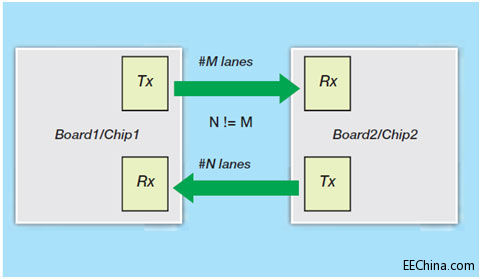

在視頻投影機這樣的設備中,主流數據以高吞吐量單方向流動,而吞吐量較低的反向通道則用來傳輸輔助或控制信息。在此類應用設備中,采用全面的雙工鏈路意味著使用更少的帶寬,本質上會降低系統設計的投資回報率。這種問題的理想解決方案是:如圖 4 所示,采用非對稱的鏈路寬度以及最優的 GT 資源利用率,其中,具有較高吞吐量的數據流方向上的信道數量要多于具有較低吞吐量的數據流方向上的信道數量。

圖 3–面向 3 個連續 Guad 上四信道 Aurora 設計的“1 個主機和 2 個從機”配置

由于 Aurora 內核中現有的數據流模式(單工/雙工),目前只能以相同的 TX 和 RX 信道數量來配置內核。要想使兩個方向的信道數量不同,您需要為每個方向生成兩個 Aurora 單工內核。賽靈思應用指南 1227,“采用 Aurora 64B/66B IP 核的非對稱信道設計” (XAPP1227) 中介紹了在 7 系列 FPGA 上構建非對稱信道設計的方法。

另外一個有用的設計策略是 BUFG 資源優化。通常,為了實現在相同或不同線路速率下工作的多個 Aurora 內核,系統設計人員需要知道器件具體的時鐘要求和限制。要想實現很多條 Aurora 鏈路,就需要為每條鏈路生成時鐘。節約時鐘資源會提高系統的性價比。如果系統設計具有多個模塊,而且時鐘資源 (BUFG) 緊張,那么應考慮用 BUFR/BUFH 代替 BUFG。建議您使用相同類型的緩沖器驅動 GT 內核的兩個 TX 路徑用戶時鐘。

表 4–3 個四信道設計的最優信道選擇

圖 4–用 Aurora 實現跨鏈路的非對稱數據傳輸

7 系列 Aurora 內核需要一個額外的動態重配置端口 (DRP) 時鐘輸入,否則將需要使用一個 BUFG。如果 Aurora 的自由運行時鐘頻率選定在允許的 DRP 時鐘范圍內,那么 Aurora 輸出的自由運行時鐘可以重復使用并連接回到 DRP 時鐘。這樣您可節省所生成設計中的 BUFG 數量。

在為多個 Aurora 設計選擇線路速率時,您應記住:

如果線路速率是整數倍數,便于時鐘推導和在多條鏈路之間共享,這樣您就可共享時鐘資源。如果將共享邏輯特性延伸到諧波線路速率,您就可以通過少量的額外時鐘分頻器為從機 Aurora 內核生成所需的輸入頻率。

未來機遇

Aurora 具有很高的靈活性,可用來創建多種系統配置和應用。在賽靈思 Vivado IP Integrator 這樣的強大工具幫助下,較高的設計輸入生產力和系統級資源共享正在加速 All Programmable 應用領域的創新。憑借賽靈思 UltraScale 架構,具備更多 GT 通道的器件可受益于更強的 GT 線路速率支持,因此能夠實現更多的設計可能性和更高的資源利用率。

表 5–在 48 條單信道設計中使用共享邏輯特性所實現的資源優勢

如需評估 Aurora 內核,敬請查看IP Catalog、IPI 和 Aurora 產品 Web 頁面:http://china.xilinx.com/products/design_resources/conn_ central/grouping/aurora.htm.

評論