讓XDC時序與約束為您效力

作者:Adam Taylor e2v 公司首席工程師 aptaylor@theiet.org

本文引用地址:http://www.104case.com/article/201601/286360.htm時序和布局約束是實現設計要求的關鍵因素。本文是介紹其使用方法的入門讀物。

完成 RTL 設計只是 FPGA 設計量產準備工作中的一部分。接下來的挑戰是確保設計滿足芯片內的時序和性能要求。為此,您經常需要定義時序和布局約束。我們了解一下在基于賽靈思 FPGA 和 SoC 設計系統時如何創建和使用這兩種約束。

時序約束

最基本的時序約束定義了系統時鐘的工作頻率。然而,更高級的約束能建立時鐘路徑之間的關系。工程師利用這類約束確定是否有必要對路徑進行分析,或者在時鐘路徑之間不存在有效的時序關系時忽視路徑。

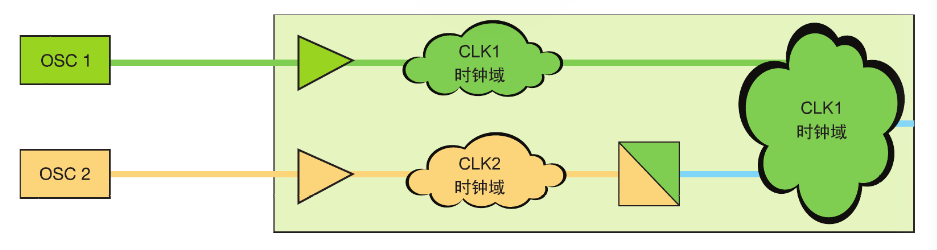

默認情況下,賽靈思的 Vivado® 設計套件會分析所有關系。然而,并非設計中的所有時鐘之間都有可以準確分析的時序關系。例如當時鐘是異步的,就無法準確確定它們的相位,如圖 1 所示。

圖 1–時鐘域 CLK1 和 CLK2 相互之間異步。

您可通過在約束文件中聲明時鐘組來管理時鐘路徑之間的關系。當聲明時鐘組時,Vivado 工具不會對組內定義的時鐘之間的任何方向執行時序分析。

為了有助于生成時序約束,Vivado 工具將時鐘定義為三種類型:同步、異步或不可擴展。

• 同步時鐘具有可預測的時序/相位關系。通常主時鐘及其衍生時鐘符合這種特性,因為它們具有公共的根起源和周期。

• 異步時鐘之間不具備可預測的時序/相位關系。通常不同的主時鐘(及其衍生時鐘)符合這種特性。異步時鐘有不同的起源。

• 如果超過1,000個周期后,仍無法確定公共周期,那么兩個時鐘就是不可擴展的。如果是這種情況,將使用 1,000 個周期內的最差建立時間關系。不過,無法保證這就是實際的最差情況。

使用 Vivado 生成的時鐘報告來確定您所處理的時鐘是哪種類型。該報告可幫助您識別異步和不可擴展時鐘。

聲明多周期路徑能實現更合適而且要求放松的時序分析,從而讓時序引擎集中處理其它更關鍵的路徑。

識別出這些時鐘后,您就可利用“set clock group”約束禁止它們之間的時序分析。Vivado 套件使用的是賽靈思設計約束 (XDC),其基于廣泛使用的 Tcl 約束格式的 Synopsys 設計約束 (SDC)。通過 XDC 約束,您可使用以下命令定義時鐘組:

set_clock_groups -name -logically_exclusive -physically_exclusive -asynchronous -group

-name 是為組賦予的名稱。-group 選項是定義組成員(即沒有時序關系的時鐘)的位置。當有多個用來驅動時鐘樹的時鐘源可供選擇,包括 BUFGMUX 和 BUFGCTL,應使用 logically 和 physically exclusive 選項。從而,這些時鐘不能同時出現在時鐘樹上。所以,我們不希望 Vivado 分析這些時鐘之間的關系,因為它們是互斥的。最后,–asynchronous 約束可用來定義異步時鐘路徑。

建立時序關系的最后一個方面是考慮時鐘的非理想關系,尤其是抖動。您需要考慮兩種形式的抖動:輸入抖動和系統抖動。輸入抖動出現在主時鐘輸入上,體現了實際跳變出現時間與理想條件下跳變出現時間之間的差異。系統抖動源自設計中存在的噪聲。

您可以使用 set_input_jitter 約束來定義每個主輸入時鐘的抖動。同時,使用 set_system_jitter 約束為整個設計(所有時鐘)設定系統抖動。

時序例外

當有時序例外時,您還必須關注已定義的時鐘組內發生了什么。然而,什么是時序例外呢?

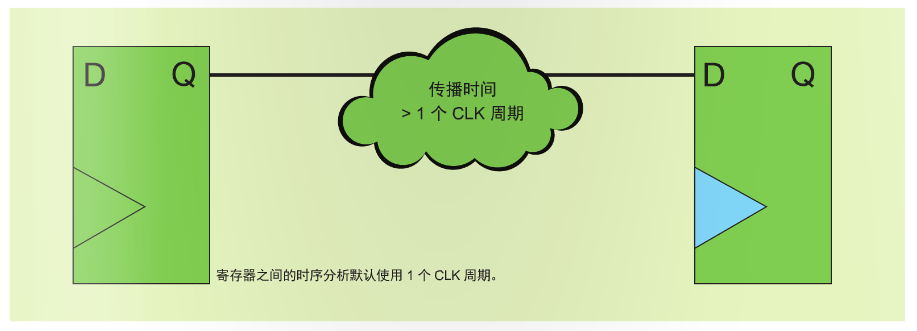

一種常見的時序例外是只有每隔一個時鐘周期所采樣的結果。另一種情況是將數據從慢時鐘傳輸到更快的時鐘(或相反),其中兩個時鐘都是同步的。事實上,這兩種時序例外一般被稱為多周期路徑,如圖 2 所示。

圖 2–多周期路徑是一種時序例外的例子。

為這些路徑聲明多周期路徑能實現更合適而且要求放松的時序分析,從而讓時序引擎集中處理其它更關鍵的路徑。最后的益處是能夠提高結果質量。

您可以在 XDC 文件中使用以下 XDC 命令聲明多周期路徑:

set_multicycle_path path_ multiplier [-setup|-hold]

[-start|-end][-from ] [-to ]

[-through

]

當您聲明多周期路徑時,實際上是將建立或保持(或二者皆有)分析要求與 path_mutiplier 相乘。例如在上面的第一個實例中,每兩個時鐘周期有一次輸出,因此對于建立時序而言 path_multiplier 是 2。由于多周期路徑既可應用到建立時間又可應用到保持時間,那么您可以選擇其應用位置。當您聲明建立時間乘數時,最佳做法通常是使用下面的公式同時聲明一個保持時間乘數。

保持周期 = 建立乘數 – 1 – 保持乘數

這對于我們所介紹的下列簡單實例意味著,保持乘數由下面這個公式確定:

保持乘數 = 建立乘數 – 1,當使用公共時鐘時。

為了演示

多周期路徑的重要性,我創建了一個簡單實例,您可在這里下載。在 XDC 文件中有一個實例包含了建立和保持這兩個已被同時聲明的多周期路徑。

物理約束

最常用的物理約束是 I/O 引腳布局和與 I/O 引腳有關的參數定義,例如標準驅動強度。不過,還有其它類型的物理約束,包括布局、布線、I/O 和配置約束等。布局約束能夠定義單元的位置,而布線約束可用來定義信號的布線。I/O 約束可用來定義 I/O 位置及其參數。最后,配置約束可用來定義配置方法。

同樣,也有一些約束不屬于這幾組約束。Vivado 設計套件包含三種這樣的約束,它們主要用于網表中。

• DONT_TOUCH – 該約束可用來阻止優化,這樣當實現安全關鍵型或高可靠性系統時該約束會非常有用。

• MARK_DEBUG – 該約束可用來保存 RTL信號,以便隨后用于調試。

• CLOCK_DEDICATED_ROUTE – 該約束可用來識別時鐘布線。

最常用的約束與 I/O 布局和 I/O 的配置有關。將 I/O 放在 FPGA 上,需要使用布局約束找到物理引腳,使用 I/O 約束配置 I/O 標準和斜率等 I/O 屬性。

現代化的 FPGA 支持多種單端和差分 I/O 標準。這些均可通過 I/O 約束來進行定義。不過,您必須確保遵守 I/O Banking 規則,這取決于最后的引腳布局。

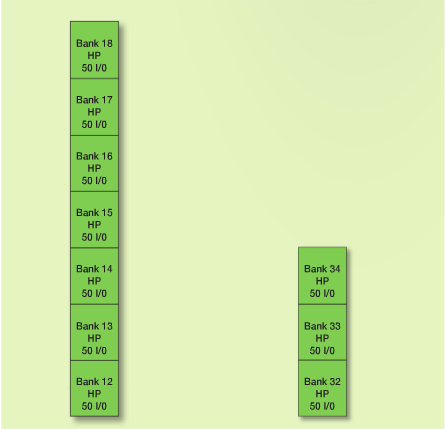

但什么是 I/O Banking 規則?將 FPGA 中的用戶 I/O 分組為若干個 Bank,每個 Bank 包含多組 I/O。這些 Bank 具有獨立的電壓源,能支持多種 I/O 標準。在 Zynq®-7000 All Programmable SoC(以及其它 7 系列器件)中,I/O Bank 被進一步分為高性能和大范圍這兩個大的組別。這種類別劃分能進一步約束性能,并要求工程師針對接口使用正確的類別。

高性能 (HP) 類別針對更高的數據速率進行了精心優化。它使用更低的工作電壓,而且不支持 LVCMOS 3v3 和 2v5。另一個是大范圍 (HR) 類別,其可處理 HP 不支持的更多 I/O 標準。因此,HR 支持傳統的 3v3 和 2v5 接口。圖 3 給出了這些 Bank。

圖 3 – 賽靈思 7 系列器件上的高性能(左)和大范圍 I/O Bank

當您決定為信號使用哪種 Bank 后,仍然可以更改信號驅動強度和斜率。這些都是硬件設計團隊很感興趣的指標,因為他們要努力確保單板的信號完整性達到最優。選擇結果還會影響單板設計的時序。為此,您可以使用信號完整性工具。

SI 工具需要 IBIS 模型。當您打開了Impelmented Design時,您可使用 File->Export->Export IBIS 模型選項從 Vivado 工具中提取設計的 IBIS 模型。然后,使用該文件關閉解決系統級 SI 問題和最終 PCB 布局的時序分析。

如果設計團隊整體上對 SI 性能以及系統的時序感到滿意,您就會得到針對設計中 I/O 的多個約束,如下所示。

set_property PACKAGE_PIN G17 [get_ports {dout}] set_property IOSTAN- DARD LVCMOS33 [get_ports

{dout}]

set_property SLEW SLOW [get_ports {dout}]

set_property DRIVE 4 [get_ ports {dout}]

對于 HP I/O Bank,您還可使用數控阻抗正確做IO端接并增加系統的 SI,無需使用外部端接方案。如果沒有信號驅動 I/O,例如將 I/O 連接到外部連接器,這時您還必須考慮 I/O 的影響。這種情況下,您可使用 I/O 約束實現上拉或下拉電阻,以防止由于 FPGA 輸入信號懸置而導致系統問題。

當然,您也可以使用物理約束在 I/O block 內放置最終的輸出觸發器,以改善設計的時序。這樣做能縮短clock to out的時間。您也可以對輸入信號做相同的處理,以使設計滿足引腳到引腳的建立和保持時間要求。

物理約束從布局開始

您可能出于多種原因想對布局進行約束,例如幫助達到時序要求,或者在設計的不同區域間實現隔離。就此而言,有三種類型的約束很重要:

• BEL –將網表單元放在 slice 中的基本的邏輯元素。

• LOC –將網表的單元放在器件內的一個位置。

• PBlock – 可使用物理(或“P”)block 將邏輯 block 約束到 FPGA 的一個區域。

因此,LOC 允許在器件內定義一個 slice 或其它位置;BEL 約束可用來定義觸發器在 slice 中使用的更精細粒度。當對設計的大面積區域進行分段時,PBlock 可用來將邏輯集合在一起。PBlock 的另一個用途是在執行部分重配置時定義邏輯區域。

有些情況下,您需要將較小的邏輯功能放在一組,以確保時序達到最佳。盡管可以用 PBlock 來實現,但更常見的方法是使用相對放置的宏命令。

相對放置的宏命令(RPM)允許將 DSP、觸發器、LUT 和 RAM 等設計元素在布局中放在一起。

與 PBlock 不同,RPM 不會將這些元素的位置約束在器件的特定區域(除非您想這樣做),而是在布局時將這些元素放在一起。將設計元素放在一起能實現兩個目標。這樣能改善資源效率,讓您能夠精細調節互聯長度,以實現更好的時序性能。

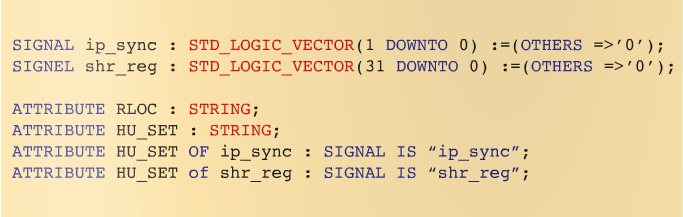

要將設計元素放在一起,可使用三種類型的約束,這些約束用 HDL 源文件進行定義。

• U_SET 可定義一個與層級無關的單元 RPM 集。

• HU_SET 可定義有層級的單元 RPM 集

• RLOC給定義好的SET分配相對位置。

RLOC 約束被定義為 RLOC = XmYm,其中 X 和 Y 與 FPGA 陣列的坐標有關。當定義 RLOC 時,既可以用相對坐標也可以用絕對坐標,取決于您是否添加了 RPM_GRID 屬性。添加這個屬性后,該定義將成為絕對坐標而非相對的。由于這些約束在 HDL 中定義,如圖 4 所示,因此在將約束添加到 HDL 文件之前,通常需要首先運行布局布線設計反復,以便正確定義布局。

圖 4 – 源代碼中的約束

總之,理解時序和布局約束并學習如何正確使用它們,對于在賽靈思可編程邏輯設計中獲得最佳結果質量至關重要。

評論