頻率特性測試儀的設計

頻率特性是一個網絡性能最直觀的反映。頻率特性測試儀用于測量網絡的幅頻特性和相頻特性,是根據掃頻法的測量原理設計,是一種快速、簡便、實時、動態、多參數、直觀的測量儀器,可廣泛應用于電子工程等領域。由于模擬式掃頻儀價格昂貴,不能直接得到相頻特性,更不能打印網絡的頻率響應曲線,給使用帶來諸多不便。為此,設計了低頻段數字式頻率特性測試儀。該測試儀采用數字直接頻率合成技術專用的集成電路AD985l產生掃頻信號,以單片機和FPGA為控制核心,通過A/D和D/A轉換器等接口電路,實現掃頻信號頻率的步進調整、數字顯示及被測網絡幅頻特性與相頻特性的數顯等。該系統成本低廉,掃頻范圍較寬(10 Hz~1MHz),可方便地與打印機連接,實現頻率特性曲線的打印。

2 多功能計數器設計方案

2.1 幅頻和相頻特性測量方案

方案1:利用公式H(s)=R(s)/E(s),以沖擊函數為激勵,則輸出信號的拉氏變換與系統函數相等。但是產生性能很好的沖擊函數比較困難,需要對采集的數據做FFT變換,需要占用大量的硬件和軟件資源,且精度也受到限制。

方案2:掃頻測試法。當系統在正弦信號的激勵下,穩態時,響應信號與輸入激勵信號頻率相同,其幅值比即為該頻率的幅頻響應值,而兩者的相位差即為相頻特性值。采用頻率逐點步進的測試方法。無需對信號進行時域與頻域的變換計算,通過對模擬量的測量與計算完成,且精度較高。

綜上所述,選擇方案2。

2.2 掃描信號產生方案

方案1:采用單片函數發生器。其頻率可由外圍電路控制。產生的信號頻率穩定度低,抗干擾能力差,靈活性差。

方案2:采用數字鎖相環頻率合成技術。但鎖相環本身是一個惰性環節,頻率轉換時間長,整個測試儀的反應速度就會很慢,而且帶寬不高。

方案3:采用數字直接頻率合成技術(DDFS)。以單片機和FPGA為控制核心,通過相位累加器的輸出尋址波形存儲器中的數據,以產生固定頻率的正弦信號。該方案實現簡單,頻率穩定,抗干擾能力強。

綜上分析,采用方案3。

2.3 幅度檢測方案

方案1:采用二極管峰值檢測電路。但是二極管的導通壓降會帶來較大誤差,小信號測量精度不高,而且模擬電路易受到外部的影響,穩定性不高。

方案2:采用真有效值檢測器件。該方法電路簡單,精度高,穩定性高。

綜上所述,采用方案2。

2.4 相位檢測方案

方案1:相位電壓轉換法。采用低通濾波法和積分法。低通濾波法的濾波環節和精度不高;積分法精度較高,但是對積分電路和放電回路的要求很高。

方案2:計數法。兩路信號經整形異或后,所得的脈沖占空比能反映相位差的大小,由此測得其相位差。采用多周期同步計數法,可使量化誤差大大減小,精度很高。

綜上所述,選取方案2。

3 系統總體設計

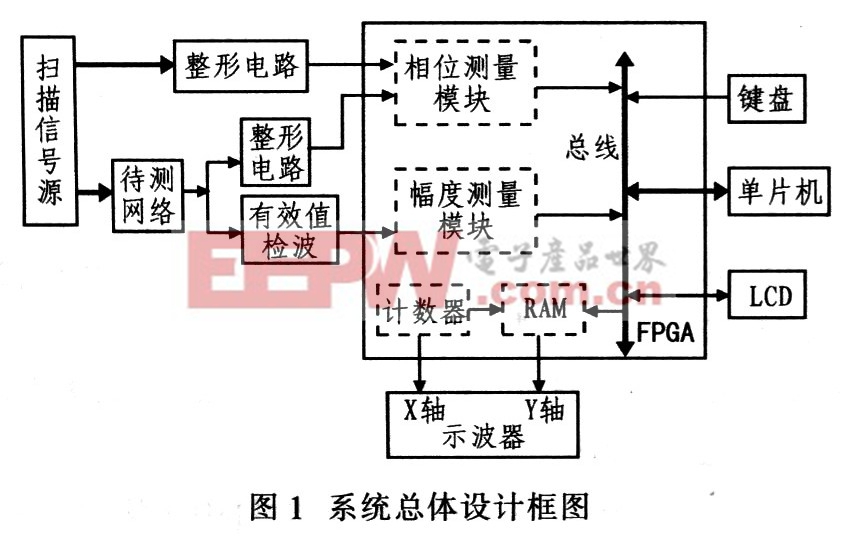

該系統以單片機和FPGA為控制核心,用DDFS技術產生頻率掃描信號,采用真有效值檢測器件AD637測量信號幅度。在FPGA中,采用高頻脈沖計數的方法測量相位差,經過單片機運算,可得到100 Hz~100 kHz中任意頻率的幅頻特性和相頻特性數據,實現在該頻段的自動掃描,并在示波器上同時顯示幅頻和相頻特性曲線。用鍵盤控制系統實現各種功能,并且在LCD同步顯示相應的功能和數據,人機交互界面友好。圖1給出系統總體設計框圖。

4 理論分析與計算

4.1 掃頻測試法理論依據

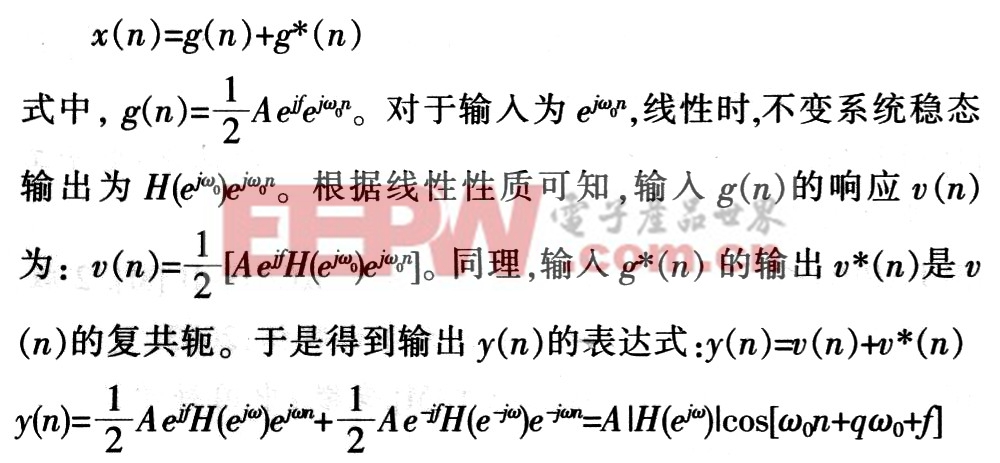

設頻率響應為H(jω)的實系數線性時,不變系統在信號x(n)_Acos(ω0n+f)激勵下的穩態輸出為y(n)。利用三角恒等式,可將輸入表示為2個復指數函數之和:

因此,輸出信號和輸入信號是頻率相同的正弦波,僅有兩點不同:第一,振幅被|H(ejω)|加權,即網絡系統在ω=ω0的幅度函數值;第二,輸出信號相對于輸入信號有一個數量為q(ω0)的相位時延,即網絡系統在ω=ω0的相位值。

4.2 DDS信號源

根據DDFS原理所產生的波形頻率為:

![]()

式中fclk為基準頻率,M為相位增量因子,N為累加器的位數。M取22,N取24。

為得到100 kHz的信號,而且在每個周期希望取到32個以上點,則累加器輸出后級D/A轉換需要至少3.2 MHz的速度,于是選取建立時間為30 ns、10位的DAC900,不僅滿足了對D/A轉換速度的要求,而且具有10位數據線,減少了D/A轉換中固有的量化誤差。fclk取40MHz,頻率的最小步進:

![]()

評論