測試3G手機的DigRF技術

DigRF 3G支持數(shù)字傳輸下的三種時序模式,具體取決于被傳輸RF信息的類型(表1)。DigRF標準還支持三種公共的輸入基準時鐘頻率(19.0 MHz、26.0 MHz和38.4 MHz);時鐘通過SysClk信號送至基帶。與速度模式無關,DigRF處理器會用一個本地的FIFO緩沖管理數(shù)據(jù)流,當傳輸幀時會產(chǎn)生一個無法預測的時序。

生產(chǎn)測試的挑戰(zhàn)

對采用DigRF協(xié)議器件作成功測試的關鍵是要找到一種方式,能在RF接收測試期間管控RxData包的不確定性狀態(tài)。在對DigRF產(chǎn)品作RF接收測試期間,能觀察到RxData信號合成狀態(tài)的多級不確定性:

相位時序;

幀時序;

幀類型;

有效載荷中的數(shù)據(jù)。

312 Mbps的數(shù)據(jù)速率來自于一個1248 MHz主時鐘(一般由PLL生成)的1/4分頻器。在生產(chǎn)性測試系統(tǒng)中,考慮到影響RF前端的相位噪聲性能的重要性,器件的時鐘輸入應由RF儀器提供。與普通數(shù)字子系統(tǒng)相比較,這個時鐘源的起始相位通常是不可控的。DUT(待測設備)的輸入時鐘相位未定,PLL倍頻器/分頻器產(chǎn)生的相位也不確定,兩者結(jié)合導致RxData輸出時序無法預測,包括器件各上電循環(huán)之間,以及多地點并行測試配置中的不同器件之間的輸出時序。

一種生產(chǎn)型測試儀應有這種能力,即在各次測試間對測試儀硬件和DUT作必要修改時,仍保持數(shù)字子系統(tǒng)的運行。它使測試儀能夠維持相對于DUT輸出的選通時序,避免在正式運行中的選通相位重調(diào),節(jié)省了測試時間。

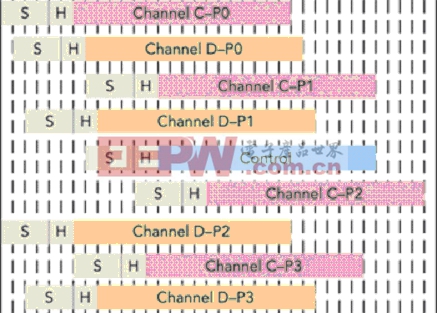

下一個重要的測試挑戰(zhàn)是尋找一個能處理多級不確定性數(shù)據(jù)包傳輸性能的方式。如圖3所示,在DUT的每個RF接收測試期間,測試儀都不知道每個包會在哪個測試循環(huán)中傳輸,包的類型會是什么,或者包的類型是否符合預期(例如,RFIC會生成一個主動的控制狀態(tài)消息)。

圖 3. 由于數(shù)據(jù)包的不確定性,在一款器件的每次RF接收測試期間,測試儀不知道每個包會在哪個測試循環(huán)中傳輸,包的類型是什么,或者包的類型是否符合預期。

馬上能看出,測試程序不能在數(shù)字測試模式中采用固定循環(huán)周期的選通隔離所需I/Q數(shù)據(jù)。同樣,對同步或頭的數(shù)字匹配回路不能以DigRF速度,足夠快地通過ATE儀器的流水線,儀器也不能完成對頭信息的實時識別和決策。

ATE策略的比較

傳統(tǒng)生產(chǎn)測試系統(tǒng)有靜態(tài)的選通時序以及簡單的比較功能(例如H、L、X、M、V、存儲),因此它們自身并不具備強大的校準能力,以應對DigRF器件需要的非確定性。不過,這類測試儀中的數(shù)字儀器有所需要的數(shù)字捕捉能力,一般用于ADC(模數(shù)轉(zhuǎn)換器)輸出數(shù)據(jù)或DUT寄存器讀取操作。因此,你可以保留在這臺儀器上的投資,并且采用一種批量捕捉和后處理技術(block-capture-and-post-processing)應對DigRF的RF接收測試挑戰(zhàn)。

對于RF接收測試,一般CW(連續(xù)波)測試需要1kB至4kB的I/Q采樣,而日益普遍的采用調(diào)制波形的系統(tǒng)級測試則使用16 kB至32 kB的I/Q采樣。注意轉(zhuǎn)換為實際的串行位:

1k I/Q = 1024 [8 bits (I) + 8 bits (Q)] 協(xié)議_開銷 = 串行位數(shù)

為了解決實時情況下的非確定性行為,測試儀必須提供專為DigRF 3G DUT與數(shù)字捕捉之間編碼的數(shù)字邏輯。其目標是在數(shù)據(jù)到達測試儀的DSP(數(shù)字信號處理器)前,減輕捕捉時所出現(xiàn)的所有時序與數(shù)據(jù)不確定性問題。

一種測試選擇是在DIB(器件接口板)上設計一個FPGA(現(xiàn)場可編程門陣列)電路。這種方法可以用一片廉價器件提供定制邏輯,但也有三個麻煩:

評論