高精度數(shù)字信號中和器的設(shè)計(jì)與實(shí)現(xiàn)

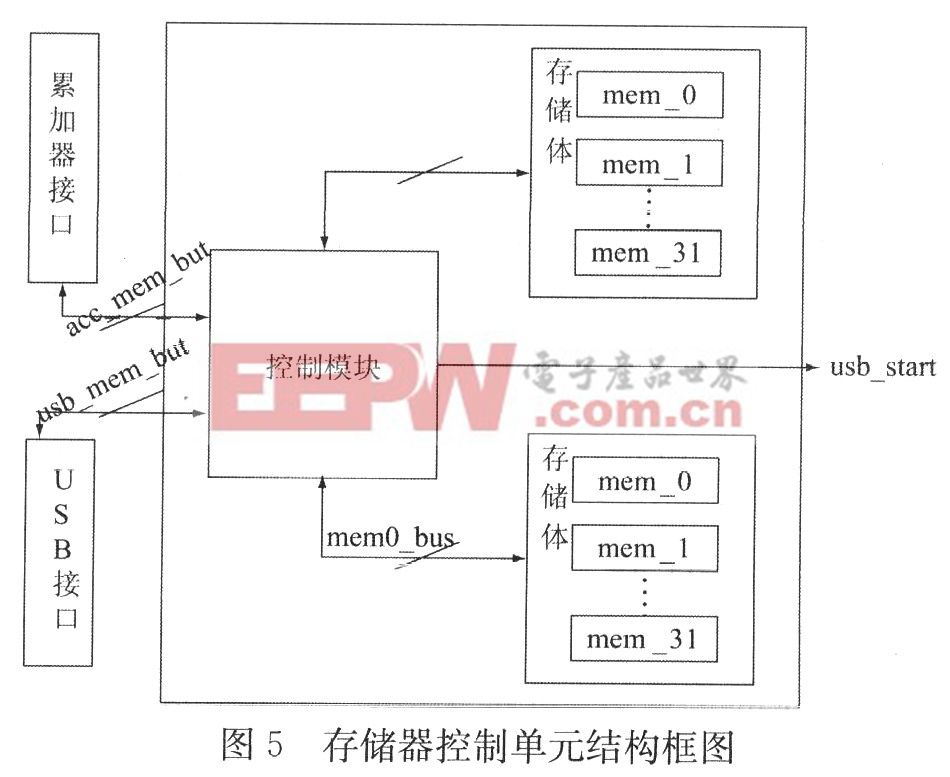

3.3 存儲(chǔ)器控制單元

圖5所示為存儲(chǔ)器算法流程。存儲(chǔ)器控制單元內(nèi)部包含了兩個(gè)存儲(chǔ)體。任一時(shí)刻,兩個(gè)存儲(chǔ)體分別由累加器單元控制,實(shí)現(xiàn)數(shù)據(jù)累加;或由USB控制單元控制,將存儲(chǔ)體中的數(shù)據(jù)傳輸至上位機(jī)。由存儲(chǔ)器控制單元進(jìn)行控制,兩個(gè)存儲(chǔ)器進(jìn)行乒乓操作,每秒進(jìn)行一次切換,即每秒完成一濃累加循環(huán)。

3.4 USB控制單元

USB控制單元在每完成一秒的數(shù)據(jù)累加后,啟動(dòng)一次數(shù)據(jù)傳輸,數(shù)據(jù)傳輸就是由USB控制單元讀取存儲(chǔ)體中的計(jì)算結(jié)果,將結(jié)果寫入U(xiǎn)SB控制器中。并在讀取存儲(chǔ)體中數(shù)據(jù)的同時(shí),將存儲(chǔ)體中的數(shù)據(jù)清0,為下一次數(shù)據(jù)累加做準(zhǔn)備。

4 測試結(jié)果

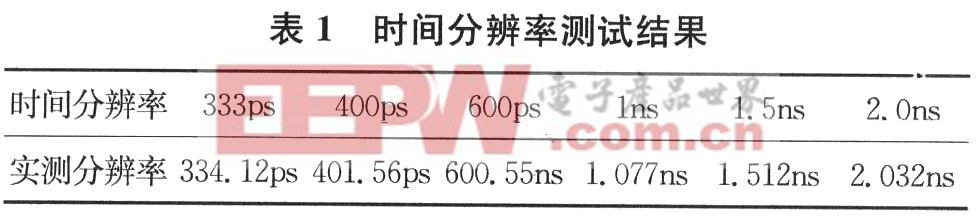

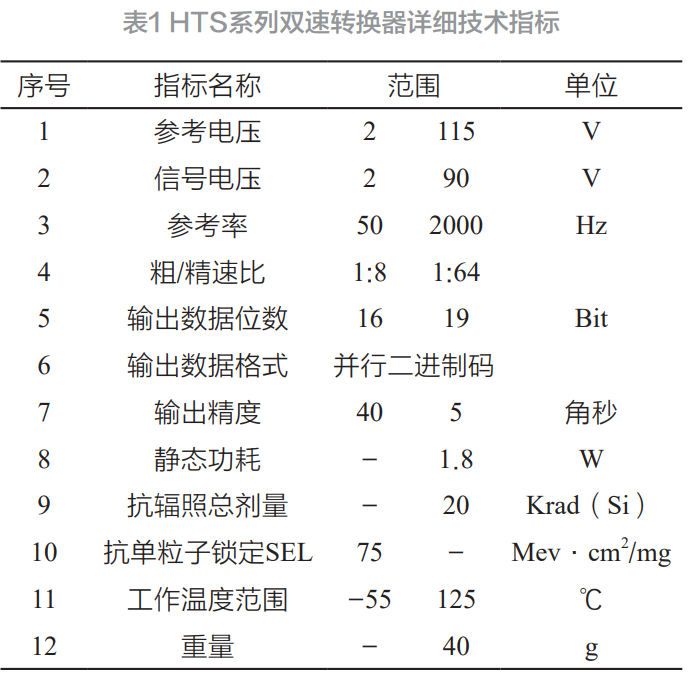

本設(shè)計(jì)中射頻采集部分的采樣時(shí)鐘為1.5GHz,故在交錯(cuò)采樣模式下,ADC的采樣率為3GSPS。因而ADC的采樣間隔為1/3GSPS=333ps,即時(shí)間間隔大于333ps的信號即可為系統(tǒng)所分辨,測量。實(shí)際測試中采用延遲線測量法進(jìn)行時(shí)間分辨率的測試。時(shí)間分辨率測試數(shù)據(jù)如表1所示。

設(shè)計(jì)中采用FPGA內(nèi)部的BlockRAM作為存儲(chǔ)累加單元,限于BlockRAM的容量和硬件算法的設(shè)計(jì),本系統(tǒng)的測量時(shí)間范圍為0~20us,即在一個(gè)測量周期內(nèi)只測量觸發(fā)信號后20us內(nèi)的信號。

5 結(jié)束語

根據(jù)飛行時(shí)間質(zhì)譜儀器的應(yīng)用背景,本文提出了一種基于超高速模數(shù)轉(zhuǎn)換技術(shù)的高精度數(shù)字信號中和器的設(shè)計(jì)與實(shí)現(xiàn)方案,經(jīng)實(shí)際制作與調(diào)試,本設(shè)計(jì)達(dá)到了預(yù)期的設(shè)計(jì)目標(biāo),時(shí)間測量范圍為0~20us,實(shí)際測試最小時(shí)間分辨率為334ps,線性度良好。目前,該數(shù)字信號中和器已應(yīng)用于飛行時(shí)問質(zhì)譜儀器的相關(guān)實(shí)驗(yàn)中。今后的重點(diǎn)將針對檢測動(dòng)態(tài)范圍、最小時(shí)間分辨率和靈敏度等主要參數(shù)進(jìn)一步進(jìn)行優(yōu)化。

評論