高精度數字信號中和器的設計與實現

觸發通道和外時鐘輸入通道的信號調理模塊主要由雙向緩沖器及電平轉換芯片組成,不再贅述。

2.2 射頻采集模塊

在本系統的應用背景中,輸入脈沖信號的最小時間間隔為400ps,故要求射頻采集模塊的采樣間隔小于400ps。設計中采用國家半導體公司的模數轉換器ADC08D1500來構建射頻采集模塊,ADC08D1500為8bit雙通道超高速模數轉換器:在單邊沿采樣模式下,最高采樣率為1.5GSPS;在雙邊沿采樣(交錯采樣)模式下,最高采樣率為3GSPS,即時間分辨率為333ps,滿足設計要求。

2.3 高速時鐘產生模塊

為保證測量脈沖時間間隔的精度,射頻采集模塊需要一個高時間穩定度、最高頻率為1.5GHz的轉換時鐘。為此,TDC選用集成鎖相環芯片AD9517-4來產生時鐘信號。AD9517-4是一個集成PLL頻率合成器與時鐘分配器,時鐘穩定度20ppm。在本系統中AD9517-4的輸出頻率調節范圍為500MHz~1.5GHz,對應系統時間分辨率為333ps~2ns可調。

2.4 USB2.0模塊

為了降低數字信號中和器對PC硬件配置的要求和數字信號中和器本身的便攜性,設計中采用USB2.0接口來實現數字信號中和器與PC問的數據傳輸。在氣體檢測的應用中,飛行時間質譜儀器中的離子飛行時間較短,每秒采樣的數據量較少(為幾十KHz),而利用集成USB2.0控制芯片CY7C68013可實現最高為48Mbyte/s的數據傳輸速度,故可以滿足傳輸速度的要求。

3 基于FPGA的數據處理

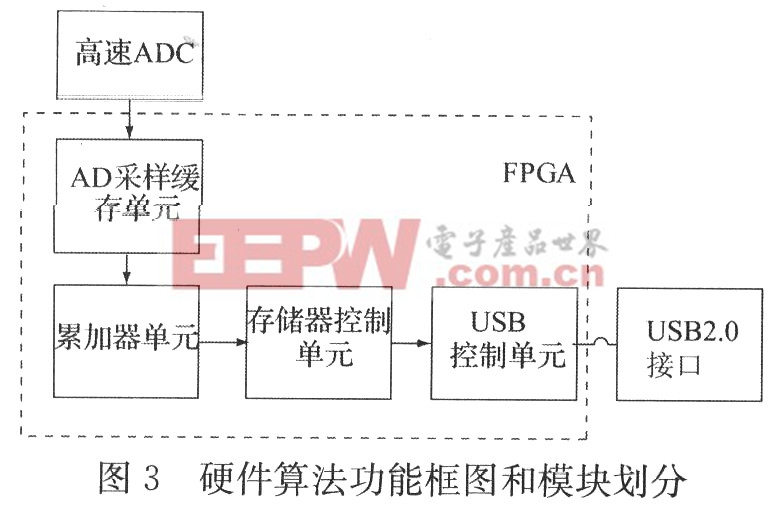

圖3所示為數字信號中和器的FPGA硬件算法設計框圖。設計中將硬件程序劃分為AD采樣緩存單元、累加器單元、存儲器控制單元、USB控制單元。

3.1 A/D采樣緩存單元

A/D采樣緩存單元控制外部A/D芯片,并實現內部定時,每50us啟動一次數據采集,每次數據采集持續時間20μs。并將采樣數據存放在一深度為4的緩存中,緩存中的數據由累加器單元進行后續處理。

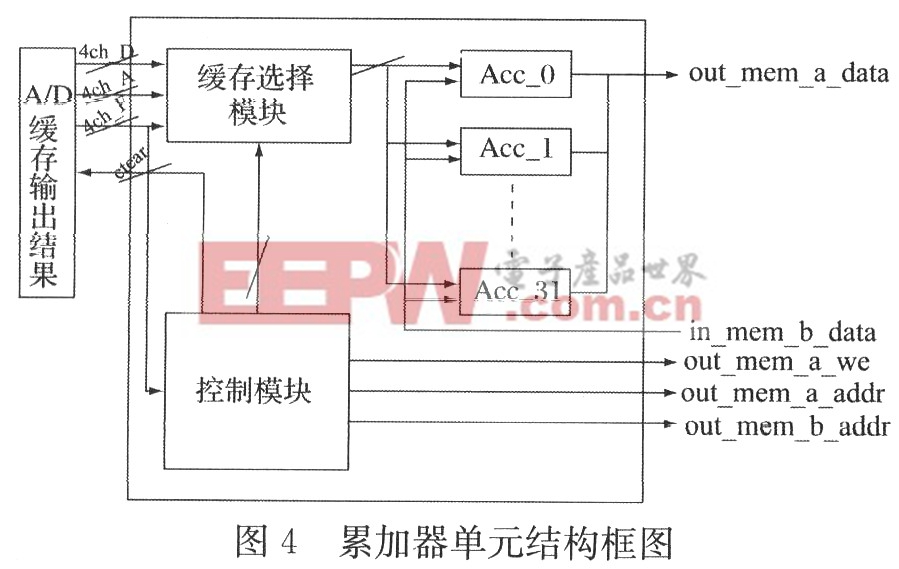

3.2 累加器單元

圖4所示為累加器算法流程。當A/D采樣緩存單元中的緩存有數據時,讀取緩存中數據,一次讀取32個采樣點,將采樣結果和存儲器中對應地址的數據相加,并將累加再次寫入存儲器中的對應地址。

評論